1

/Chapter4

N i dung môn h cộ ọ

N i dung môn h cộ ọ

1. Gi i thi u chung v h vi x lýớ ệ ề ệ ử

2. B vi x lý Intel 8088/8086ộ ử

3. L p trình h p ng cho 8086ậ ợ ữ

4. T ch c vào ra d li uổ ứ ữ ệ

5. Ng t và x lý ng tắ ử ắ

6. Truy c p b nh tr c ti p DMAậ ộ ớ ự ế

7. Các b vi x lý trên th c tộ ử ự ế

2

/Chapter4

Ch ng 4: T ch c vào ra d li uươ ổ ứ ữ ệ

Ch ng 4: T ch c vào ra d li uươ ổ ứ ữ ệ

•Các tín hi u c a 8086 và các m ch ph tr 8284, 8288ệ ủ ạ ụ ợ

•Ghép n i 8088 v i b nhố ớ ộ ớ

•Ghép n i 8086 v i b nhố ớ ộ ớ

•Ghép n i v i thi t b ngo i viố ớ ế ị ạ

3

/Chapter4

Ch ng 4: T ch c vào ra d li uươ ổ ứ ữ ệ

Ch ng 4: T ch c vào ra d li uươ ổ ứ ữ ệ

•Các tín hi u c a 8086 và các m ch ph tr 8284, 8288ệ ủ ạ ụ ợ

Các tín hi u c a 8086ệ ủ

Phân kênh và vi c đ m cho các busệ ệ

M ch t o xung nh p 8284 và m ch đi u khi n bus 8288ạ ạ ị ạ ề ể

Bi u đ th i gian c a các l nh ghi/đ cể ồ ờ ủ ệ ọ

•Ghép n i 8088 v i b nhố ớ ộ ớ

•Ghép n i 8086 v i b nhố ớ ộ ớ

•Ghép n i v i thi t b ngo i viố ớ ế ị ạ

4

/Chapter4

Ch ng 4: T ch c vào ra d li uươ ổ ứ ữ ệ

Ch ng 4: T ch c vào ra d li uươ ổ ứ ữ ệ

•Các tín hi u c a 8086 và các m ch ph tr 8284, 8288ệ ủ ạ ụ ợ

Các tín hi u c a 8086ệ ủ

Phân kênh và vi c đ m cho các busệ ệ

M ch t o xung nh p 8284 và m ch đi u khi n bus 8288ạ ạ ị ạ ề ể

Bi u đ th i gian c a các l nh ghi/đ cể ồ ờ ủ ệ ọ

•Ghép n i 8088 v i b nhố ớ ộ ớ

•Ghép n i 8086 v i b nhố ớ ộ ớ

•Ghép n i v i thi t b ngo i viố ớ ế ị ạ

5

/Chapter4

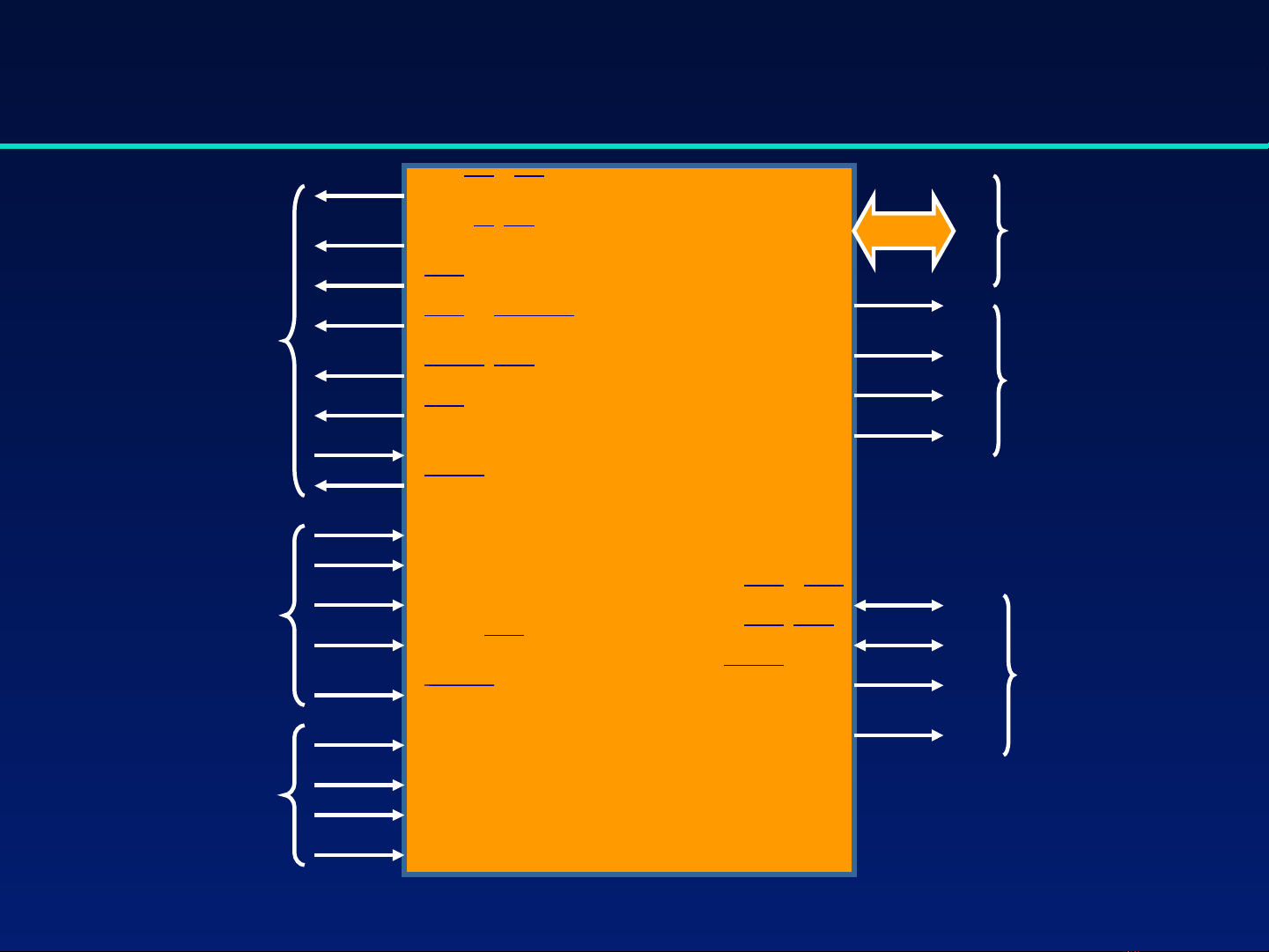

Các chân tín hi u c a 8086ệ ủ

Các chân tín hi u c a 8086ệ ủ

8086

AD0-AD15

A16/S3

A17/S4

A19/S6

A18/S5

BHE/S7

READY

HOLD(RQ/GT0)

INTA(QS1)

ALE(QS0)

HLDA(RQ/GT1)HLDA(RQ/GT1)

M/IO (S2)

DT/R(S1)

WR (LOCK)

RD

DEN (S0)

SS0

NMI

INTR

MN/MX

RESET

TEST

CLK

Vcc

GND

GND

16 đ ng ườ

đ a ch th p/d li uị ỉ ấ ữ ệ

4 đ ng ườ

bus C/ đ a ch caoị ỉ

Tín hi u đi uệ ề

khi n busể

Tín hi u đi uệ ề

khi n h th ngể ệ ố

Tín hi u đi u khi nệ ề ể

CPU

đ ng hồ ồ

và ngu nồ

![Bài giảng Kiến trúc máy tính: Chương 1 - Giới thiệu tổng quan [chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250729/kimphuong1001/135x160/47331753774510.jpg)