LUAÄN VAÊN TOÁT NGHIEÄP GVHD : TRAÀN VAÊN TROÏNG

ÖÙng duïng vi maïch soá laäp trình Trang 30

nhöõng tín hieäu ôû ngoõ vaøo vaø nhöõng tín hieäu naøy ñöôïc ñöa tôùi maûng AND. Ngoaøi

ra vi maïch coøn ñöôïc thieát keá moät maûng boå sung (maûng buø). Ñaây laø toång soá haïng

buø vaø ñöôïc thöïc hieän nhö moät ngoû vaøo cuûa maûng AND, noù cho pheùp boå sung

theâm nhieàu toå hôïp.

4. HoÏ vi maïch FPGA ( Field Progammable Gate Array).

Hoï FPGA ñöôïc Signetics giôùi thieäu vaøo naêm 1977 ñöôïc söû duïng ñeå thay theá

cho nhöõng coång nhieàu ngoõ vaøo tieâu chuaån, caáu truùc cuûa noù bao goàm moät maûng

AND laäp trình, vôùi laäp trình cöïc tính ôû ngoõ ra. Chæ vôùi moät coång AND coù theå

bieán ñoåi thaønh coång NAND, NOR hay coång OR. Moãi coång AND trong FPGA coù

theå bieán ñoåi thaønh caùc coång logic khaùc nhau.

FPGA cuõng ñöôïc boå sung linh ñoäng hôn nhöõng coång tieâu chuaån khaùc. Vi

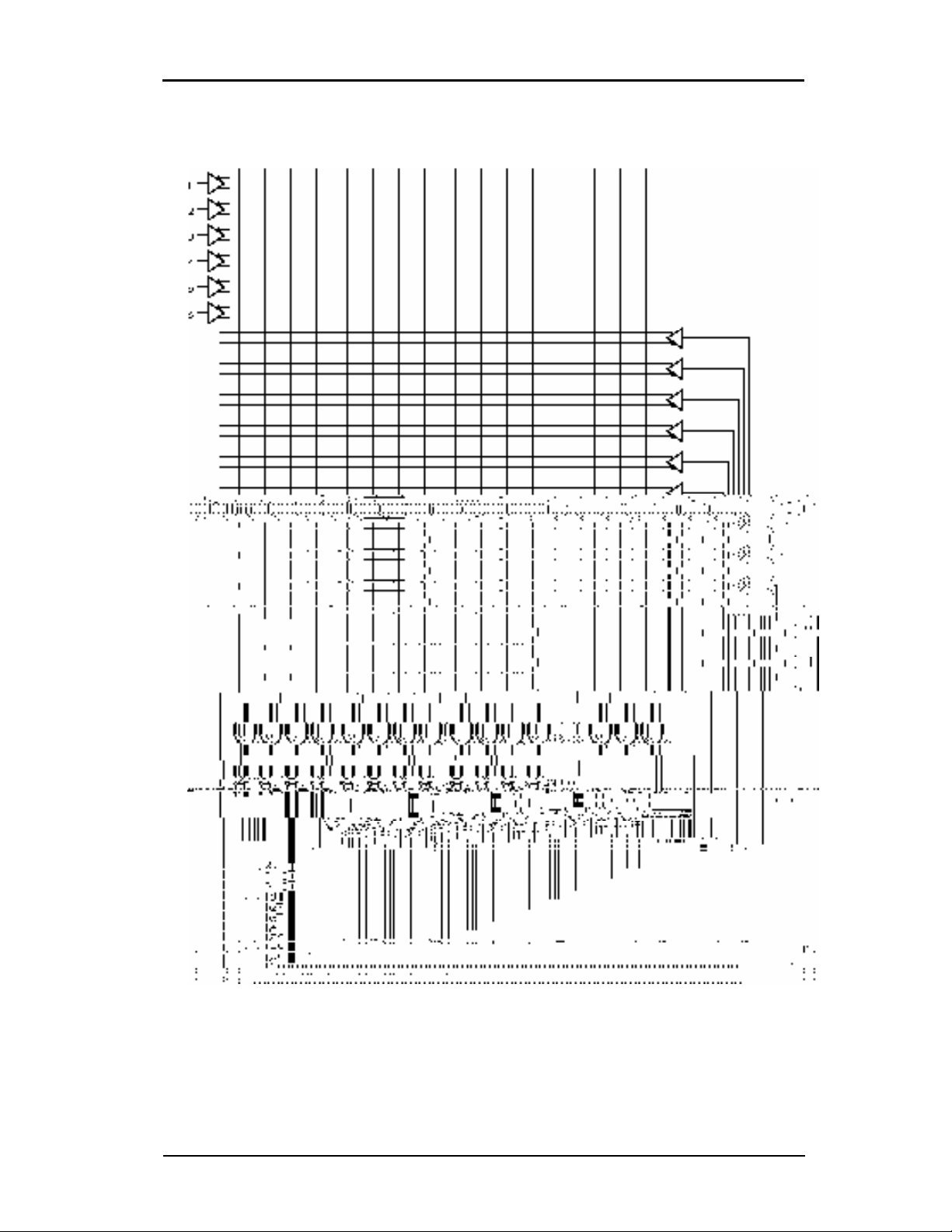

maïch ñaïi dieän cho hoï FPGA laø PLS151, coù hình daùng 20 chaân ñöôïc trình baøy ôû

hình 3.6. PLS151 coù 6 ngoû vaøo, 12 ngoõ ra vaø coù tín hieäu hoài tieáp ñöa veà maûng

AND ñöôïc söû duïng nhö nhöõng ngoõ vaøo. Coù theâm 3 tích soá ñöôïc taïo ra bôûi 3

ñöôøng ñieàu khieån, caùc tín hieäu naøy ñieàu khieån nhöõng coång ñeäm ngoû ra 3 traïng

thaùi. FPGA thích hôïp trong caùc thieát keá ñeå giaûi maõ ñòa chæ vaø ñöôïc theâm vaøo

caùc chöùc naêng khaùc.

5. HoÏ vi maïch PAL ( Programmable Array Logic).

PAL laø moät hoï phoå bieán nhaát trong hoï PLD ñöôïc MONOLITHIC

MEMORIES INC giôùi thieäu vaøo naêm 1978. PAL ñöôïc ñaêng kyù baûn quyeàn veà

caáu truùc cuûa coâng ty MMI. Caáu truùc cuûa PAL bao goàm moät maûng AND laäp trình

theo sau laø moät maûng OR coá ñònh, caáu truùc naøy ñöôïc caûi tieán töø nhöõng khuyeát

ñieåm cuûa hoï FPLA. Hình 3.7 minh hoïa cho caáu truùc ñôn giaûn cuûa PAL. Do doaïi

boû vieäc söû duïng caàu chì ôû maûng OR, do ñoù soá löôïng tinh theå Silicon ñöôïc söû

duïng giaûm, daãn ñeán giaù thaønh cuûa PAL thaáp hôn so vôùi FPLA. Maët khaùc thôøi

gian trì hoaõn cuûa PAL ngaén hôn so vôùi FPLA do giaûm ñöôïc söï trì hoaõn khi

truyeàn qua maûng OR.

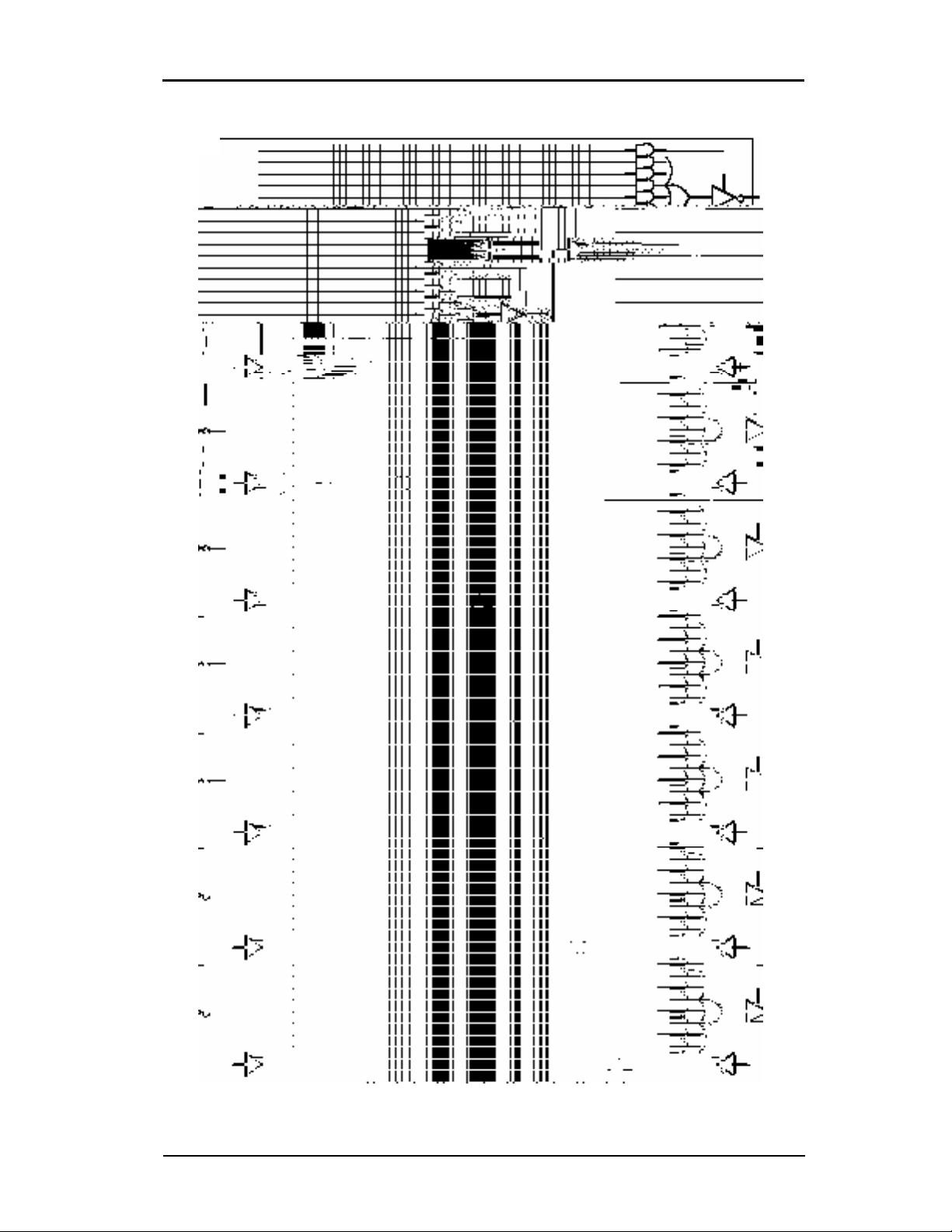

Khaûo saùt PAL16L8 coù hình daùng 20 chaân sô ñoà logic ñöôïc trình baøy ôû hình

3.8. Vi maïch naøy coù 8 toå hôïp ngoõ ra, moãi ngoõ ra ñöôïc ñaûo vôùi 7 tích soá cuûa ngoõ

vaøo, 6 trong 8 ngoõ ra ñöôïc hoài tieáp veà maûng AND, cho pheùp nhöõng chaân naøy

ñöôïc söû duïng vôùi chöùc naêng I/O. Do PAL16L8 coù ngoõ ra taùc ñoäng ôû möùc thaáp

neân noù coù theå keát hôïp vôùi caùc IC khaùc cuøng moät möùc taùc ñoäng.

LUAÄN VAÊN TOÁT NGHIEÄP GVHD : TRAÀN VAÊN TROÏNG

ÖÙng duïng vi maïch soá laäp trình Trang 31

Hình 3.6 . Sô ñoà logic cuûa FPGA PLS151

LUAÄN VAÊN TOÁT NGHIEÄP GVHD : TRAÀN VAÊN TROÏNG

ÖÙng duïng vi maïch soá laäp trình Trang 32

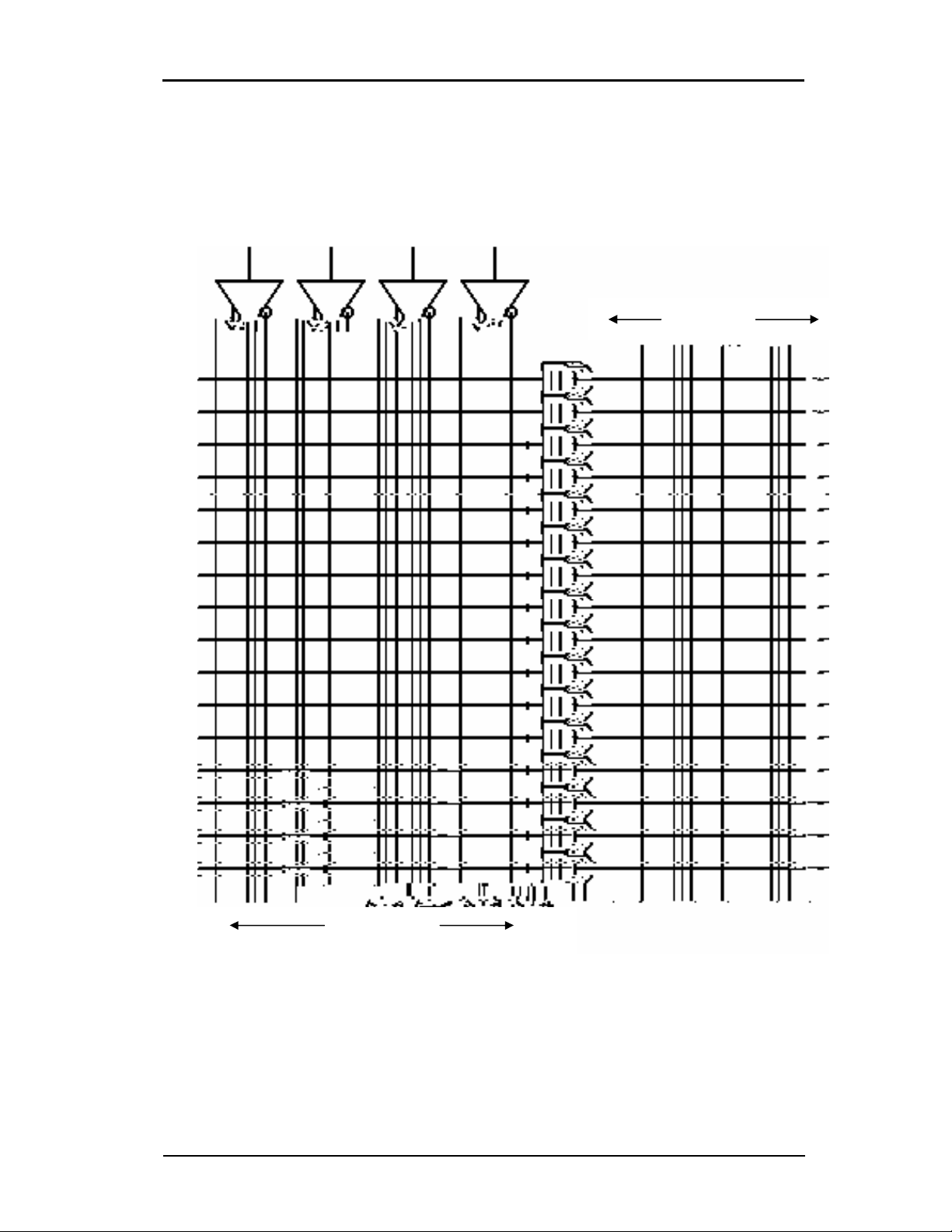

I3 I2 I1 I0

O3 O2 O1

O0

Hình 3.7 . Sô ñoà logic cuûa PAL

Maûng OR

Maûng AND

LUAÄN VAÊN TOÁT NGHIEÄP GVHD : TRAÀN VAÊN TROÏNG

ÖÙng duïng vi maïch soá laäp trình Trang 33

Hình 3.8. Sô ñoà logic cuûa PAL16L8

19

17

1

2

3

4

5

6

7

8

9

18

16

15

14

13

12

11

LUAÄN VAÊN TOÁT NGHIEÄP GVHD : TRAÀN VAÊN TROÏNG

ÖÙng duïng vi maïch soá laäp trình Trang 34

PAL16L8 ñöôïc öùng duïng trong lónh vöïc giaûi maõ ñòa chæ, noù thuaän tieän trong

vieäc keát hôïp vôùi caùc boä vi xöû lyù vaø thieát bò ngoaïi vi vì cuøng moät möùc taùc ñoäng.

Vôùi nhöõng ñaëc tính nhö toác ñoä töông ñoái cao, giaù thaønh thaáp, thôøi gian truyeàn trì

hoaõn khoaûng 7,5ns neân PAL16L8 raát phoå bieán trong coâng nghieäp PLD. Ngoaøi ra

PAL16L8 coù moät ñaëc ñieåm môùi so vôùi caùc hoï tröôùc laø coù caàu chì baûo veä, noù

duøng ñeå choáng söï sao cheùp, giuùp baûo veä noäi dung beân trong. Ngoaøi PAL16L8

coâng ty MMI coøn giôùi thieäu caùc loaïi vi maïch khaùc nhö PAL16R4, PAL16R6,

PAL16R8. Caùc vi maïch naøy coù caáu taïo gioáng nhö PAL16L8 nhöng ôû ngoõ ra söû

duïng theâm caùc FF D ñeå choát tín hieäu ngoû ra.

Moät theá heä vi maïch PAL ñöôïc coâng ty AMD giôùi thieäu laø PAL22V10 vôùi

hình daùng 24 chaân ñöôïc cheá taïo baèng coâng ngheä CMOS thay theá cho coâng ngheä

löôõng cöïc. Ñaëc tröng cuûa vi maïch naøy laø ôû ngoû ra ñöôïc cho qua coång PLD.

Ngoaøi vieäc taêng soá bieán ngoû vaøo vi maïch naøy coøn coù moät soá ñaëc ñieåm nöõa

laø trong haøm logic caùc thaønh phaàn tích soá coù theå thay ñoåi töø 8 ñeán 16 bieán. Ñieàu

naøy seõ giuùp cho vi maïch thöïc hieän nhieàu phöông trình phöùc taïp. Nhôø vaøo caáu

taïo ôû ngoû ra caùc coång PLD neân caùc ngoû ra hoaëc vaøo cuûa vi maïch coù ñaëc tính

giao tieáp 2 chieàu, ñieàu naøy laøm taêng khaû naêng xöû lyù cuûa vi maïch vaø taïo söï

thuaän lôïi cho vieäc thieát keá. Do nhöõng ñaëc ñieåm ñaõ ñöôïc caûi tieán neân caùc theá heä

vi maïch PAL ñöôïc phoå bieán roäng raõi (ñaëc bieät laø nhoùm vi maïch 20 chaân) vaø

PAL ñöôïc xem laø hoï vi maïch ñaïi dieän cho hoï vi maïch soá laäp trình.

Ngoaøi ra caùc coâng ty cheá taïo PAL coù choïn löïa trong vieäc kyù hieäu caùc soá

treân moät vi maïch. Ñieàu naøy cung caáp cho ngöôøi söû duïng nhöõng thoâng tin caàn

thieát coù lieân quan ñeán öùng duïng cuûa vi maïch. Caùc kyù hieäu trong vieäc ñaùnh soá

cuûa hoï PAL noùi chung bao goàm 2 soá ñeám ñöôïc taùch rôøi nhau bôûi 1 hay 2 kyù töï.

Soá ñaàn tieân trong teân vi maïch cho bieát soá ngoõ vaøo cuûa vi maïch (ñaây chính laø soá

bieán ngoõ vaøo cuûa maûng AND). Soá thöù hai bieåu thò soá ngoû ra cuûa vi maïch. Kyù töï

naèm giöõa 2 soá chæ ra yù nghóa caùc thuoäc tính cuûa ngoû ra. Moät soá maõ kyù töï coù yù

nghóa laø:

H taùc ñoäng möùc thaáp.

L taùc ñoäng möùc cao.

P taùc ñoäng ngoû ra coù theå laäp trình.

C phaàn boå sung caùc ngoû ra.

S boä tuaàn töï.

Caùc kyù hieäu cuûa vi maïch hoï PAL ñöôïc xem laø nhöõng höôùng daãn cô

baûn cuûa vi maïch. Ngoaøi ra caùc coâng ty cheá taïo coøn cung caáp baûn thoâng soá kyõ

thuaät vaø sô ñoà logic cuûa vi maïch keøm theo ñeå laøm taøi lieäu tham khaûo cho caùc

nhaø thieát keá.

6. Hoï vi maïch GAL ( Generic Array Logic).

GAL laø moät nhoùm cuûa coâng ngheä EEPLD, noù ñöôïc giôùi thieäu vaø phaùt trieån

bôûi coâng ty Lattice Semiconductor Comp. Coâng ty naøy ñaõ ñöa ra moät khaùi nieäm

veà coång PLD coù kyù hieäu laø OLMCs (Output Logic Macrocells).

![Bài giảng Tổ chức - Cấu trúc Máy tính II Đại học Công nghệ Thông tin (2022) [Mới Nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250515/hoatrongguong03/135x160/8531747304537.jpg)