VHDL for efficient testbenches www.appliedVHDL.com Applied VHDL Training Course, Dr Fearghal Morgan, V2007.1 p1

VHDL for

Efficient Testbenches

using muxAndDecEx1

combinational logic example

Dr Fearghal Morgan

VHDL for efficient testbenches www.appliedVHDL.com Applied VHDL Training Course, Dr Fearghal Morgan, V2007.1 p2

VHDL For Efficient Testbenches (TBs)

Learning outcomes

On completion of this module, you should be able to :

Apply stimulus using

Explicit stimulus application using

single process -- detailed in muxAndDecEx1

multiple processes -- course material

For loop

Array

FileIO

Generate message output during simulation

Presentation also introduces

VHDL functions and their definition in the IEEE VHDL

libraries

VHDL Variables

VHDL for efficient testbenches www.appliedVHDL.com Applied VHDL Training Course, Dr Fearghal Morgan, V2007.1 p3

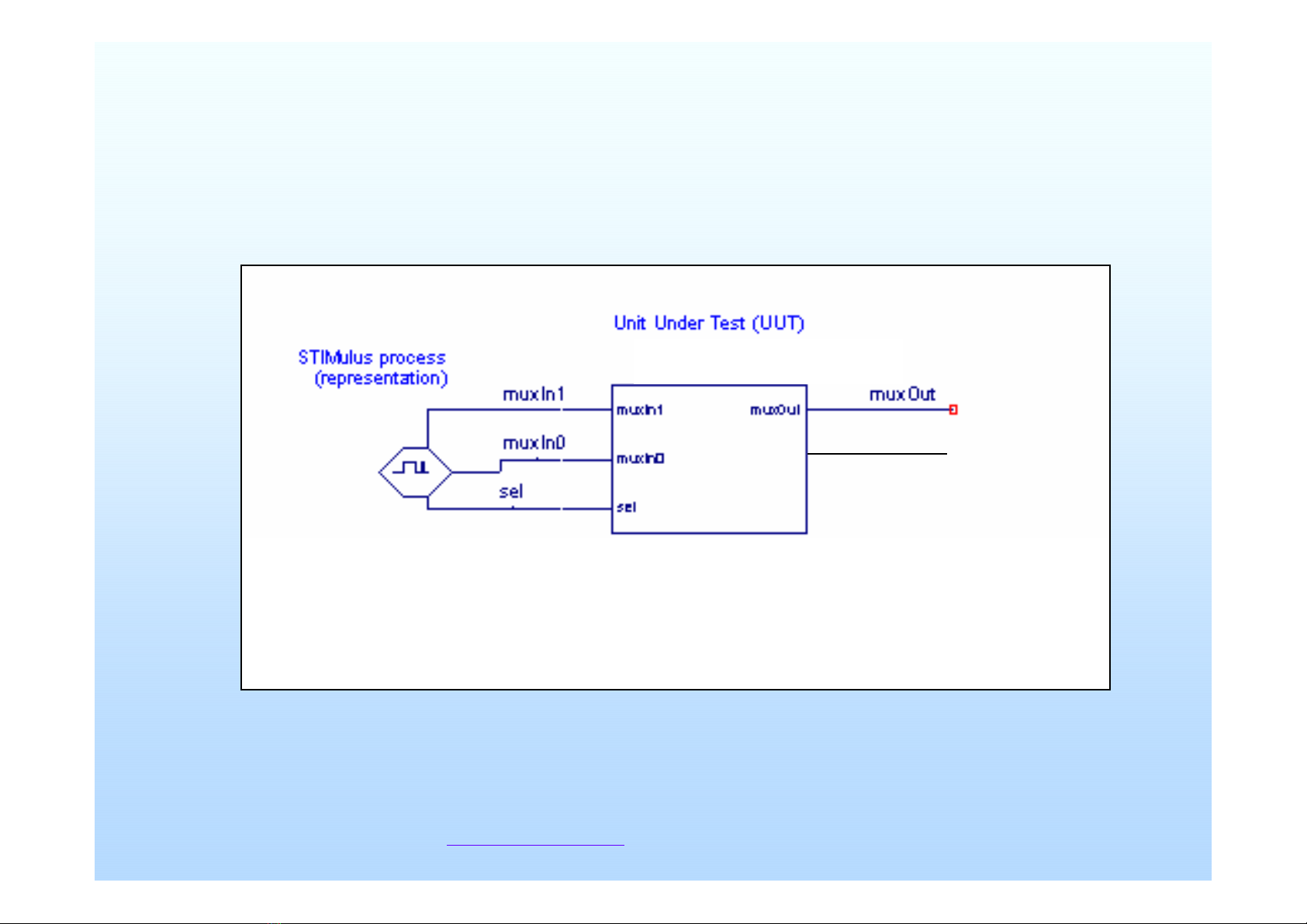

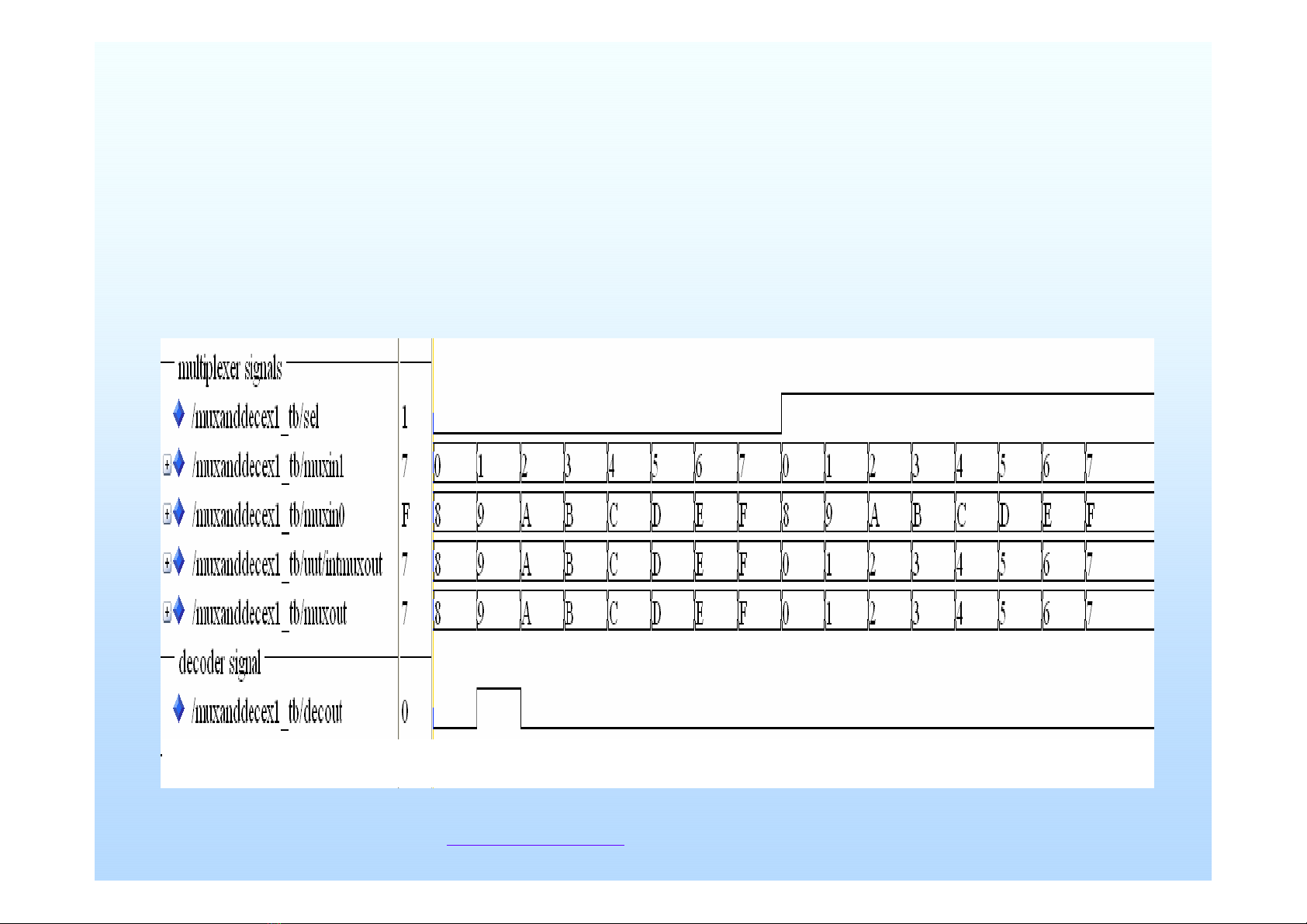

muxAndDecEx1 Testbench & Simulation

Visualise the test bench structure

muxAndDecEx1

decOutdecOut

VHDL for efficient testbenches www.appliedVHDL.com Applied VHDL Training Course, Dr Fearghal Morgan, V2007.1 p4

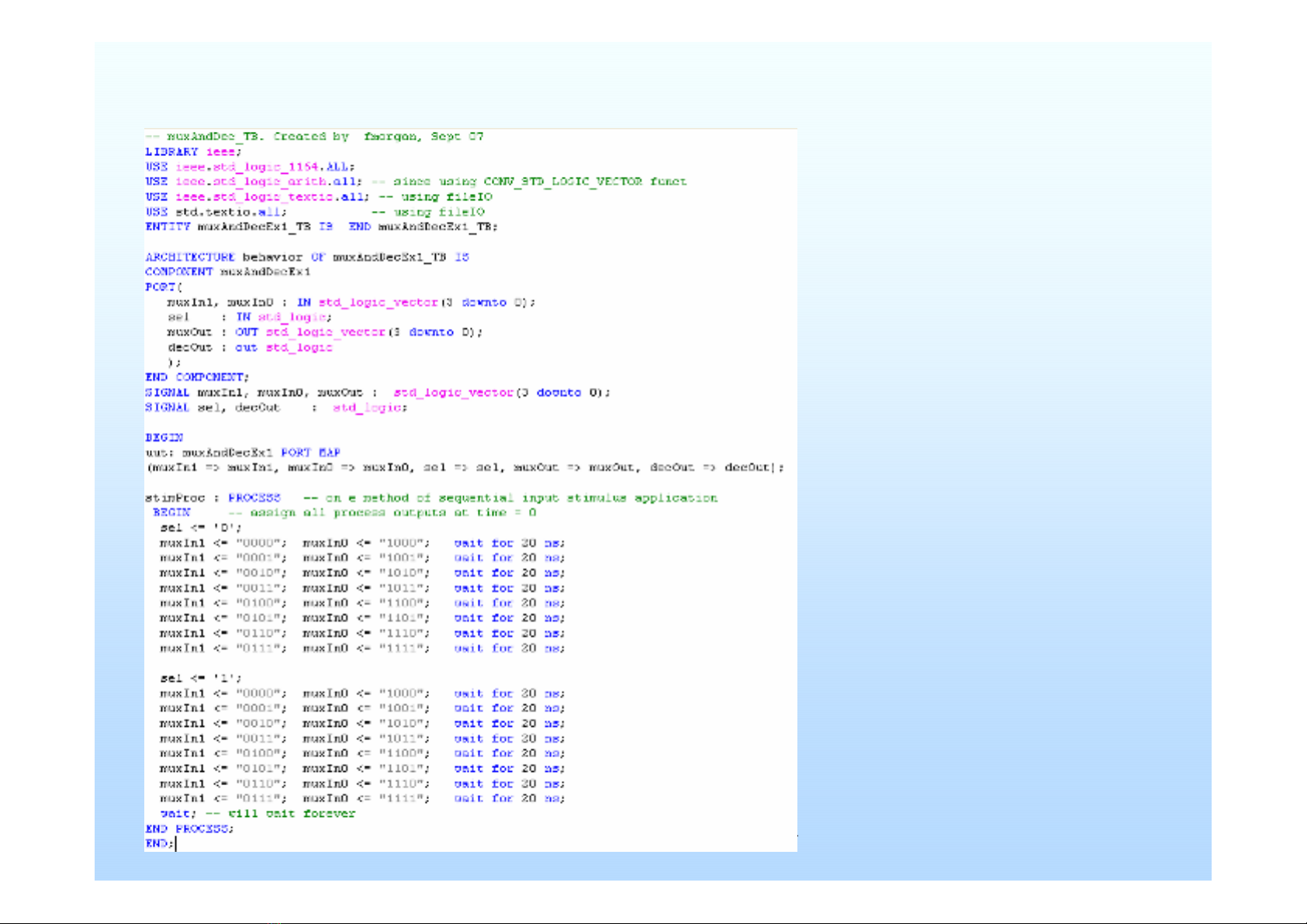

Basic muxAndDecEx1 Testbench

VHDL for efficient testbenches www.appliedVHDL.com Applied VHDL Training Course, Dr Fearghal Morgan, V2007.1 p5

Basic muxAndDecEx1 Testbench

Simulation Waveform

![Bài giảng Tổ chức - Cấu trúc Máy tính II Đại học Công nghệ Thông tin (2022) [Mới Nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250515/hoatrongguong03/135x160/8531747304537.jpg)