ChươngChương 6:6: PHÂN CỰC CHO PHÂN CỰC CHO

TRASISTOR TRƯỜNG FETTRASISTOR TRƯỜNG FET

BỘ GIÁO DỤC VÀO ĐÀO TẠO

ĐH Sư Phạm Kỹ Thuật TP.HCM

KHOA ĐIỆN –ĐIỆN TỬ

Bộ Môn Cơ Sở Kỹ Thuật Điện

2

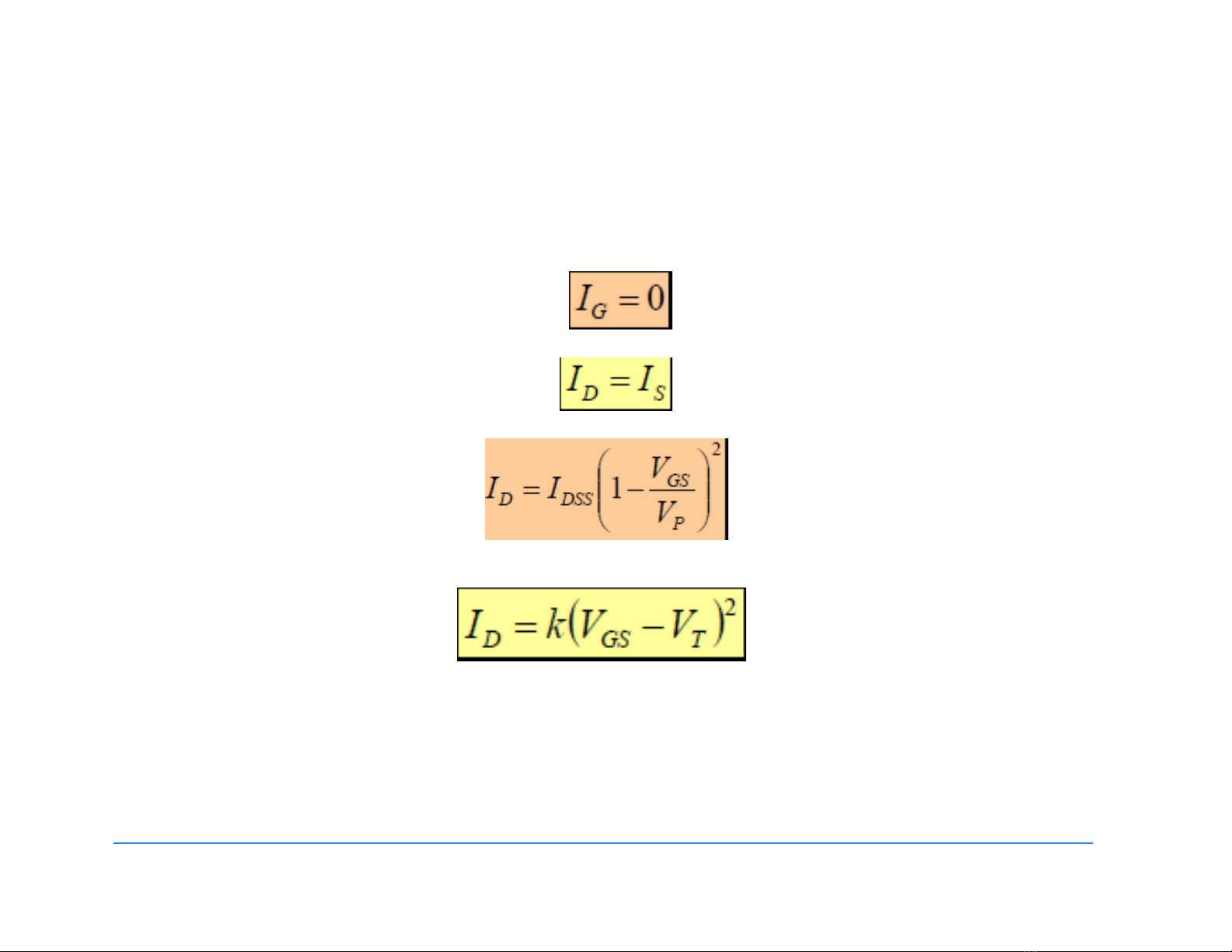

6.1. Giới thiệu

Yêu cầu: Tìm điểm làm việc tĩnh Q(IDQ, VDSQ)

Mối quan hệ tổng quát có thể áp dụng để phân tích dc tính toán phân cực

cho các mạch khuếch đai:

3

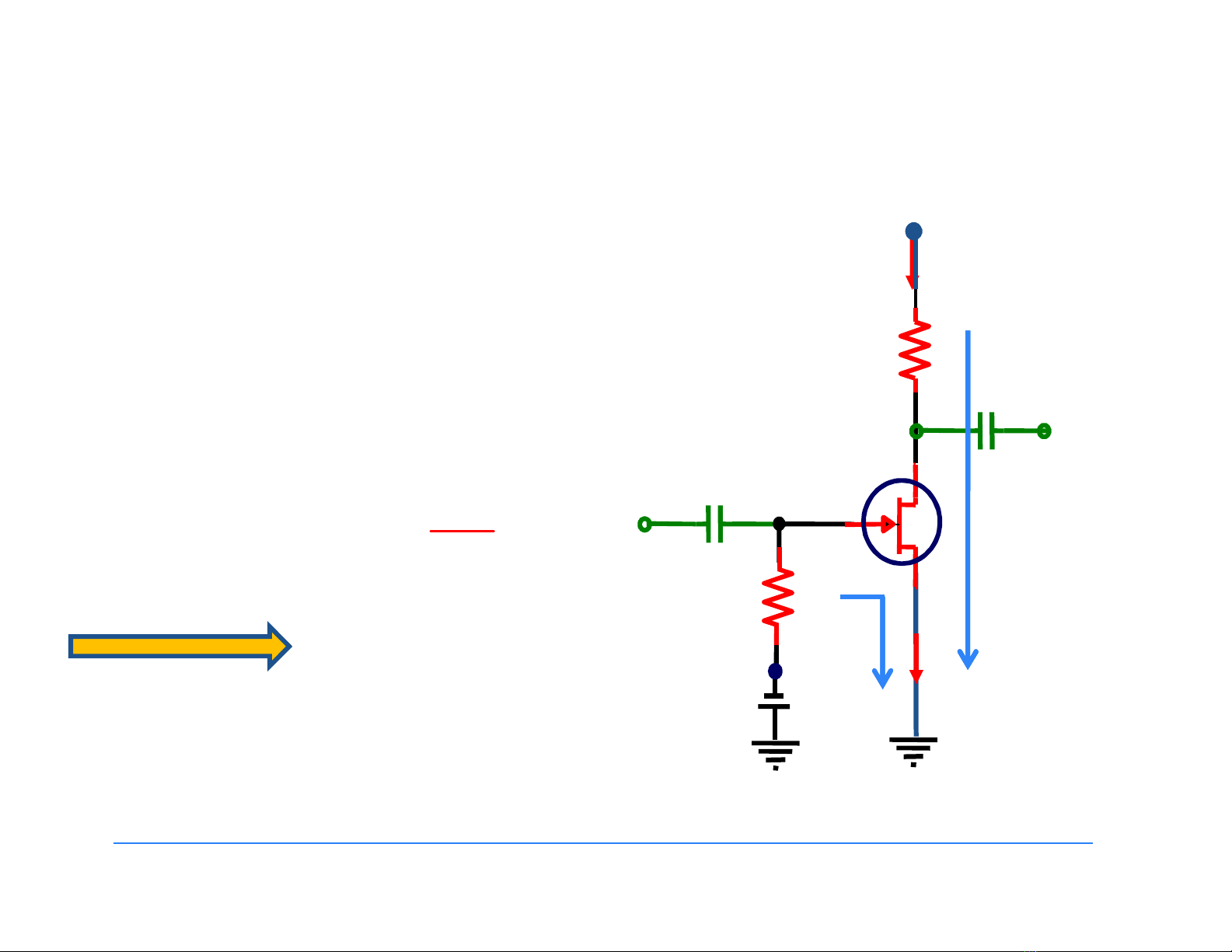

6.2.1. Mạch phân cực cố định

RD

C1

Vi

VGG

RG

1M

VO

C2

NJFET

G

D

S

IS

ID

VDD

IG= 0, ID= IS

VDS = VDD – ID.RD

2

1GS

D DSS

P

V

I I V

GS GG

V V

Mạch vòng GS

Thế (*) vào phương trình Shockley

Mạch vòng DS

(*)

IIDD

4

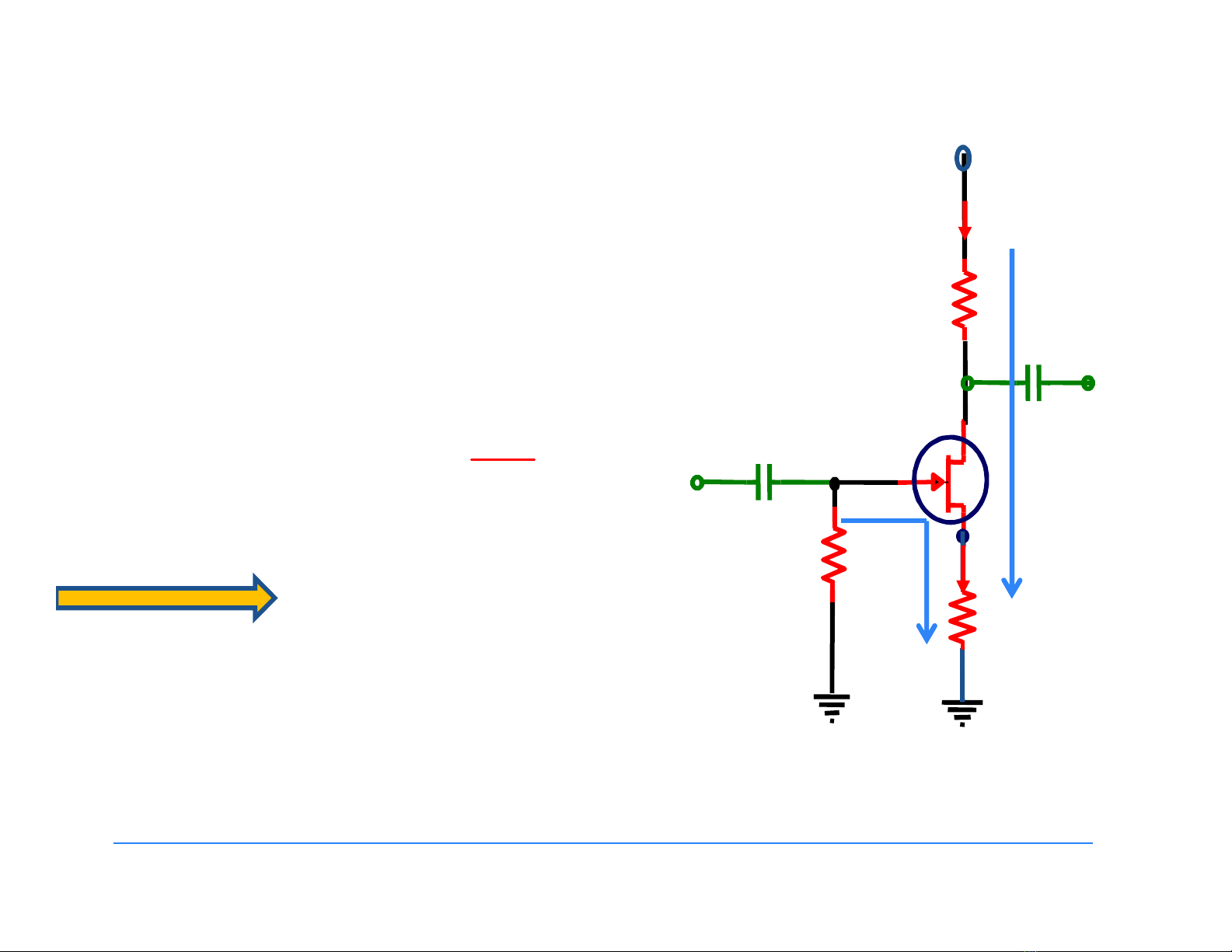

6.2.2. Mạch tự phân cực

RD

C1

ViRG

1M

VO

C2

NJFET

G

D

S

ID

RS

IS

VDD

VDS = VDD – ID.(RD+RS)

.

GS D S

V I R

IG= 0, ID= IS

Mạch vòng GS

2

1GS

D DSS

P

V

I I V

Thế VGS vào phương trình Shockley

Mạch vòng DS

Chọn nghiệm thoả 0 IDIDSS

VPVGS 0

IID1D1, I, ID2D2

5

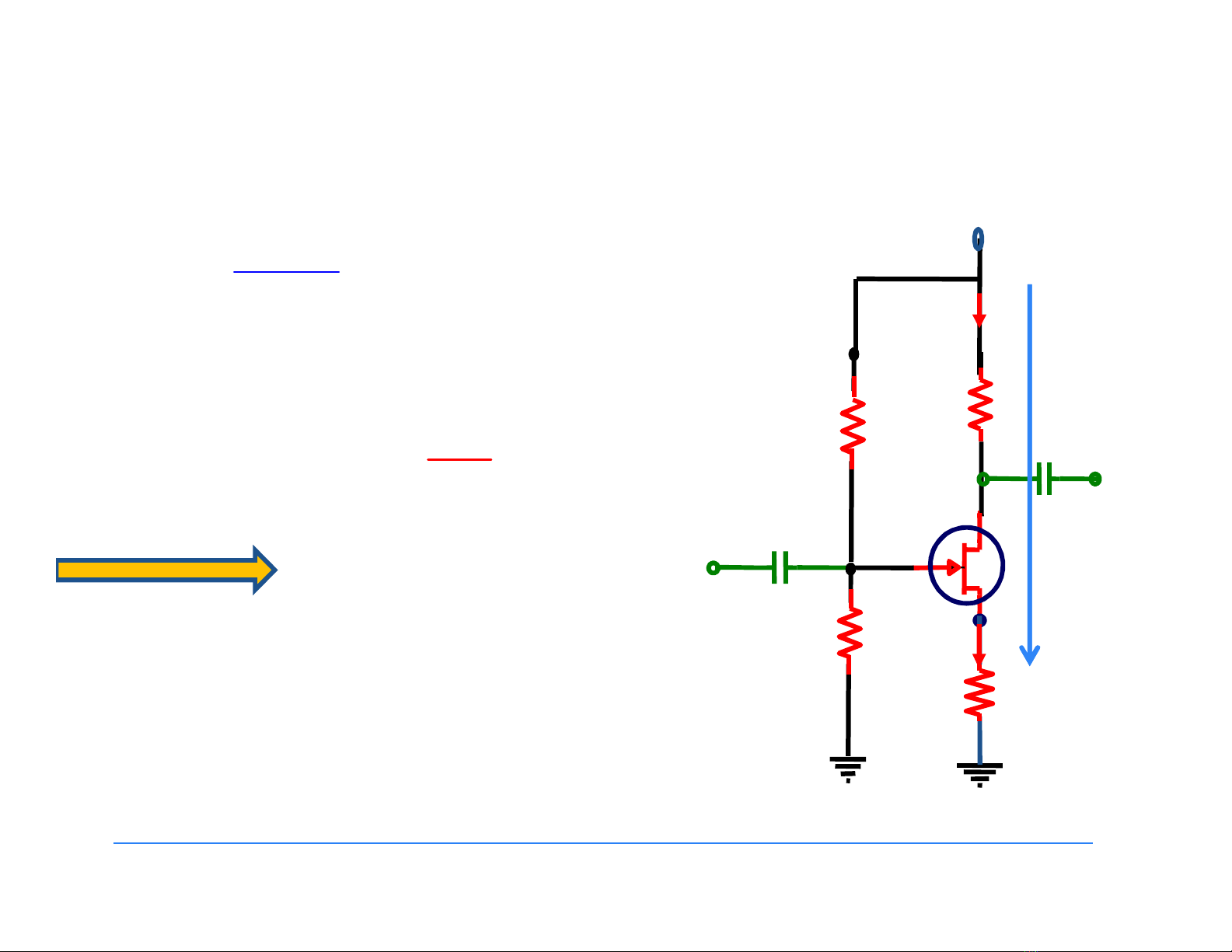

6.2.3. Mạch phân cực dùng cầu phân áp

RD

C1

Vi

R2

VO

C2

NJFET

G

D

S

ID

RS

IS

R1

VDD

VDS = VDD – ID.(RD+RS)

2

1GS

D DSS

P

V

I I V

2

1 2

G DD

R

V V

R R

.

GS D S G

V I R V

IG= 0, ID= IS

Thế VGS vào phương trình Shockley

Mạch vòng DS

Chọn nghiệm thoả 0 IDIDSS

VPVGS 0

IID1D1, I, ID2D2

![Bài giảng Kỹ thuật số: Chương 2 - Huỳnh Việt Thắng [Mới Nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260420/hoatrami2026/135x160/66851776745650.jpg)

![Thiết kế cung cấp điện cho Nhà máy cơ khí Duyên Hải: Bài tập lớn [chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260417/choang102426@st.vimaru.edu.vn/135x160/52181776391564.jpg)