1

ỨNG DỤNG FPGA TRONG

THIẾT KẾ CÁC MODULE

ĐIỀU KHIỂN

Chương 3

2

I. MỘT SỐ LƯU Ý KHI THIẾT KẾ

Trường ĐH Bách Khoa TP.HCM

1.1. Các biếnchỉđược gán trong 1 khốialways, không được gán trong

nhiềukhốialways khác

reg [7:0] a, b;

initial a = 4;

always @(posedge clk) begin

a = b + 2;

end

always @(posedge reset) begin

a = 0;

end

reg [7:0] a, b;

initial a = 4;

always @(posedge clk or posedge reset)

begin

if (reset == 1)

a = 0;

else

a = b + 2;

end

3

I. MỘT SỐ LƯU Ý KHI THIẾT KẾ

Trường ĐH Bách Khoa TP.HCM

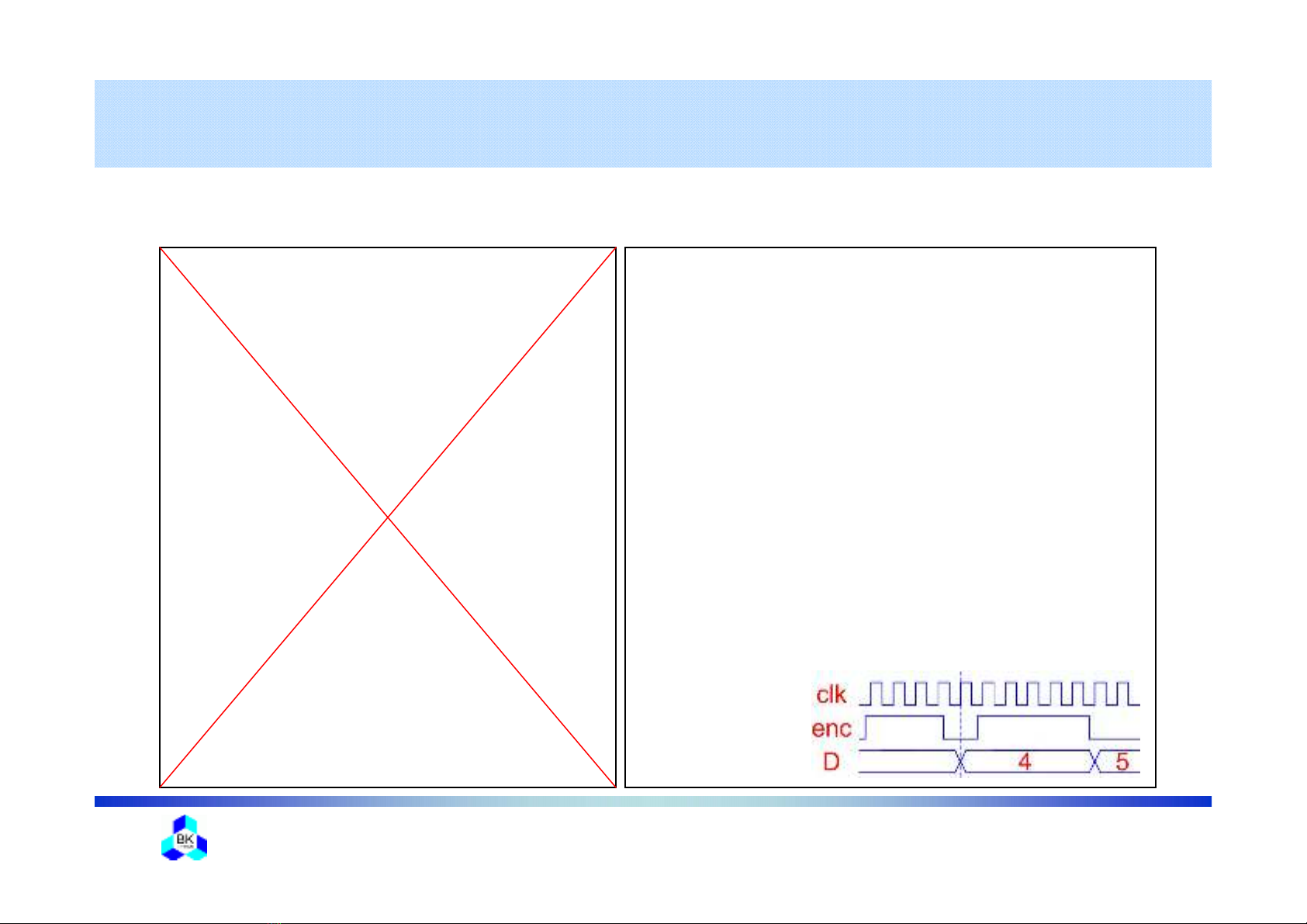

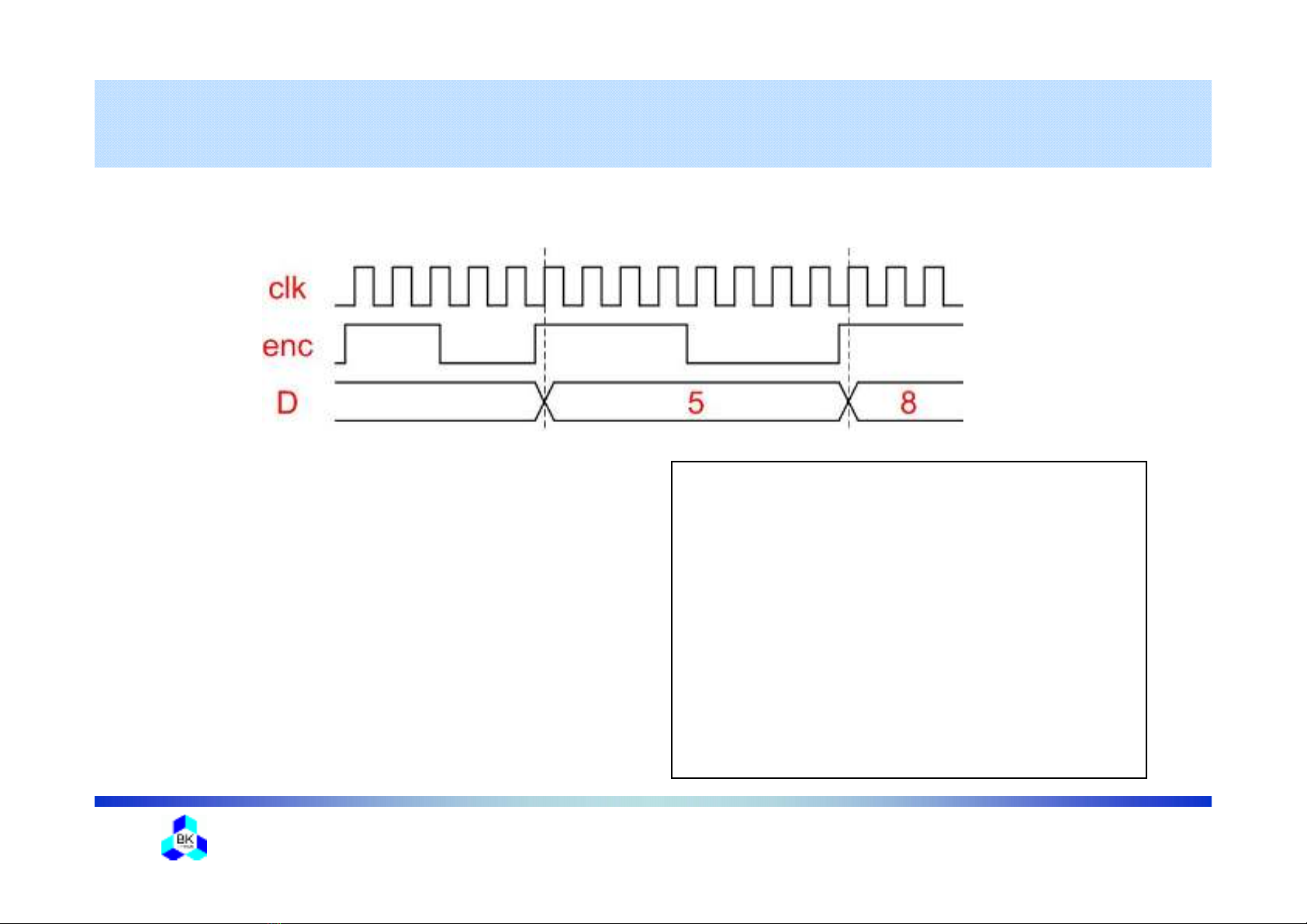

1.2. Để phát hiệnxungcạnh lên củacáctínhiệu, dùng xung clk tầnsốcao

chèn vào

module demxung_encoder (clk, enc, D);

input clk, enc;

output [7:0] D;

reg [7:0] D = 8’h00;

reg pre_enc = 0;

always @(posedge clk) begin

pre_enc <= enc;

if ({pre_enc, enc} == 2’b01)

D <= D + 1;

end

module demxung_encoder (clk, enc, D);

input clk, enc;

output [7:0] D;

reg [7:0] D = 8’h00;

reg pre_enc = 0;

always @(posedge clk) begin

pre_enc <= enc;

end

always @(posedge clk) begin

if ({pre_enc, enc} == 2’b01)

D = D + 1;

end

4

I. MỘT SỐ LƯU Ý KHI THIẾT KẾ

Trường ĐH Bách Khoa TP.HCM

1.3. Dùng biếntạmđể cậpnhậtgiátrịcác bộđếm

module do_dorongxung (clk, enc, D);

input clk, enc;

output [7:0] D;

reg [7:0] D = 8’h00;

reg pre_enc = 0;

always @(posedge clk) begin

pre_enc <= enc;

if ({pre_enc, enc} == 2’b01)

D <= 1;

else if ({pre_enc, enc} == 2’b11)

D <= D+1;

end

module do_dorongxung (clk, enc, D);

input clk, enc;

output [7:0] D;

reg [7:0] D = 8’h00, temp = 8’h01;

reg pre_enc = 0;

always @(posedge clk) begin

pre_enc <= enc;

if ({pre_enc, enc} == 2’b11)

temp <= temp+1;

else if ({pre_enc, enc} == 2’b10) begin

D <= temp; temp <= 0;

end

end

5

Trường ĐH Bách Khoa TP.HCM

1.4. Ví du 1: Viếtchương trình verilog đotầnsô

-Giá trị D đượccậpnhậtsaumỗi

cạnh lên của xung enc.

-Tầnsốxung clk chọnrấtlớnso

vớitầnsốcủa xung enc

-NếubộđếmD vượtquágiátrị

0xFF thì sẽluôn bằng 0xFF

module do_tanso (clk, enc, D);

input clk, enc;

output [7:0] D;

reg [7:0] D = 8’h00, temp = 8’h00;

reg pre_enc = 0;

always @(posedge clk) begin

…

end

I. MỘT SỐ LƯU Ý KHI THIẾT KẾ

![Tài liệu học tập Thiết kế hệ thống nhúng [mới nhất, đầy đủ]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260305/hoatulip2026/135x160/37051773135929.jpg)

![Giáo trình Tự động hóa quá trình sản xuất: Phần 2 [Đầy đủ/Chi tiết]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260424/vispacex_27/135x160/6191777378796.jpg)

![Giáo trình Kỹ thuật Vi điều khiển Phần 2: [Mô tả nội dung phần 2 nếu có]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260424/vispacex_27/135x160/62641777433528.jpg)

![Giáo trình Kỹ thuật Vi điều khiển Phần 1: [Mô tả chi tiết hơn về nội dung phần 1 nếu có thông tin]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260424/vispacex_27/135x160/15221777433529.jpg)