1

THIẾT KẾ PHẦN CỨNG

DÙNG FPGA

Chương 1

2

I. GIỚI THIỆU CẤU TRÚC FPGA

Trường ĐH Bách Khoa TP.HCM

1.1. FPGA (Field Programmable Gate Array)

-Làmạch tích hợpcókhảnăng cấuhìnhlại

bởingườithiếtkế, thựchiện các hàm logic

từcơbảnđếnphứctạp.

- FPGA đượccấuthànhtừcác bộphận:

•Cáckhốilogic cơbảnlậptrìnhđược

(logic block)

•Hệthống mạch liên kếtlậptrìnhđược

•Khối vào/ra (IO Pads)

•PhầntửthiếtkếsẵnkhácnhưDSP

slice, RAM, ROM, nhân vi xửlý..

-Cấu hình FPGA dùng ngôn ngữmô tả

phầncứng HDL (hardware description

language), mạch nguyên lý (schematic)

3

I. GIỚI THIỆU CẤU TRÚC FPGA

Trường ĐH Bách Khoa TP.HCM

1.1. FPGA (Field Programmable Gate Array)

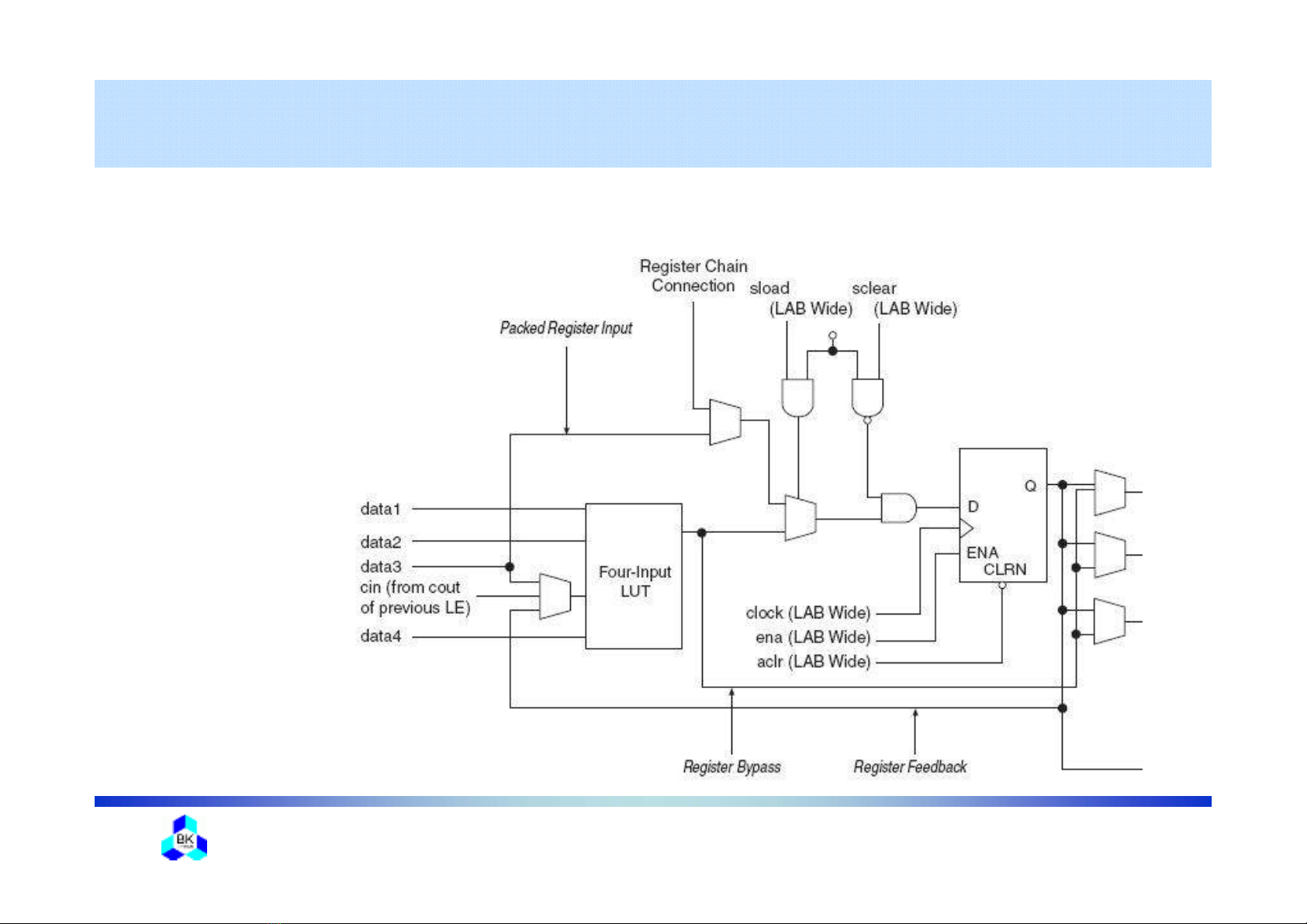

-CấutrúcLE

(logic element)

của Cyclone IV

(Altera)

- LUT : look

up table

4

I. GIỚI THIỆU CẤU TRÚC FPGA

Trường ĐH Bách Khoa TP.HCM

1.1. FPGA (Field Programmable Gate Array)

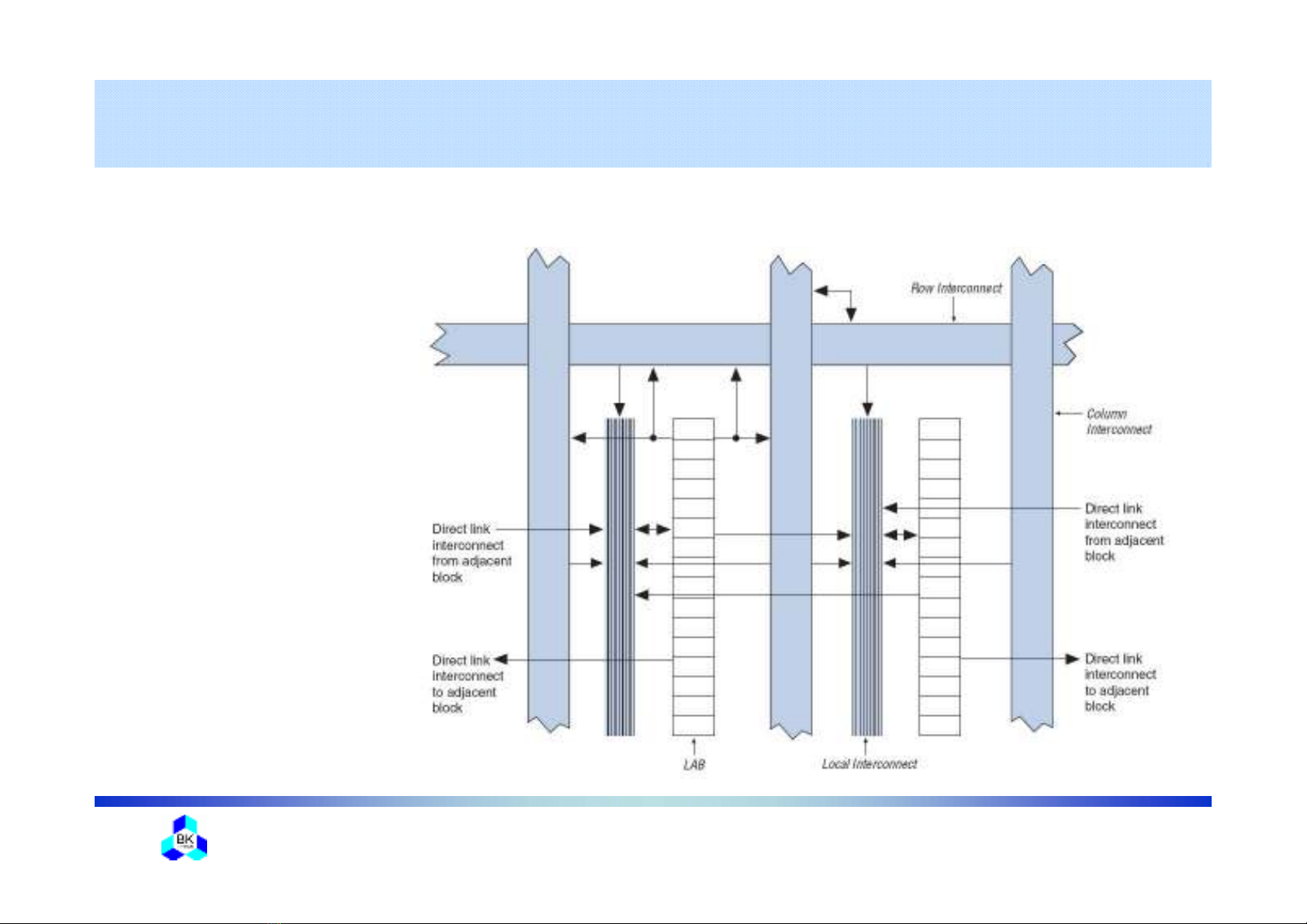

-CấutrúcLAB:

(logic array block)

•Chứa16 LE

•Tínhiệuđiều

khiểnLAB

•Mạch liên kết

5

I. GIỚI THIỆU CẤU TRÚC FPGA

Trường ĐH Bách Khoa TP.HCM

1.1. FPGA (Field Programmable Gate Array)

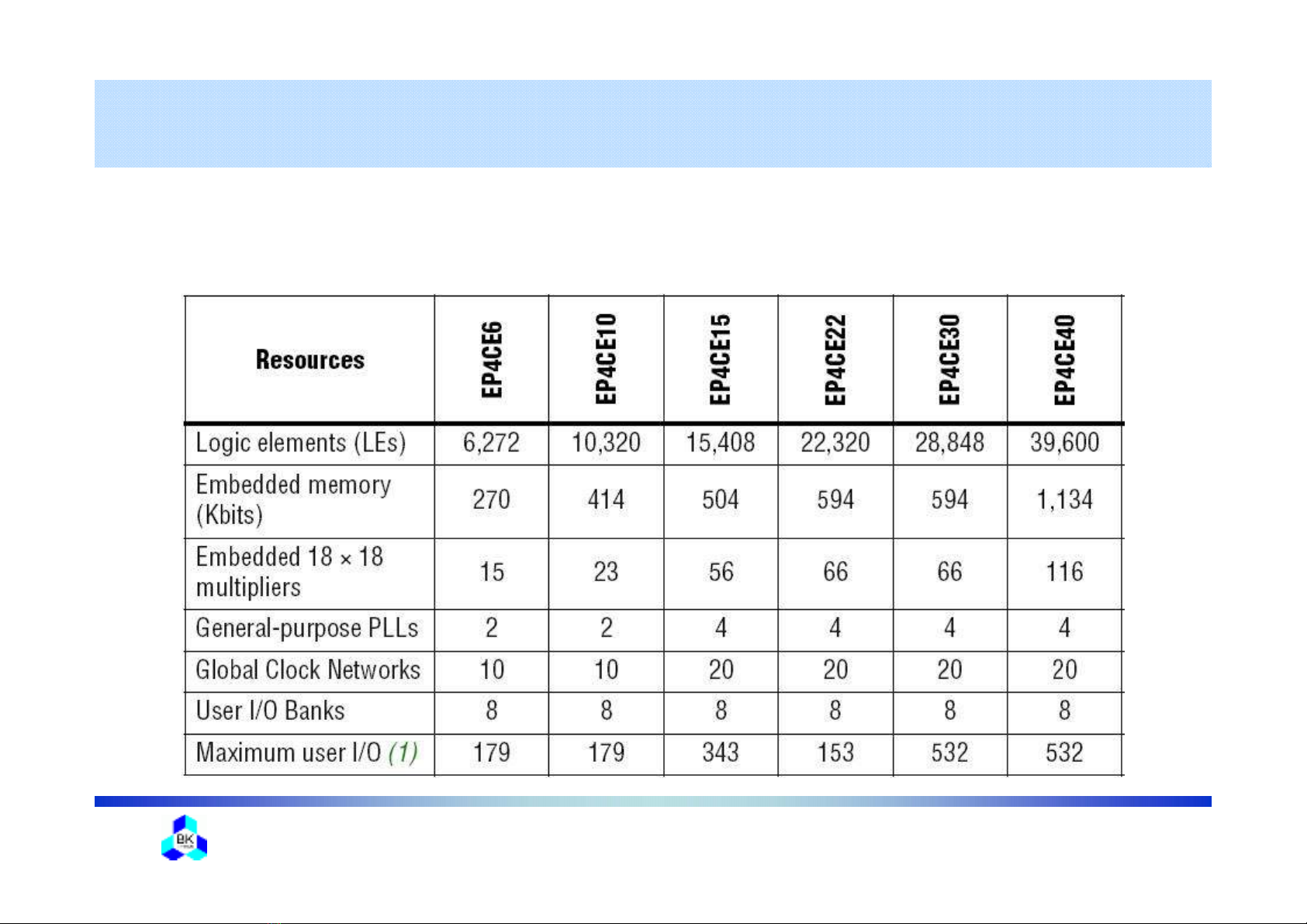

-HọCyclone IV của Altera

![Tài liệu học tập Thiết kế hệ thống nhúng [mới nhất, đầy đủ]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260305/hoatulip2026/135x160/37051773135929.jpg)

![Giáo trình Xử lý sự cố Diesel tàu thủy (Nghề Khai thác máy tàu thủy, Trình độ Trung cấp) - Trường Cao đẳng Nông nghiệp Thanh Hóa [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260508/songngu_011/135x160/23801778744471.jpg)