1

MỤC LỤC

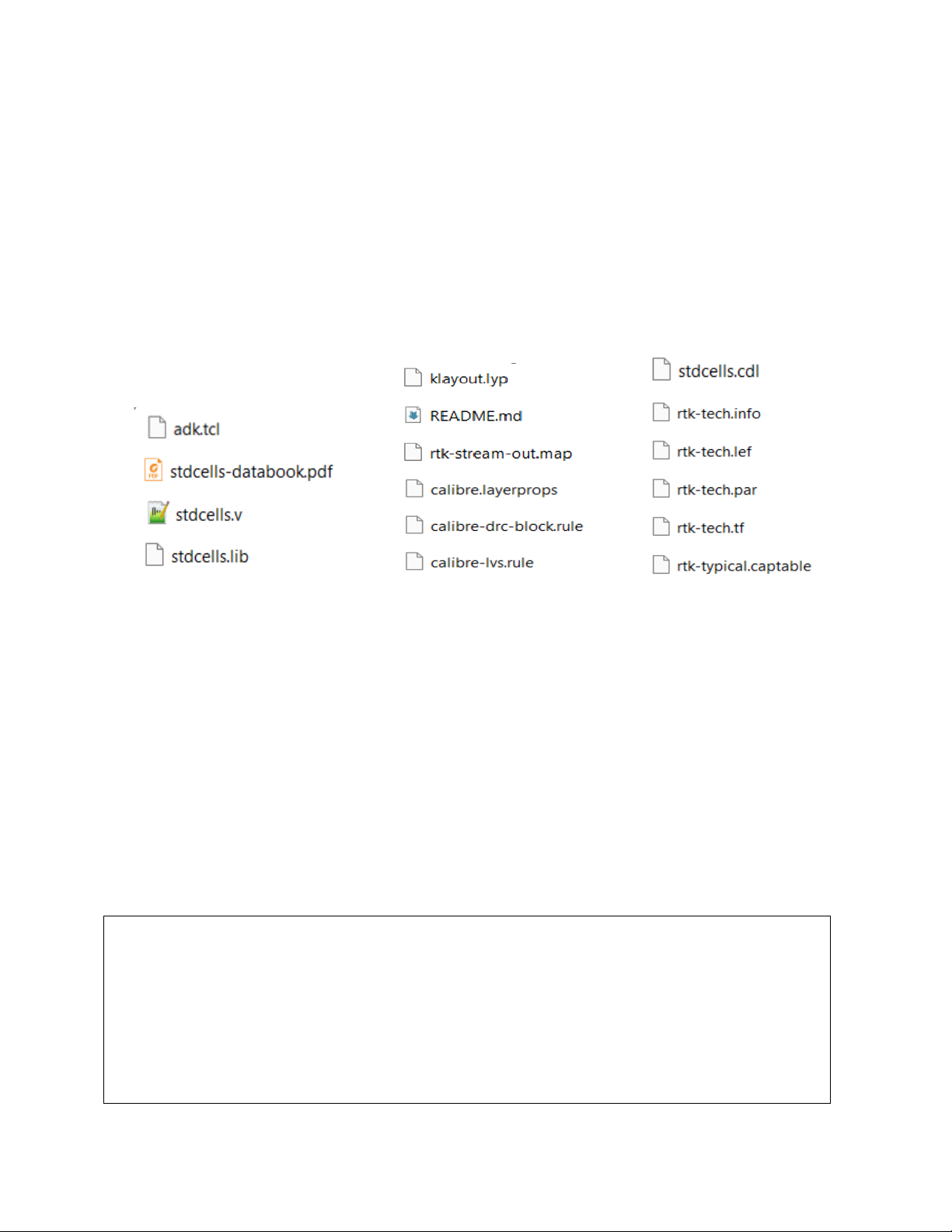

I. GIỚI THIỆU CHUNG VỀ THƯ VIỆN ......................................................... 2

II. PHÂN TÍCH CHI TIẾT THƯ VIỆN ............................................................. 3

1. File “adk.tcl” ............................................................................................... 3

2. File “calibre.layerprops” ........................................................................... 3

3. File “stdcells.cdl” ........................................................................................ 4

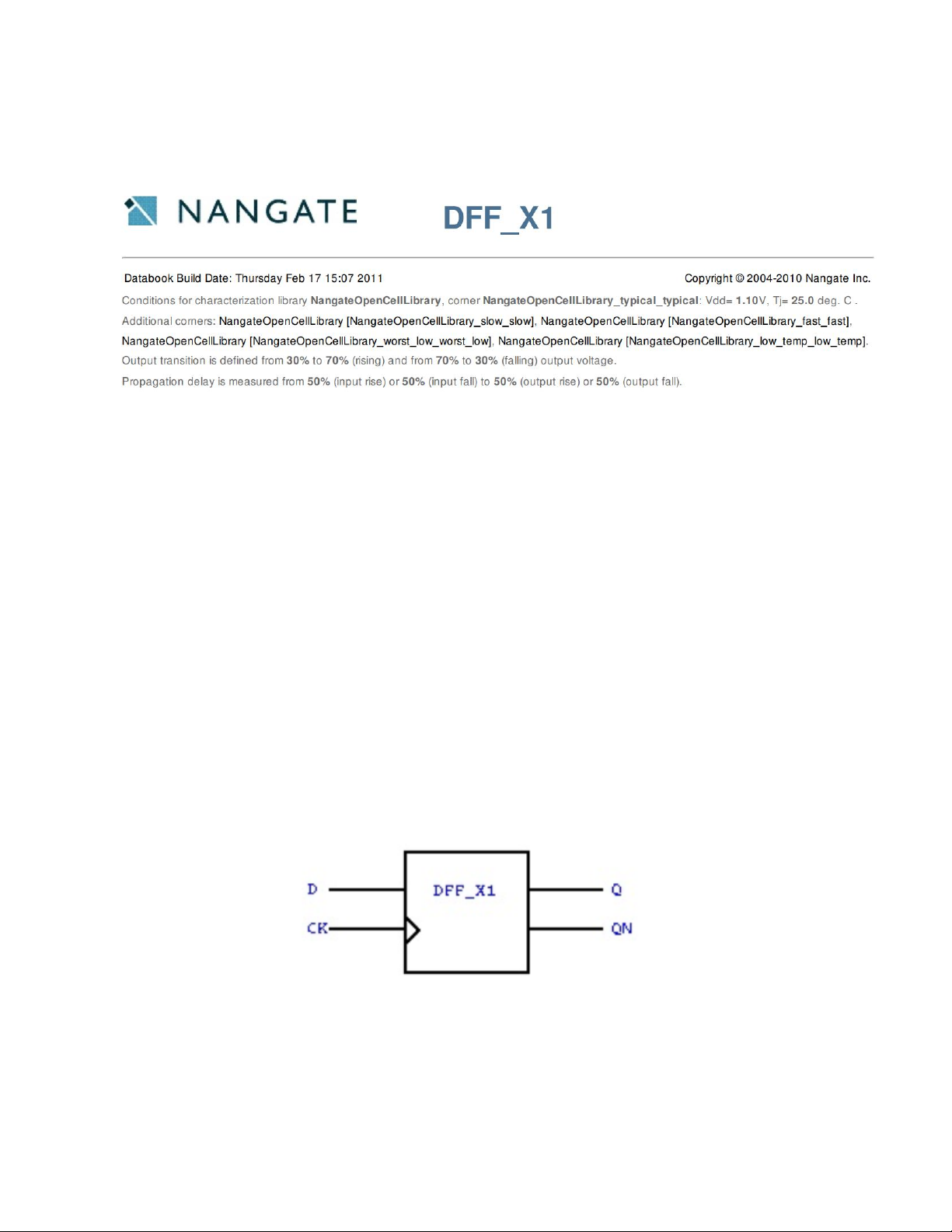

4. Databook của thư viện ............................................................................... 4

5. File “stdcells.v” ........................................................................................... 8

6. File “stdcells.lib” ........................................................................................ 12

III. PHÂN TÍCH VÀ MÔ PHỎNG KHỐI ALU ................................................. 20

1. Mô tả hoạt động ......................................................................................... 20

2. Code Verilog ............................................................................................... 20

3. Testbench .................................................................................................... 21

4. Kết quả mô phỏng ..................................................................................... 23

TÀI LIỆU THAM KHẢO .............................................................................. 23

BÁO CÁO KỸ NĂNG .................................................................................... 24