Ngườibáocáo:NguyễnChíLinhTàiliệu:TUT02.01

Ngày:9/8/2006Trang:1/10

Tutorialno02.01

Gửiđến:www.picvietnam.com

Nộidung:ChuẩngiaotiếpI2C–I2CtrongPIC

MICROSOFTWORD

Tómtắt:

GiớithiệuchungvềI2C

‐ ĐặcđiểmchungvềI2C:giaothức,địachỉ

‐ Cácchếđộhoạtđộng:master‐slave,multi‐master

ModuleI2CtrongViđiềukhiểnPIC

‐ Cấutrúcphầncứng

‐ Chếđộhoạtđộng:Master,Slave,Multi‐master

1. GiớithiệuchungvềI2C

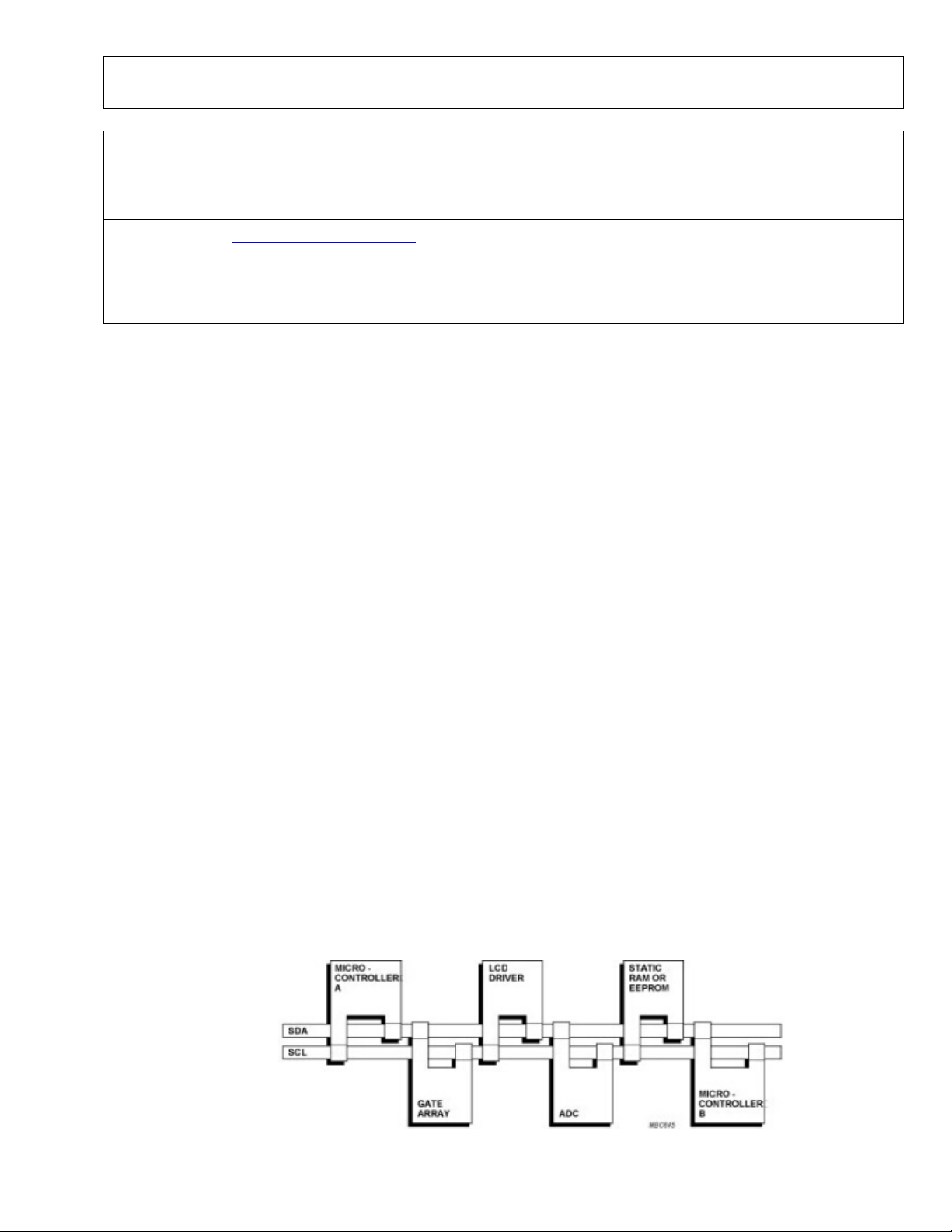

Ngàynaytrongcáchệthốngđiệntửhiệnđại,rấtnhiềuICshaythiếtbịngoạivicần

phảigiaotiếpvớicácICshaythiếtbịkhác–giaotiếpvớithếgiớibênngoài.Vóimụctiêu

đạtđượchiệuquảchophầncứngtốtnhấtvớimạchđiệnđơngiản,Phillipsđãpháttriển

mộtchuẩngiaotiếpnốitiếp2dâyđượcgọilàI2C.I2ClàtênviếttắtcủacụmtừInter‐

IntergratedCircuit–BusgiaotiếpgiữacácICvớinhau.

LịchsửI2C–Thêmvàođây…(Phầnnàysẽthêmsau…)

I2CmặcdùđượcpháttriểnbớiPhilips,nhưngnóđãđượcrấtnhiềunhàsảnxuấtIC

trênthếgiớisửdụng.I2Ctrởthànhmộtchuẩncôngnghiệpchocácgiaotiếpđiềukhiển,có

thểkểrađâymộtvàitêntuổingoàiPhilipsnhư:TexasIntrument(TI),Maxim‐Dallas,

analogDevice,NationalSemiconductor…BusI2Cđượcsửdụnglàmbusgiaotiếpngoại

vichorấtnhiềuloạiICkhácnhaunhưcácloạiViđiềukhiển8051,PIC,AVR,ARM,chíp

nhớnhưRAMtĩnh(StaticRam),EEPROM,bộchuyểnđổitươngtựsố(ADC),sốtươngtụ

(DAC),ICđiểukhiểnLCD,LED…

Hình1.1.BUSI2Cvàcácthiếtbịngoạivi

Ngườibáocáo:NguyễnChíLinhTàiliệu:TUT02.01

Ngày:9/8/2006Trang:2/10

1.1. ĐặcđiểmgiaotiếpI2C

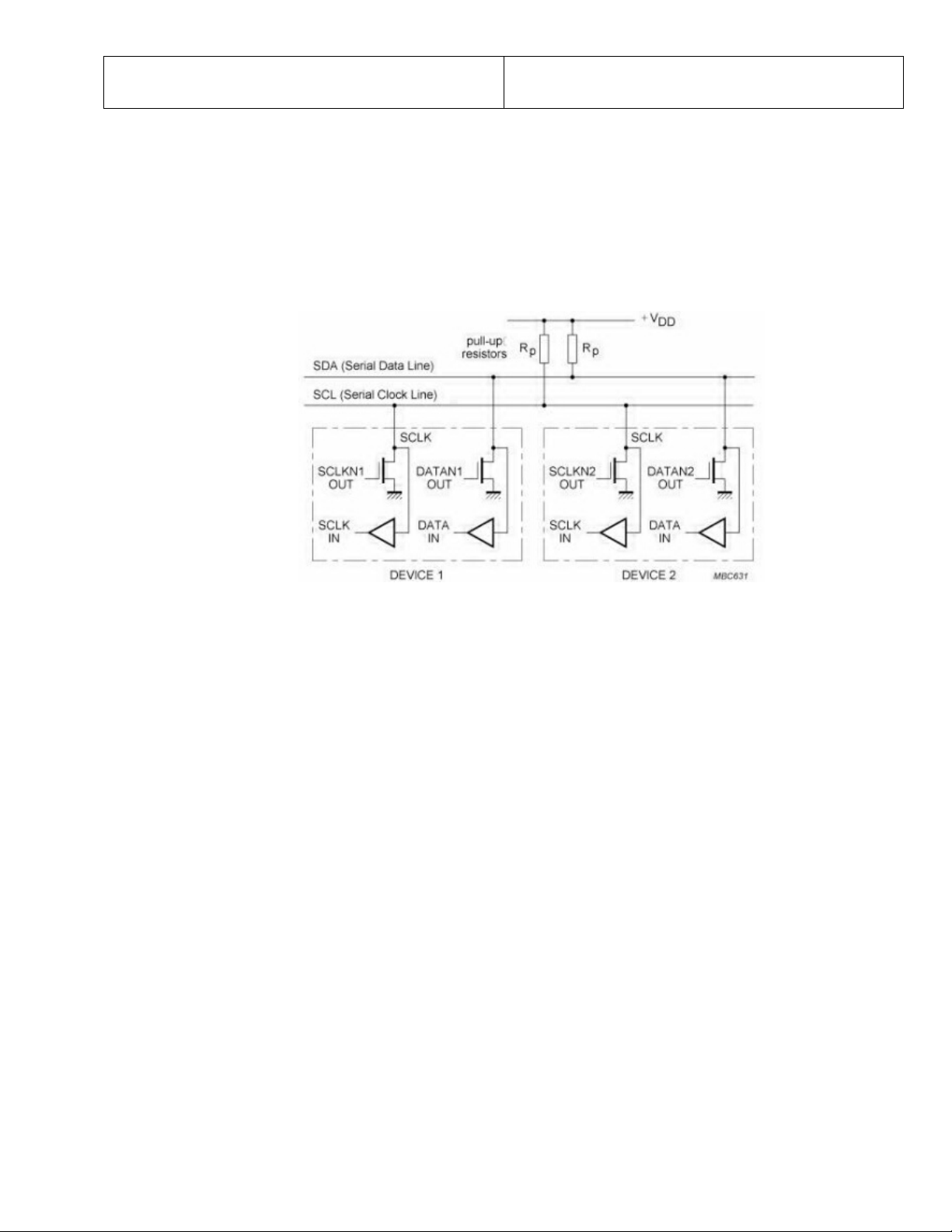

MộtgiaotiếpI2Cgồmcó2dây:SerialData(SDA)vàSerialClock(SCL).SDAlàđường

truyềndữliệu2hướng,cònSCLlàđườngtruyềnxungđồnghồvàchỉtheomộthướng.

Nhưhìnhvẽtrên,khimộtthiếtbịngoạivikếtnốivàođườngI2CthìchânSDAcủanósẽ

nốivớidâySDAcủabus,chânSCLsẽnốivớidâySCL.

Hình1.2.KếtnốithiếtbịvàobusI2Cởchếđộchuẩn(Standardmode)

vàchếđộnhanh(Fastmode)

MỗidâySDAhaySCLđềuđượcnốivớiđiệnápdươngcủanguồncấpthôngquamột

điệntrởkéolên(pull‐upresistor).Sựcầnthiếtcủacácđiệntrởkéonàylàvìchângiaotiếp

I2Ccủacácthiếtbịngoạivithườnglàdạngcựcmánghở(open‐drainoropen‐collector).

Giátrịcủacácđiệntrởnàykhácnhautùyvàotừngthiếtbịvàchuẩngiaotiếp,thườngdao

độngtrongkhoảng1KΩđến4.7KΩ.

Trởlạivớihình1.1,tathấycórấtnhiềuthiếtbị(ICs)cùngđượckếtnốivàomộtbus

I2C,tuynhiênsẽkhôngxảyrachuyệnnhầmlẫngiữacácthiếtbị,bởimỗithiếtbịsẽđược

nhậnrabởimộtđịachỉduynhấtvớimộtquanhệchủ/tớtồntạitrongsuốtthờigiankết

nối.Mỗithiếtbịcóthểhoạtđôngnhưlàthiếtbịnhậndữliệuhaycóthểvừatruyềnvừa

nhận.Hoạtđộngtruyềnhaynhậncòntùythuộcvàoviệcthiếtbịđólàchủ(master)haytớ

(slave).

MộtthiếtbịhaymộtICkhikếtnốivớibusI2C,ngoàimộtđịachỉ(duynhất)đểphân

biệt,nócònđượccấuhìnhlàthiếtbịchủ(master)haytớ(slave).Tạisaolạicósựphânbiệt

này?ĐólàvìtrênmộtbusI2Cthìquyềnđiềukhiểnthuộcvềthiếtbịchủ(master).Thiếtbị

chủnắmvaitròtạoxungđồnghồchotoànhệthống,khigiữahaithiếtbịchủ/tớgiaotiếp

thìthiếtbịchủcónhiệmvụtạoxungđồnghồvàquảnlýđịachỉcủathiếtbịtớtrongsuốt

quátrìnhgiaotiếp.Thiếtbịchủgiữvaitròchủđộng,cònthiếtbịtớgiữvaitròbịđộng

trongviêcgiaotiếp.

Ngườibáocáo:NguyễnChíLinhTàiliệu:TUT02.01

Ngày:9/8/2006Trang:3/10

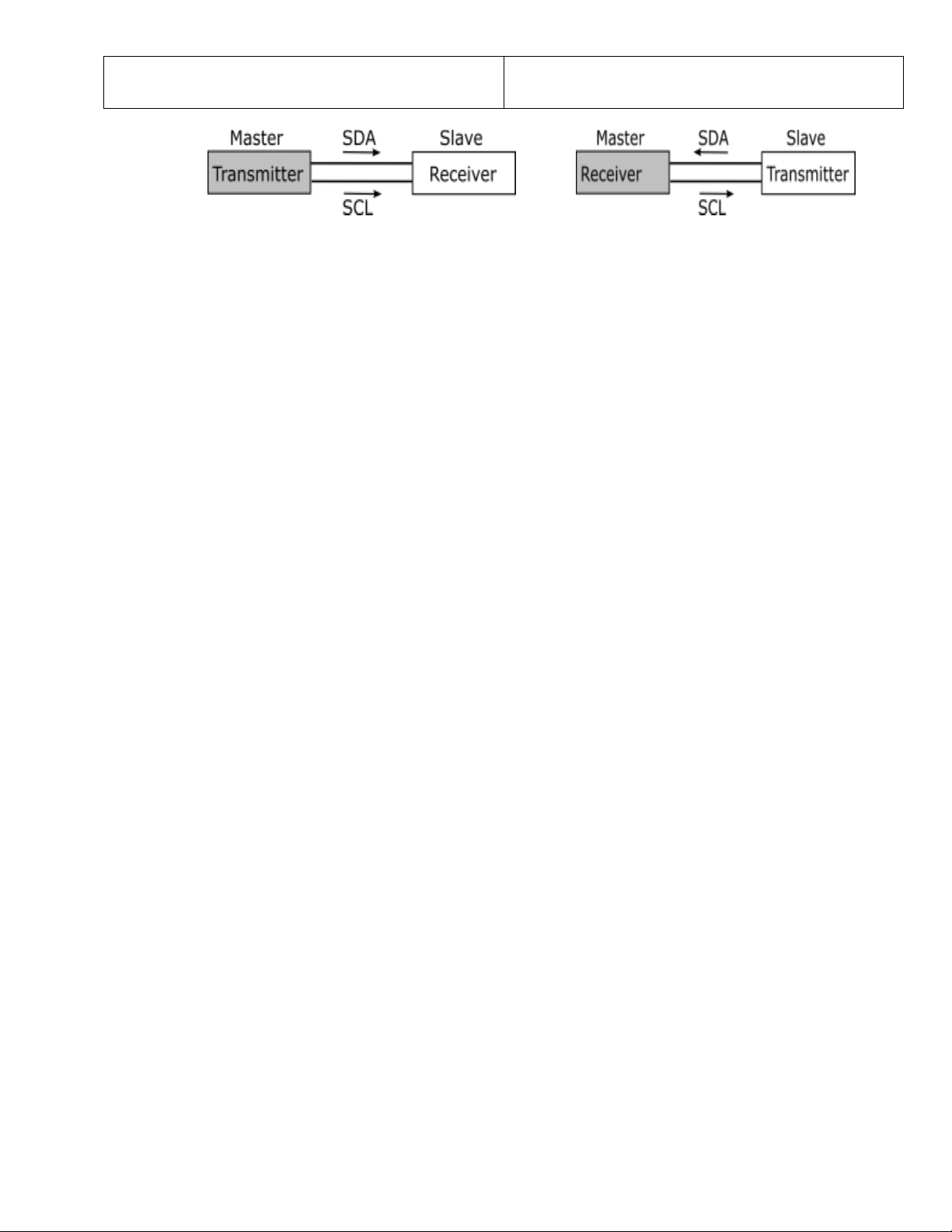

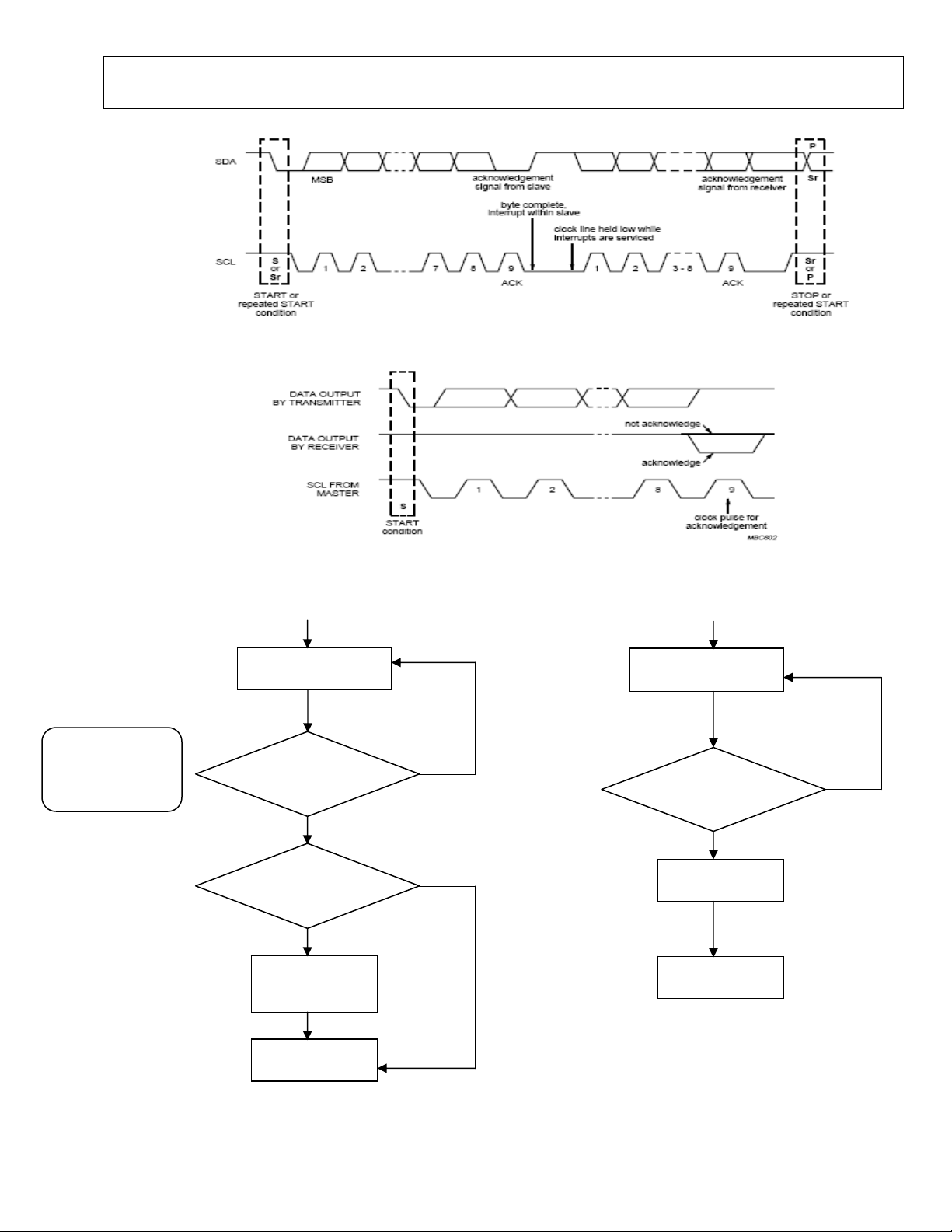

Hình1.3.Truyềnnhậndữliệugiữachủ/tớ

Nhìnhìnhtrêntathấyxungđồnghồchỉcómộthướngtừchủđếntớ,cònluồngdữliệu

cóthểđitheohaihướng,từchủđếntớhayngượclạitớđếnchủ.

VềdữliệutruyềntrênbusI2C,mộtbusI2Cchuẩntruyền8‐bitdữliệucóhướngtrên

đườngtruyềnvớitốcđộlà100Kbits/s–Chếđộchuẩn(Standardmode).Tốcđộtruyềncó

thểlêntới400Kbits/s–Chếđộnhanh(Fastmode)vàcaonhấtlà3,4Mbits/s–Chếđộcao

tốc(High‐speedmode).

MộtbusI2Ccóthểhoạtđộngởnhiềuchếđộkhácnhau:

- Mộtchủmộttớ(onemaster–oneslave)

- Mộtchủnhiềutớ(onemaster–multislave)

- Nhiềuchủnhiềutớ(Multimaster–multislave)

Dùởchếđộnào,mộtgiaotiếpI2Cđềudựavàoquanhệchủ/tớ.GiảthiếtmộtthiếtbịA

muốngửidữliệuđếnthiếtbịB,quátrìnhđượcthựchiệnnhưsau:

‐ ThiếtbịA(Chủ)xácđịnhđúngđịachỉcủathiếtbịB(tớ),cừngvớiviệcxácđịnh

địachỉ,thiếtbịAsẽquyếtđịnhviệcđọchayghivàothiếtbịtớ

‐ ThiếtbịAgửidữliệutớithiếtbịB

‐ ThiếtbịAkếtthúcquátrìnhtruyềndữliệu

KhiAmuốnnhậndữliệutừB,quátrìnhdiễnranhưtrên,chỉkháclàAsẽnhậndữliệu

từB.Tronggiaotiếpnày,AlàchủcònBvẫnlàtớ.Chitiếtviệcthiếtlậpmộtgiaotiếpgiữa

haithiếtbịsẽđượcmôtảchitiếttrongcácmụcdướiđây.

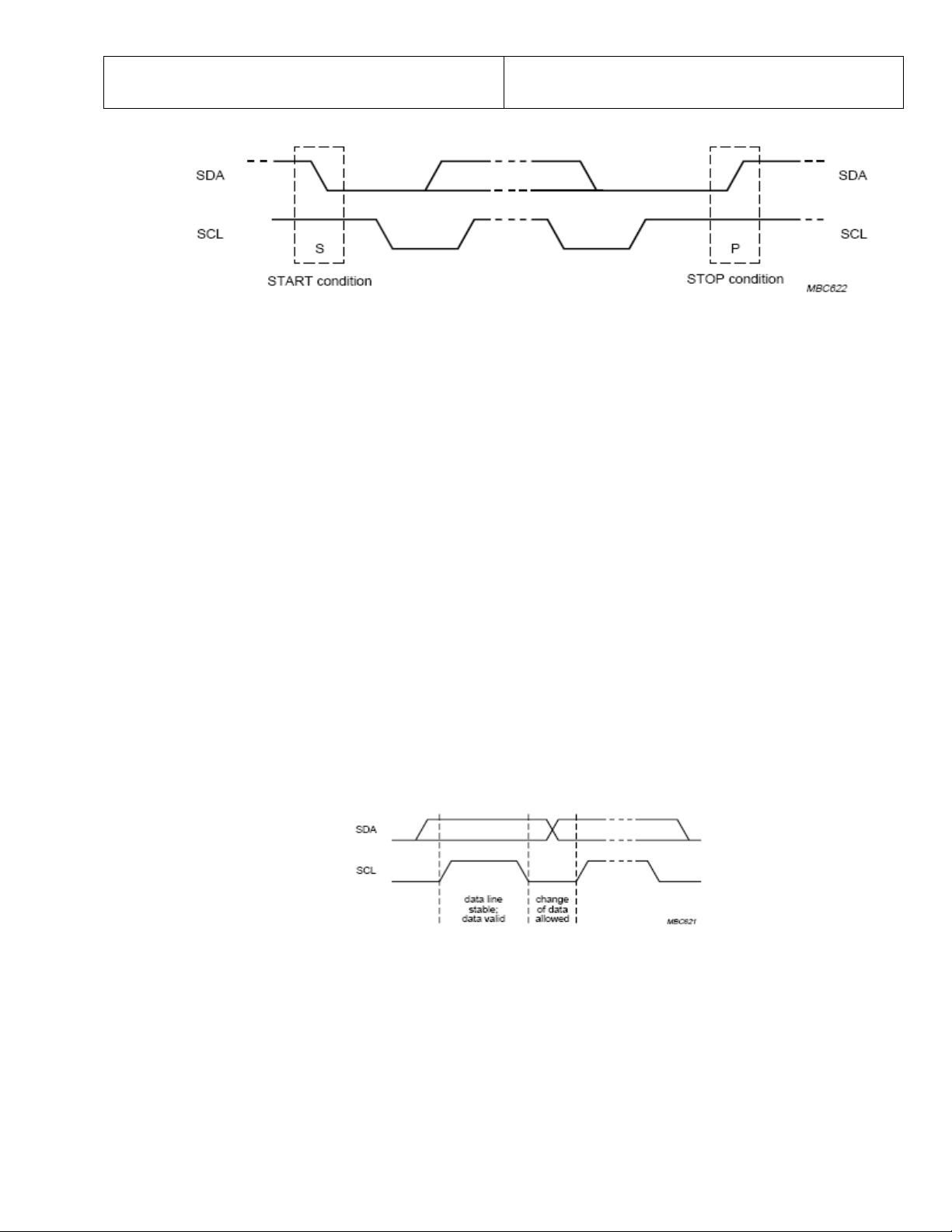

1.2. STARTandSTOPconditions

STARTvàSTOPlànhữngđiềukiệnbắtbuộcphảicókhimộtthiếtbịchủmuốnthiết

lậpgiaotiếpvớimộtthiếtbịnàođótrongmạngI2C.STARTlàđiềukiệnkhởiđầu,báo

hiệubắtđầucủagiaotiếp,cònSTOPbáohiệukếtthúcmộtgiaotiếp.Hìnhdướiđâymôtả

điềukiệnSTARTvàSTOP.

Banđầukhichưathựchiệnquátrìnhgiaotiếp,cảhaiđườngSDAvàSCLđềuởmức

cao(SDA=SCL=HIGH).LúcnàybusI2Cđượccoilàdỗi(“busfree”),sẵnsàngchomột

giaotiếp.HaiđiềukiệnSTARTvàSTOPlàkhôngthểthiếutrongviệcgiaotiếpgiữacác

thiếtbịI2Cvớinhau

Ngườibáocáo:NguyễnChíLinhTàiliệu:TUT02.01

Ngày:9/8/2006Trang:4/10

Hình1.4.ĐiềukiệnSTARTvàSTOPcủabusI2C

ĐiềukiệnSTART:mộtsựchuyểnđổitrạngtháitừcaoxuốngthấptrênđườngSDA

trongkhiđườngSCLđangởmứccao(cao=1;thấp=0)báohiệumộtđiềukiệnSTART

ĐiềukiệnSTOP:MộtsựchuyểnđổitrạngtháitừmứcthấplêncaotrênđườngSDA

trongkhiđườngSCLđangởmứccao.

CảhaiđiềukiệnSTARTvàSTOPđềuđượctạorabởithiếtbịchủ.SautínhiệuSTART,

busI2Ccoinhưđangtrongtrangtháilàmviệc(busy).BusI2Csẽrỗi,sẵnsàngchomột

giaotiếpmớisautínhiệuSTOPtừphíathiếtbịchủ.

SaukhicómộtđiềukiệnSTART,trongquatrìnhgiaotiếp,khicómộttínhiệuSTART

đượclặplạithayvìmộttínhiệuSTOPthìbusI2Cvẫntiếptụctrongtrạngtháibận.Tín

hiệuSTARTvàlặplạiSTARTđềucóchứcnănggiốngnhaulàkhởitạomộtgiaotiếp.

1.3. Địnhdạngdữliệutruyền

DữliệuđượctruyềntrênbusI2Ctheotừngbit,bitdữliệuđượctruyềnđitạimỗisườn

dươngcủaxungđồnghồtrêndâySCL,quátrìnhthayđổibitdữliệuxảyrakhiSCLđang

ởmứcthấp.

Hình1.5.Quátrìnhtruyền1bitdữliệu

Mỗibytedữliệuđượctruyềncóđộdàilà8bits.Sốlượngbytecóthểtruyềntrongmột

lầnlàkhônghạnchế.MỗibyteđượctruyềnđitheosaulàmộtbitACKđểbáohiệuđã

nhậndữliệu.Bitcótrọngsốcaonhất(MSB)sẽđượctruyềnđiđầutiên,cácbítsẽđược

truyềnđilầnlượt.Sau8xungclocktrêndâySCL,8bitdữliệuđãđượctruyềnđi.Lúcnày

thiếtbịnhận,saukhiđãnhậnđủ8bítdữliệusẽkéoSDAxuốngmứcthấptạomộtxung

ACKứngvớixungclockthứ9trêndâySDAđểbáohiệuđãnhậnđủ8bit.Thiếtbịtruyền

khinhậnđượcbitACKsẽtiếptụcthựchiệnquátrìnhtruyềnhoặckếtthúc.

Ngườibáocáo:NguyễnChíLinhTàiliệu:TUT02.01

Ngày:9/8/2006Trang:5/10

Hình1.6.DữliệutruyềntrênbusI2C

Hình1.7.BitACKtrênbusI2C

TruyềnNhận

Hình1.8.Lưuđồthuậttoánquátrìnhtruyêngnhậndữliệu

Buffer=databit

BufferFull?

ReadBuffer

SendACK

NO

YES

SDA=data_bit

Clock=8?

ACK?

Next_byte

or STOP

STOP

NO

NO

YES

YES

Kiểmtraxem

đãtruyềnđủ

8

b

i

tch

ưa

![Các chip bổ trợ: [Thông tin chi tiết/Hướng dẫn chọn mua/Nơi bán]](https://cdn.tailieu.vn/images/document/thumbnail/2011/20111130/monocin/135x160/cac_chip_bo_tro_119.jpg)

![Hệ thống đèn chạy ban ngày tốt nhất: [Hướng dẫn]](https://cdn.tailieu.vn/images/document/thumbnail/2011/20111124/gauhaman123/135x160/dien_xe_36__8662.jpg)

![Tài liệu về 555: [Thêm từ mô tả nếu có thể, ví dụ: hướng dẫn, phân tích chi tiết]](https://cdn.tailieu.vn/images/document/thumbnail/2011/20111105/1231020082/135x160/555_la_mot_loai_linh_kien_kha_la_pho_bien_bay_gio_voi_viec_de_dang_tao_duoc_xung_vuong_va_co_the_thay_doi_tan_so_tuy_thich_3818.jpg)

![Giáo trình Trang bị điện nước (TC) - Trường Cao đẳng Công nghiệp Thanh Hóa [Ngành Điện nước]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260511/hoatrami2026/135x160/14221778681890.jpg)