P&I Ch5-Digi In/Out 1

ch 5. digital interface

•GhÐp nèi hÖ trung t©m víi ThiÕt bÞ ngo¹i vi qua

c¸c tÝn hiÖu logic 1/0

•pARALLEL iN/OUT

–poRTS: principle, pPI, Centronics/LPT

–PCMCIA, Dual ported Ram.

–INTERCACing to devices: Key pad, LED, text

panel, encoder, STEP motor, ...

–hI-pOWER INTERFACE: relay, scr, triac, power

mosfet, igbt...

•sERIAL in/OUT: Sync, async,

–RS-232, RS-485, RS-422

–modem...

P&I Ch5-Digi In/Out 2

5.1. parallel interface: 5.1.1. nGuyªn lý

•In/Out nhiÒu bit ®ång thêi, nhanh, gÇn

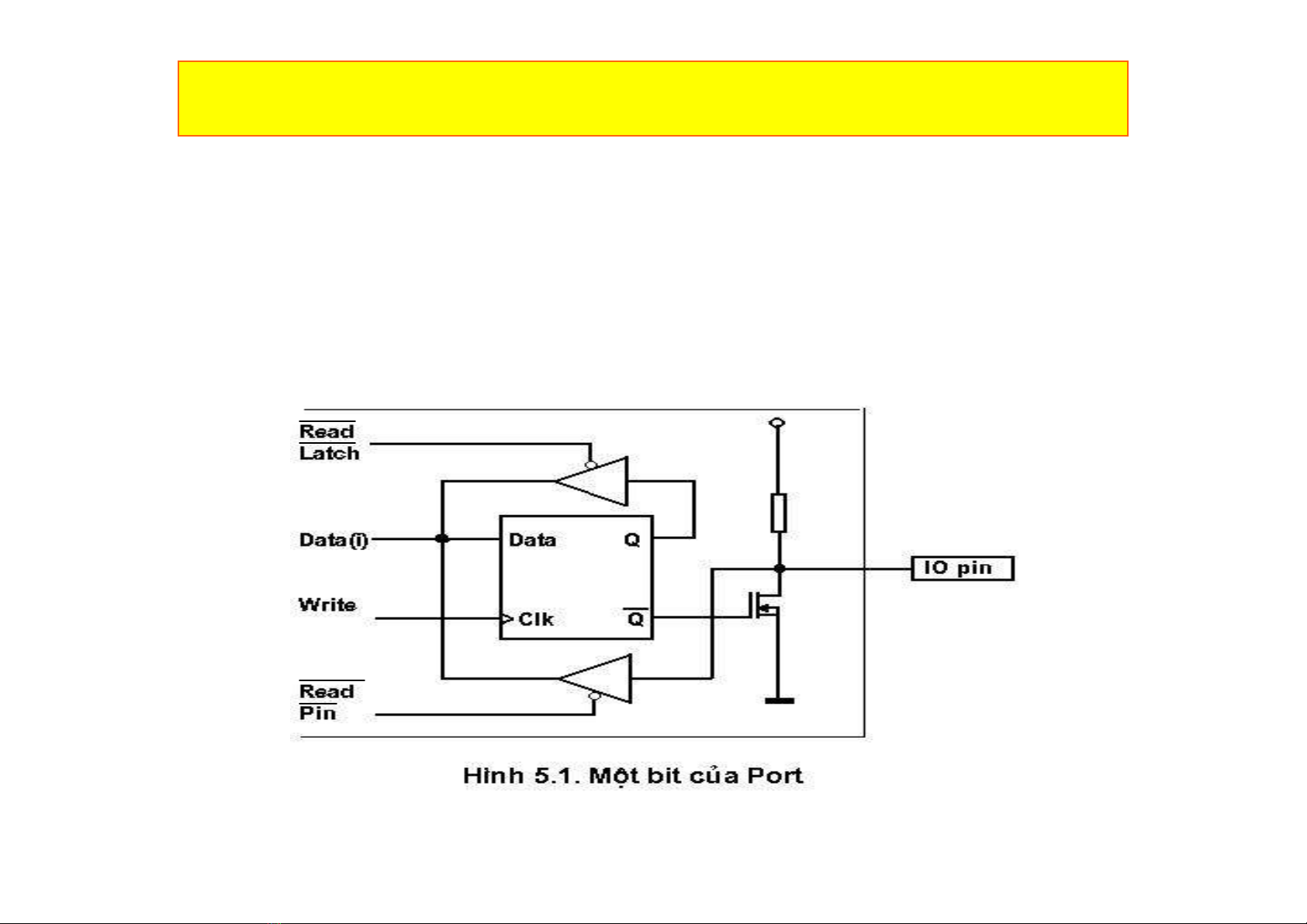

a. A Port Line (Ù1bit port):

– Output Port: Latched Output (chèt ra), D_Flip-Flops

– Unlatched Input, h×nh 5.1. single IO line/pin

P&I Ch5-Digi In/Out 3

• D Flip-Flop (D trigger):

– Là 1 trong những phần tử cơ bản của hệdãy,

– D – data, lưu giữ1 bit sốliệu.

– 4/6/8 D flip-flop => tạo ra 4/6/8 bit register, nhiều

registers đóng trong 1 chip là SRAM.

– Input:

• Data bit: 1 hoặc 0

•Clock, thường là sườn lên, ghi nhận giá trịcủa data và lưu lại

cho đến khi có bit sốliệu khác ghi đèlên.

•[Cóthểcó] clear – xóa; Preset – đặt trước

– Output:

•Q -ứng với giá trịdata input vào thời điểm có clock

•/Q – đảo của Q.

–Có2 loại: Transparent (HC373) và Master-Slave

(HC374)

P&I Ch5-Digi In/Out 4

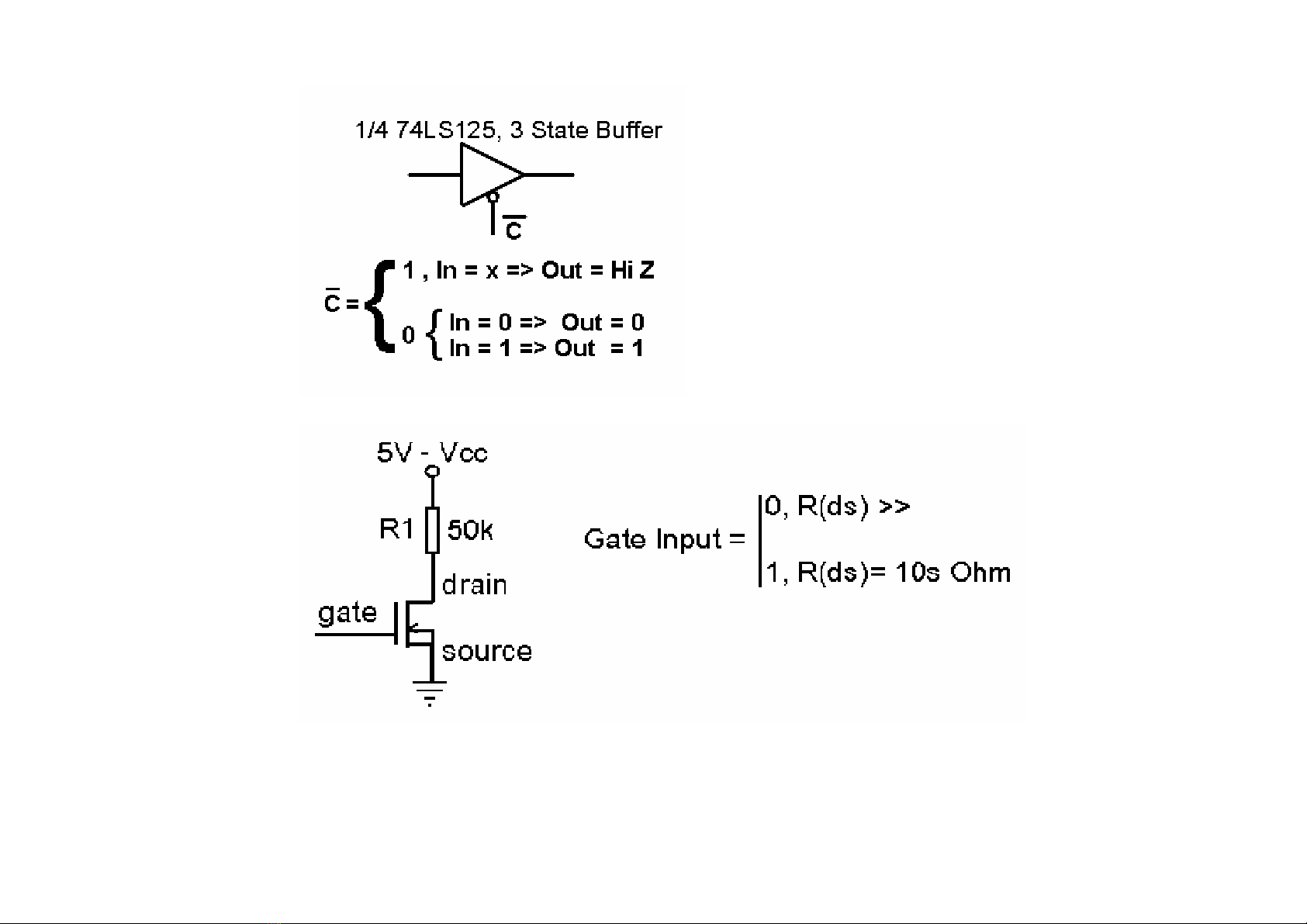

H. 501 b, c

MOSFET (Metal Oxide Semiconductor Field Effect Transistor)

P&I Ch5-Digi In/Out 5

• Write pin: bit 0 or 1, clock = ↑

– Write bit 0: D flip-flop => Q = 0; -Q = 1 =>

gate = 1 => R(ds) MOSFET = ON => pin = 0

– Write bit 1 D flip-flop => Q = 1; -Q = 0 =>

gate = 0 => R(ds) MOSFET = OFF => pin = 1

• Read pin: (Input line– out “1” firstly)-

ReadPin = 0 (!) => open 3 state lower

buffer => 1/0 from pin => data bus (i)

• ReadLatch (Reading bit out previously) :

-ReadLatch = 0 (!) => open 3 state higher

buffer => 1/0 from pin => data bus (i)

![Tổng luận Internet vạn vật (IoT): Hiện tại và tương lai [A-Z]](https://cdn.tailieu.vn/images/document/thumbnail/2021/20210201/caygaocaolon10/135x160/6521612151141.jpg)

![Bài tập thảo luận Công nghệ thông tin [năm] mới nhất](https://cdn.tailieu.vn/images/document/thumbnail/2017/20170824/sagami/135x160/71503585846.jpg)

![Tài liệu Công Nghệ Internet tiếng Việt [Mới Nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2015/20150917/tuyennt_1991/135x160/1775231_349.jpg)

![Ngân hàng đề thi trắc nghiệm Kiến trúc máy tính [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260514/hoahongxanh0906/135x160/49281779160279.jpg)