CỘNG HOÀ XÃ HỘI CHỦ NGHĨA VIỆT NAM

Độc lập-Tự do-Hạnh phúc

ĐỀ THI TỐT NGHIỆP CAO ĐẲNG NGHỀ KHOÁ 3 (2009-2012)

NGHỀ: ĐIỆN TỬ CÔNG NGHIỆP

MÔN THI: LÝ THUYẾT CHUYÊN MÔN NGHỀ

Mã đề thi: ĐTCN - LT05

Hình thức thi: Viết

Thời gian: 180 Phút (Không kể thời gian giao đề thi)

ĐỀ BÀI

Câu 1 (2đ): Thiết kế bộ so sánh 2 số nhị phân 1 bit.

Câu 2 (2đ): Mạch chỉnh lưu thyristors 1 pha một nửa chu kỳ điện áp đầu vào mạch chỉnh

lưu có giá trị hiệu dụng là 120V, cung cấp cho tải thuần trở, ta đo được điện áp trung bình

trên tải 50V.

Tính góc mở cho Thyristors

Câu 3 (3đ): Trình bày chế độ hoạt động counter của bộ TIMER0 trong vi điều khiển họ

8051. Viết chương trình ví dụ điều khiển TIMER0 hoạt động ở chế độ counter.

Câu 4 (3đ): (phần tự chọn, các trường tự ra đề)

………, ngày……..tháng……….năm………..

Duyệt Hội đồng thi tốt nghiệp Tiểu ban ra đề thi

CỘNG HOÀ XÃ HỘI CHỦ NGHĨA VIỆT NAM

Độc lập-Tự do-Hạnh phúc

ĐỀ THI TỐT NGHIỆP CAO ĐẲNG NGHỀ KHOÁ 3 (2009-2012)

NGHỀ: ĐIỆN TỬ CÔNG NGHIỆP

MÔN THI: LÝ THUYẾT CHUYÊN MÔN NGHỀ

Mã đề thi: DA ĐTCN - LT05

Câu Đáp án Điểm

I. Phần bắt buộc

1

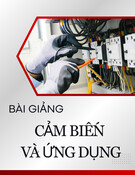

+ B¶ng ch©n lý: + Hµm logic: F1 (Ai = Bi) = Ai Bi

F2 (Ai > Bi) = Ai Bi

F3 (Ai < Bi) = Ai Bi

§Çu vµo

§Çu ra

Ai Bi F1

F2

F3

0 0 1

0 0

0 1 0

0 1

1 0 0

1 0

1 1 1

0 0

0,5

0,5

1

2 -Đưa ra công thức tổng quát tính giá trị điện áp trung bình sau mạch chỉnh lưu:

du

T

U

T

dd

0

1 Trong đó:

T: chu kỳ làm việc

Ud: giá trị điện áp trung bình của tải.

ud: điện áp tức thời của tải.

-Áp dụng để tính công thức điện áp trung bình trong sơ đồ

)cos1(

2

2

sin2.

2

12

UdUd

0,5

0,5

+ S¬ ®å logic

:

Ai

Bi

F1

F2

F3

-Từ công thức trên ta tính được cosα theo công thức:

1

2

.2

cos

2

U

Ud

-Thay số vào ta tính đươc α

86,0arccos)1

120.2

50.14,3.2

arccos(

=>

=600

0,5

0,5

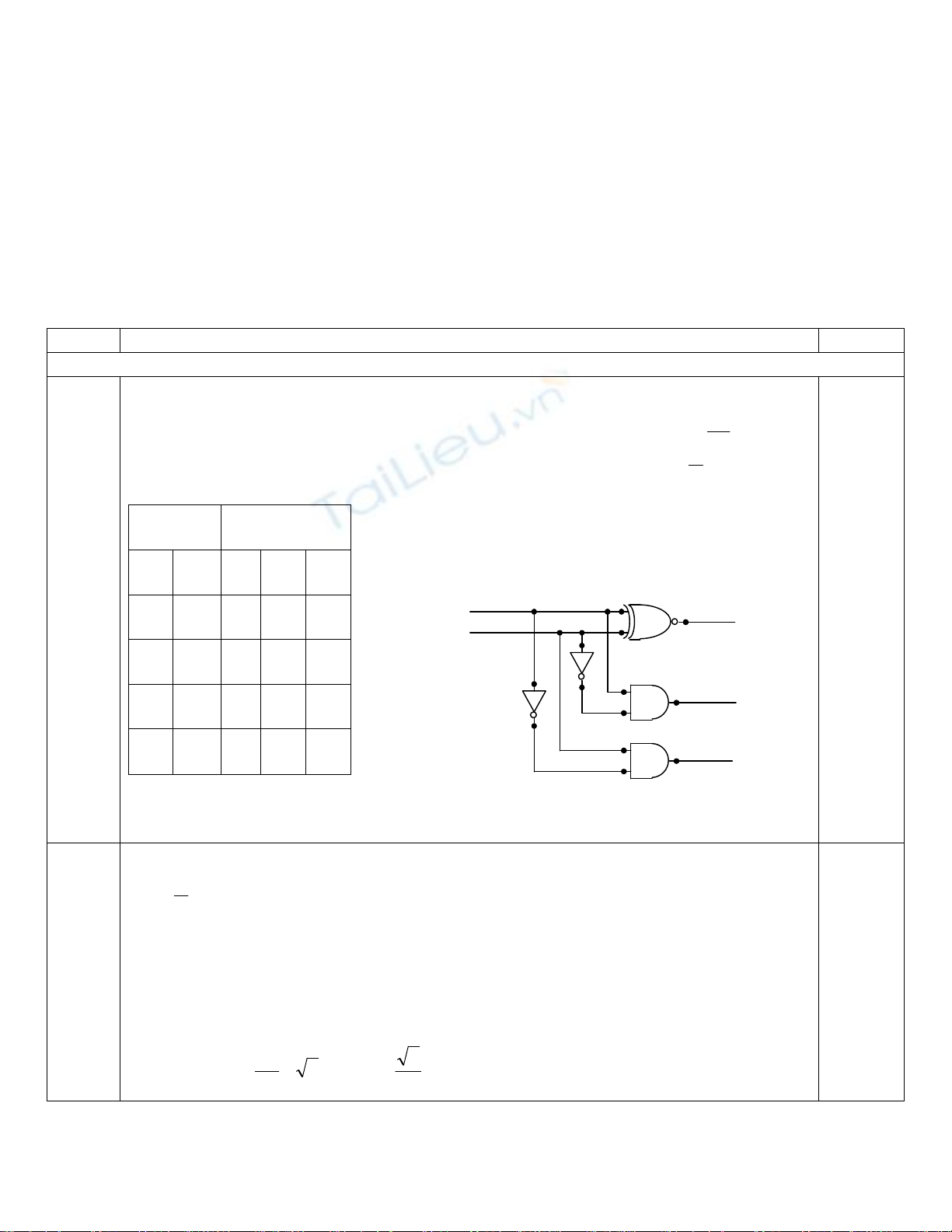

3 - Hoạt động counter của bộ TIMER0 trong vi điều khiển chế độ 16 bit:

Trong chế độ 1, bộ Timer dùng cả 2 thanh ghi TH0 và TL0 để chứa giá trị

đếm vì vậy chế độ này còn được gọi là chế độ định thời 16 bit. Bit MSB sẽ là bit D7

của TH0 còn bit LSB là D0 của TL0.

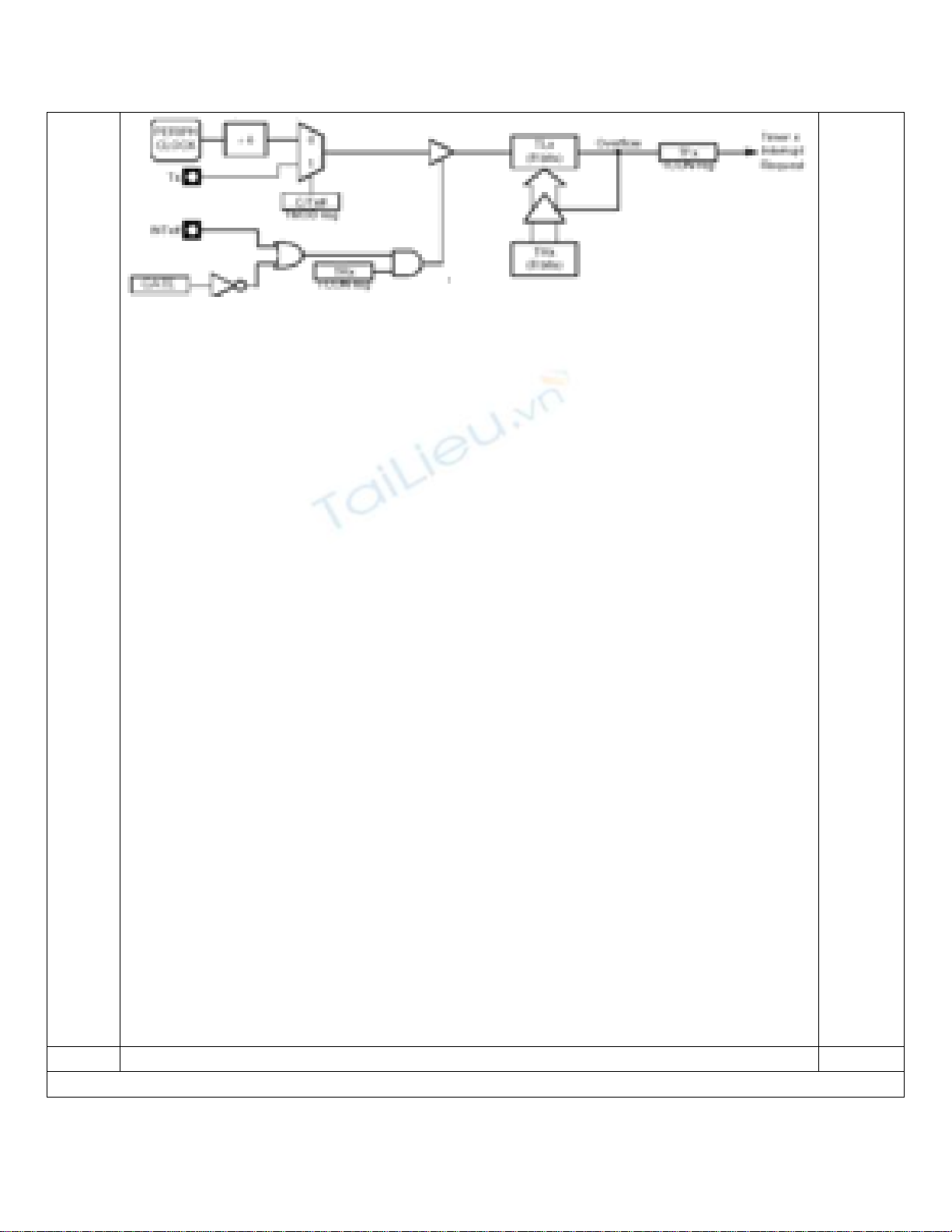

Hình trên mô tả hoạt động của các Timer ở chế độ 1: Nguồn xung clock được

đưa tới Timer phụ thuộc vào bit C-/T0 trong thanh ghi TMOD:

C-/T0 = 1, xung clock sẽ được lấy từ bộ tạo xung bên ngoài qua chân T0.

Nguồn xung clock nói trên sẽ được điều khiển để đưa tới các Timer bằng các

bit: TR0, GATE và mức logic trên các chân INT0:

Nếu TR0=0, các Timer sẽ bị cấm mà không cần quan tâm tới GATE và mức

logic trên các chân INT0 (thể hiện bằng “cổng AND”).

Nếu TR0=1, các Timer sẽ hoạt động với một trong 2 điều kiện sau xảy ra (thể

hiện bằng cổng ‘OR”): Thứ nhất: bit GATE=1; thứ hai: trên chân INT0 có

mức logic 1.

Với chế độ 1, giá trị lớn nhất mà các Timer chứa được là 65535(tương ứng

FFFF(H)), khi đếm quá giá trị này sẽ xảy ra tràn, khi cờ tràn TF0 sẽ được đặt bằng

1. Sau khi xảy ra tràn, nếu muốn Timer tiếp tục đếm từ giá trị đặt trước, chương

trình phải có câu lệnh nạp lại giá trị khởi tạo sau khi đã dừng Timer bằng cách xoá

bit TR0.

- Hoạt động counter của bộ TIMER0 trong vi điều khiển chế độ 8 bit:

0,25

0,25

0,25

0,25

osc / 12

Trong chế độ 2, bộ Timer dùng TL0 để chứa giá trị đếm và TH0 để chứa giá

trị nạp lại vì vậy chế độ này được gọi là chế độ tự nạp lại 8 bit. Sau khi đếm quá

255 sẽ xảy ra tràn, khi đó TF0 được đặt bằng 1 đồng thời giá trị của Timer tự động

được nạp lại bằng nội dung của TH0.

Hình trên mô tả hoạt động của các Timer ở chế độ 2: Nguồn xung clock được

đưa tới Timer phụ thuộc vào bit C-/T0 trong thanh ghi TMOD:

C-/T0 = 1, xung clock sẽ được lấy từ bộ tạo xung bên ngoài qua chân T0.

Nguồn xung clock nói trên sẽ được điều khiển để đưa tới các Timer bằng các

bit: TR0, GATE và mức logic trên các chân INT0:

Nếu TR0=0, các Timer sẽ bị cấm mà không cần quan tâm tới GATE và mức

logic trên các chân INT0 (thể hiện bằng “cổng AND”).

Nếu TR0=1, các Timer sẽ hoạt động với một trong 2 điều kiện sau xảy ra (thể

hiện bằng cổng ‘OR”): Thứ nhất: bit GATE=1; thứ hai: trên chân INT0 có

mức logic 1.

- Viết chương trình đếm xung chân T0 hiển thị giá trị Port 1 và Port 2:

#include <reg52.h>

void main (void)

{

TMOD =0x05;

TR0 = 1;

while (1)

{

P1=TL0;

P2=TH0;

}

}

0,25

0,25

0,25

0,25

1

Cộng(I) 7

II. Phần tự chọn, do trường biên soạn

3

C

ộng ( II )

T

ổng cộng ( I + II )

…………..,Ngày………..tháng…………năm…….

Duyệt Hội đồng thi tốt nghiệp Tiểu ban ra đề thi

![Đề thi trắc nghiệm Kỹ thuật mạch điện tử: Tổng hợp [Năm]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250920/kimphuong1001/135x160/23481758356189.jpg)

![Đề thi học kì Kỹ thuật số năm 2014-2015 – Trường Đại học Bách Khoa TP.HCM [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250813/nhanmotchut_1/135x160/97661755077479.jpg)

![Bài giảng Nhập môn Kỹ thuật điện [chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251208/nguyendoangiabao365@gmail.com/135x160/60591765176011.jpg)