GI IỚ THIỆU CHUNG VỀ HỆ THỐNG BUS

Hình 73 Hệ th ngố bus th cự

tế

6.2 GI IỚ THIỆU M TỘ SỐ LO I BUSẠ THÔNG

DỤNG

6.2.1 Bus ISA và EISA

Bus ISA (Industrial Standard Architecture) là một trong các bus đ cượ phát tri nể s mớ

nhất. Bus ISA do IBM phát tri nể năm 1981 v iớ băng thông 8 bit trên máy XT, hoặc 16 bit

trên máy AT. ISA hỗ trợ t iố đa 6 thiết bị kết n iố đ ngồ th iờ và hoạt động ở các xung nh pị 4,

6 và 8MHz. Hình 74 minh hoạ các khe cắm mở rộng của bus ISA đ cượ dùng để kết n iố

v iớ các card m r ngở ộ ISA.

Hình 74 Khe cắm m rở ộng

ISA

Bus EISA là m tộ mở r ngộ c aủ bus ISA ra đ iờ vào năm 1988. EISA hỗ trợ băng thông 32

bits, nh ngư nó vẫn t ngươ thích v iớ các thiết bị theo chuẩn ISA 8 và 16 bit. EISA hoạt

động v i ớxung nh pị 8.33MHz và đạt t cố độ truyền dữ liệu 33MB/s. Hình 75 minh hoạ các

khe cắm m r ngở ộ c aủ bus EISA đ cượ dùng để kết n iố v iớ các card mở rộng ISA và

EISA. Hiện nay, bus ISA và EISA đã lạc hậu và không còn

đ cượ

s dử ụng.

Hình 75 Khe cắm m rở ộng

EISA

6.2.2 Bus PCI

6.2.2.1 Giới thi u busệ

PCI

Bus PCI (Peripheral Component Interconnect) do Intel phát tri nể năm 1993 và

đ cượ

phát

tri n thànhể m tộ trong các bus

đ cượ

sử dụng rộng rãi nhất cho đến ngày nay. P C

I

hỗ

trợ

b ă n g

thông 32 bit ho ặ c 64 bit và đ ạ t t

cố đ trộ u

y ề n d li u kháữ ệ

ca o theo t ầ n s lố à m

v

i ệ c và b ă n g thô n

g . V i bớăng thông 32 bit, t cố độ truyền dữ liệu đạt 133 MB/s t iạ t nầ

số 33MHz và 266 MB/s t iạ t n sầ ố 66MHz. V iớ băng thông 64 bit, t cố độ truyền dữ liệu

đạt 266 MB/s tại t nầ số 33MHz và

533 MB/s t iạ t nầ số 66MHz. Hình 76 minh hoạ khe cắm PCI và card mở r ngộ thiết bị PCI

và

Hình 77 minh hoạ bus c cụ b ộPCI – các thành phần tham gia vào “gia đình”

PCI.

Hình 76 Khe cắm và card thiết bị PCI

74

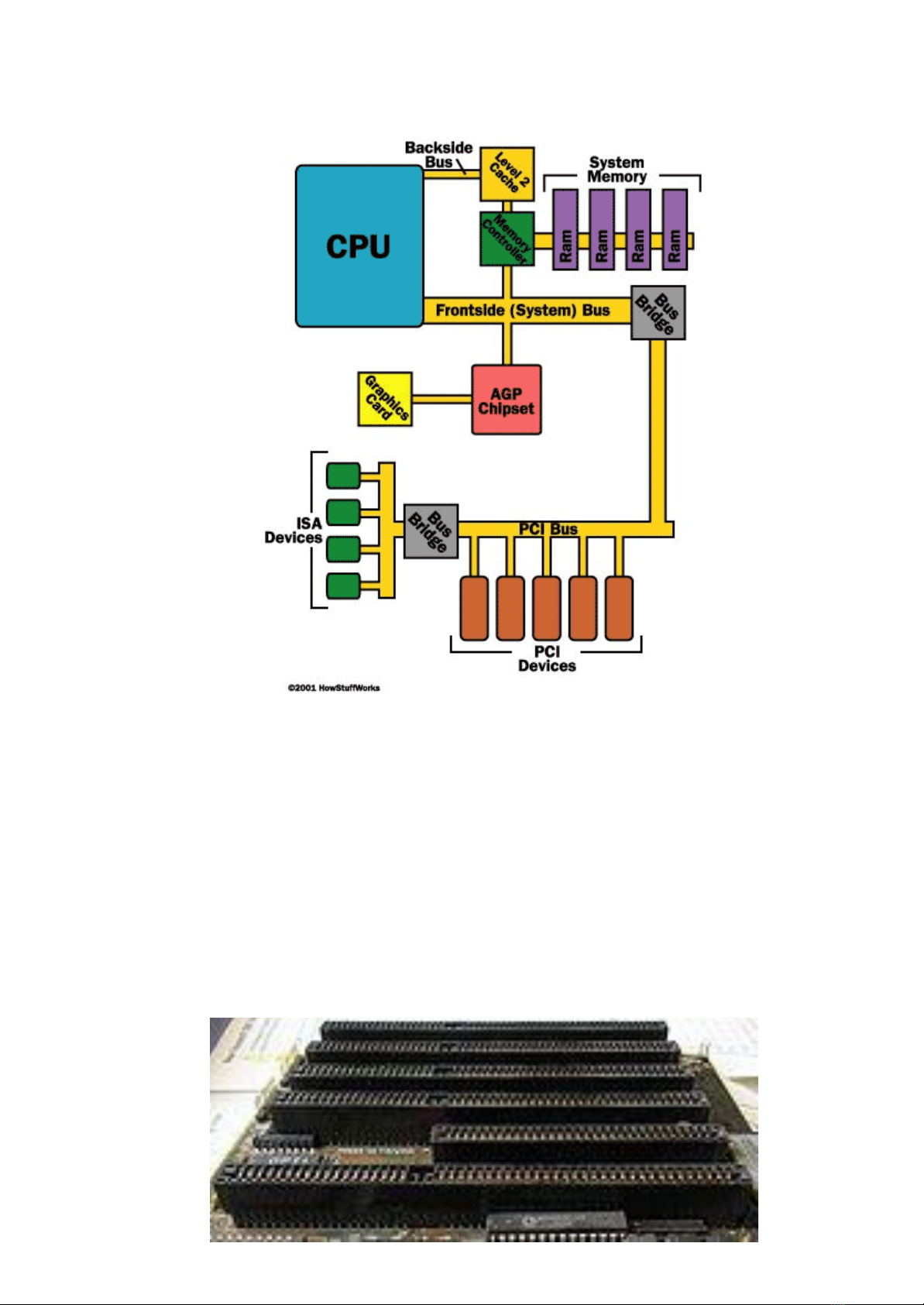

Hình 77 Bus cục b ộPCI

6.2.2.2 Nguyên lý ho t đ ng ạ ộ c aủ bus

PCI

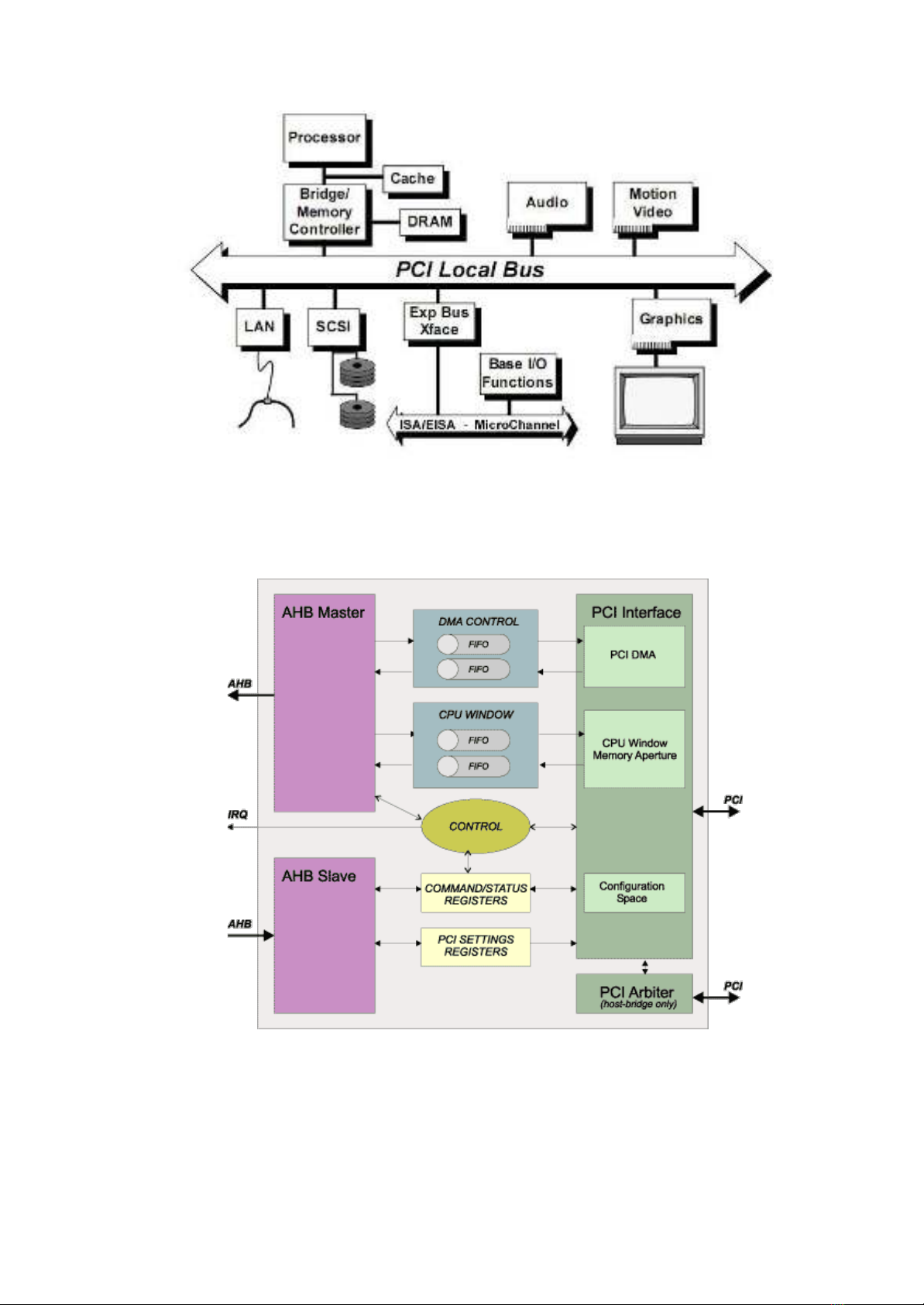

Hình 78 S đ kh i nơ ồ ố guyên lý hoạt đ ng ộc aủ bus

PCI

Hình 78 nêu sơ đồ kh iố nguyên lý hoạt đ ngộ c aủ bus PCI. Theo đó PCI là m tộ bus dùng

chung hay bus chia sẻ (shared bus). PCI hỗ trợ nhi uề thiết bị kết n iố đồng th i,ờ

nh ngư

t iạ

m i th iỗ ờ đi m,ể chỉ có m tộ cặp thiết bị

đ cượ

sử dụng bus để trao đ iổ dữ liệu. Việc trao

đ iổ dữ liệu trên bus PCI

đ cượ

th cự hi nệ thông qua các giao d chị (transaction). Thiết bị kh iở

t oạ (Initiator)

quá trình truyền dữ liệu đ cượ g iọ là thiết bị chủ (ABH Master) và thiết bị nhận dữ liệu

hay

![Đề kiểm tra trắc nghiệm môn Mạng máy tính: Tổng hợp [Năm]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260423/hoangvuong.030705@gmail.com/135x160/4931777024115.jpg)