Full name : Tr n Văn Hùngầ

Class : Bio-medical engineering

Homework #4

1. Learn by heart the logic symbol and characteristic table of the basic sequential logic

components: SR latch (set reset active high), SR latch (set, reset active low), gated SR

latch, gated D latch, SR FF, JK FF, D FF, TFF.

2. (60 points) Using the Quatus II software and perform the following tasks:

a. Draw the circuit on slide 2/48 using schematic editor tool. Run the simulation of the

circuit. Print the screenshot of the simulation result.

b. Describe the 4 bit-2 to 1 multiplexer using VHDL. Run the simulation. Print the

screenshot of the simulation result.

c. Describe the structure of the circuit on slide 2/84 using VHDL. Run the simulation.

Print the screenshot of the simulation result.

3. (40 points)

a. Thi t k m ch t h p v i đu vào X là các s nh phân 4 bit không d u và đu ra làế ế ạ ổ ợ ớ ầ ố ị ấ ầ

các s nh phân 3 bit là giá tr làm tròn xu ng c a đu vào X chia cho 2. Ví d n u ố ị ị ố ủ ầ ụ ế

k t qu phép chia là 3.5 thì s làm tròn là 3. Bi u di n m ch đã thi t k d i d ngế ả ẽ ể ễ ạ ế ế ướ ạ

t ng c a tích đã rút g n s d ng ph ng pháp bìa Karnaugh, không ph i v m ch ổ ủ ọ ử ụ ươ ả ẽ ạ

logic.

b. Thi t k m ch câu a s d ng VHDLế ế ạ ở ử ụ

1

Solution

2.

a.

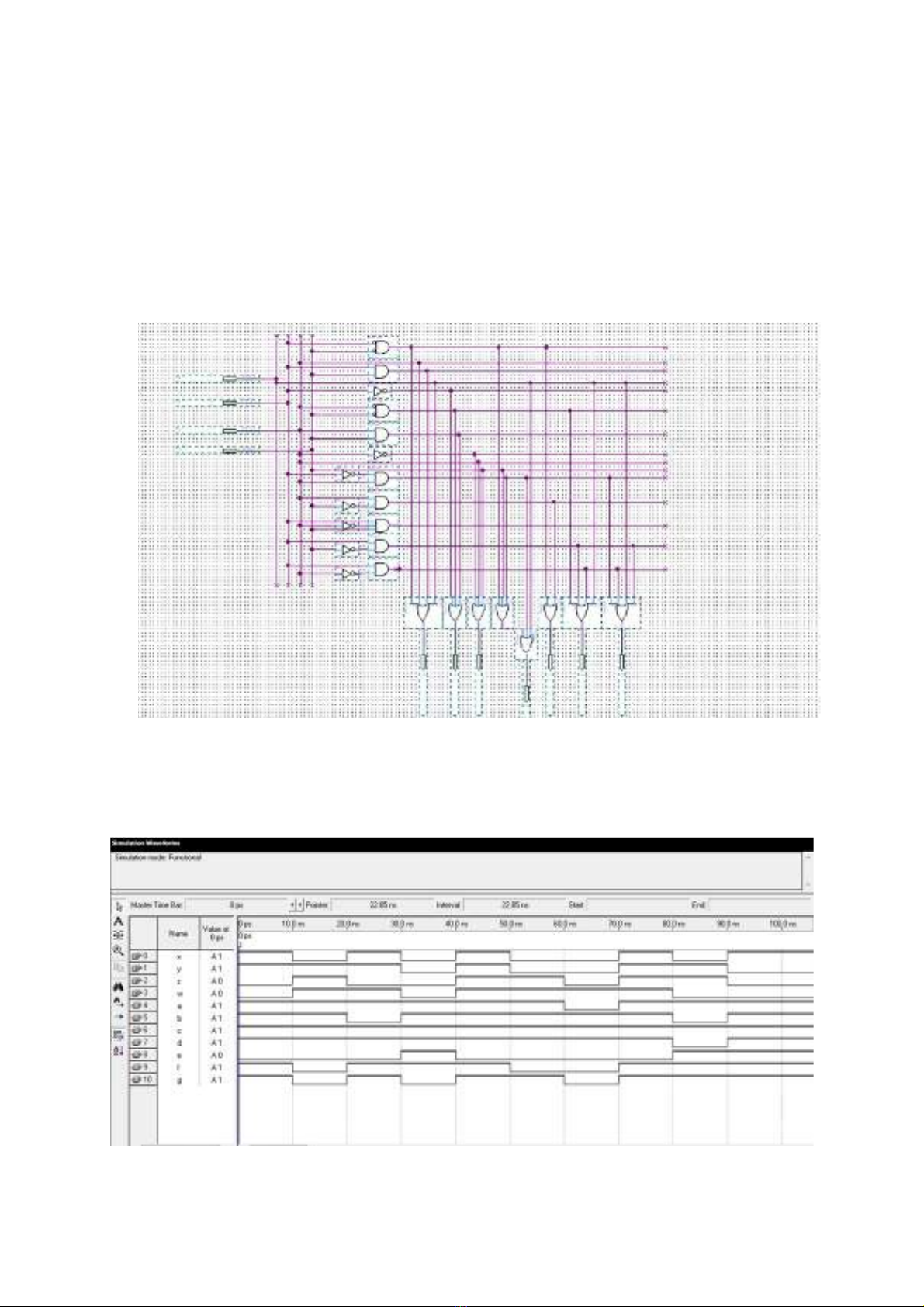

The schematic diagram for the circuit on slide 2/48

The simulation result

2

b.

Describe the 4 bit-2 to 1 multiplexer using VHDL

Method 1:

Entity MUX21_4bit is

Port (A, B: in std_logic_vector(3 down to 0);

S: in std_logic;

F: out std_logic(3 down to 0));

End MUX21_4bit;

Architecture behave of MUX21_bit is

Begin

F <= A when S = ‘o’ else B;

End behave;

Method 2:

Entity MUX21_4bit is

Port (A, B : in std_logic_vector (3 down to 0);

S : in std_logic

F: out std_logic(3 down to 0));

End MUX21_4bit;

Architecture behave of MUX21_4bit is

Component A,B,S: in std_logic;

F: out std_logic);

End Component;

Gate 1: MUX 21 port map ( A(0), B(0), S, F(0));

Gate 2: MUX 21 port map ( A(1), B(1), S, F(1));

Gate 3: MUX 21 port map ( A(2), B(2), S, F(2));

Gate 4: MUX 21 port map ( A(2), B(2), S, F(2));

End behave;

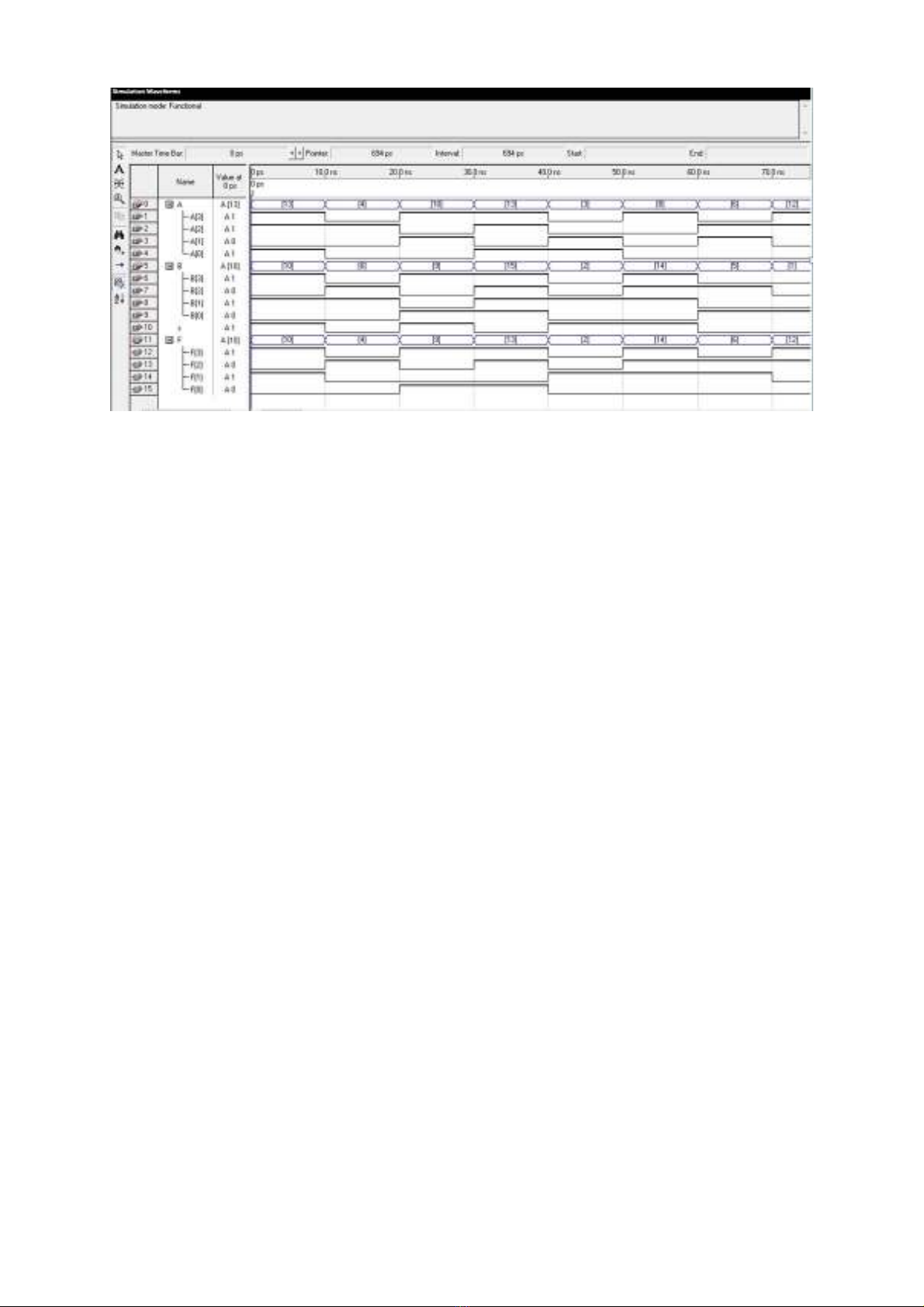

The simulation result

3

c.

Describe the structure of the circuit on slide 2/84 using VHDL

Entity BCD2LED is

Port ( BCD: in std_logic_vector (3 down to 0);

LED: out std_logic_vector(6 down to 0);

End BCD2LED;

Architecture behave of BCD2LED is

Begin

Process (BCD)

Begin

Case BCD is

When “0000” => LED <=”1111110”

When “0001” => LED <=”0110000”

When “0010” => LED <=”1101101”

When “0011” => LED <=”1111001”

When “0100” => LED <=”0110011”

When “0101” => LED <=”1011011”

When “0110” => LED <=”1011111”

When “0111” => LED <=”1110000”

When “1000” => LED <=”1111111”

When “1001” => LED <=”1111011”

When others => LED <= ”-------”

End case;

End process;

End behave;

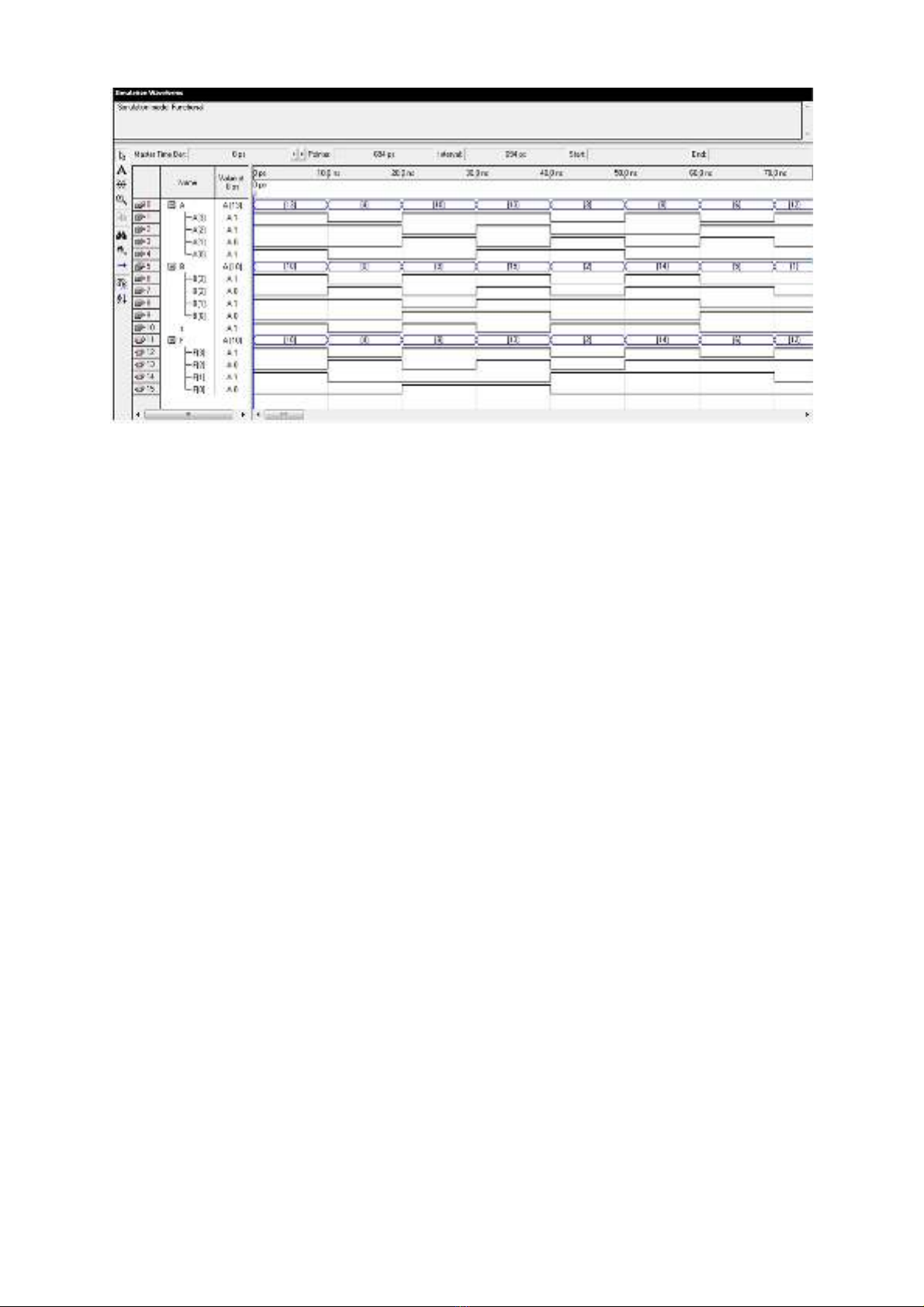

The simulation result

4

5

![Giáo trình Vô tuyến điện viên hàng hải GMDSS hạng tổng quát: Phần 1 [Chuẩn Nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260504/vispacex_27/135x160/45101777969769.jpg)