Biên soạn: Võ Kỳ Châu – Bộ môn Điện tử, Khoa Điện – Điện tử

Email: vkchau@dee.hcmut.edu.vn

1

13

Kỹ thuật số cơ bản

13-1 Khái niệm tín hiệu số

13-1-1 Định nghĩa tín hiệu tương tự

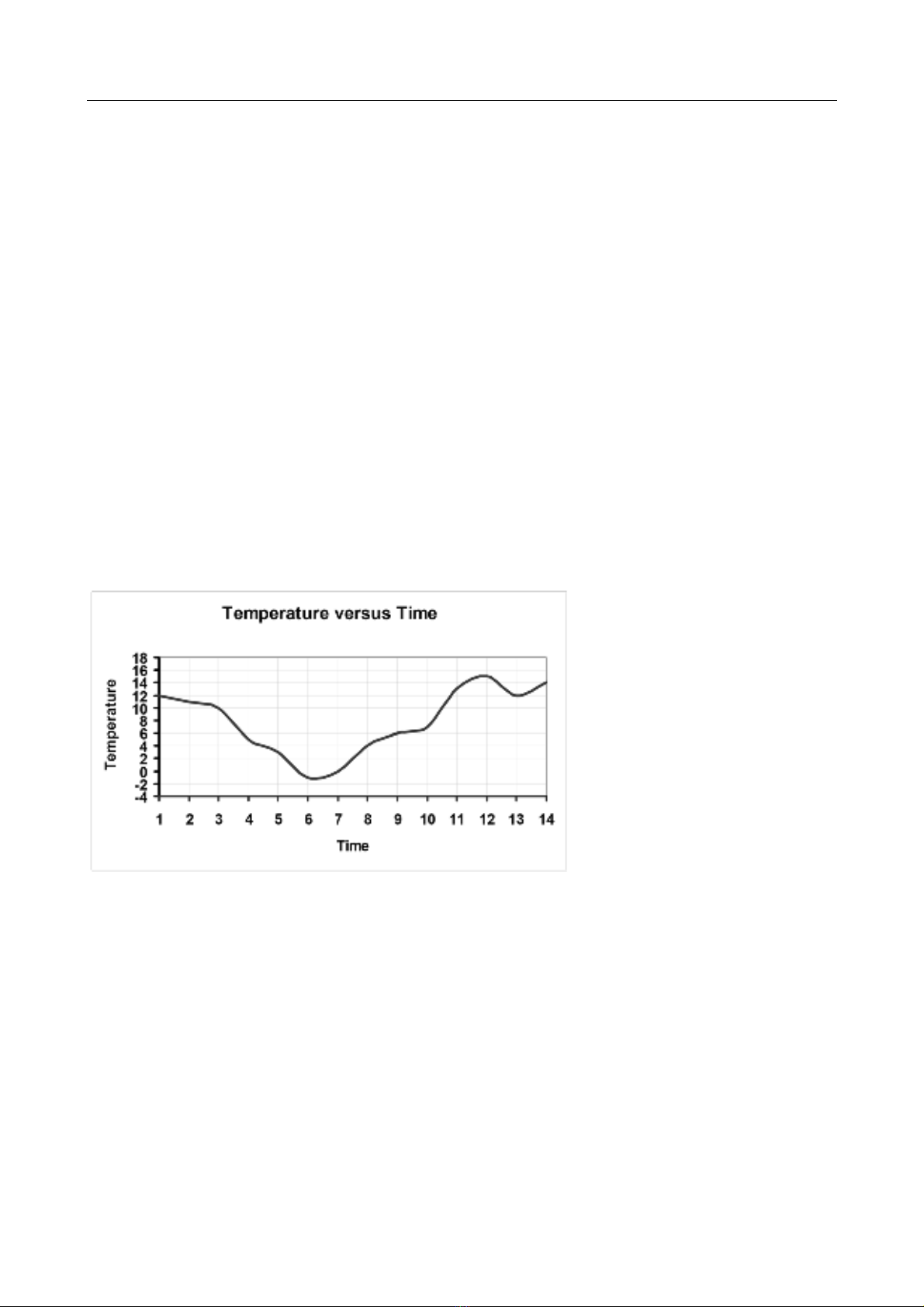

Tín hiệu tương tự (analog signal) là tín hiệu có các giá trị liên tục theo thời gian. Hình 13-1

biểu diễn sự thay đổi của nhiệt độ theo thời gian, sự thay đổi này là liên tục, do đó tín hiệu nhiệt độ

là tín hiệu tương tự.

13-1-2 Định nghĩa tín hiệu số

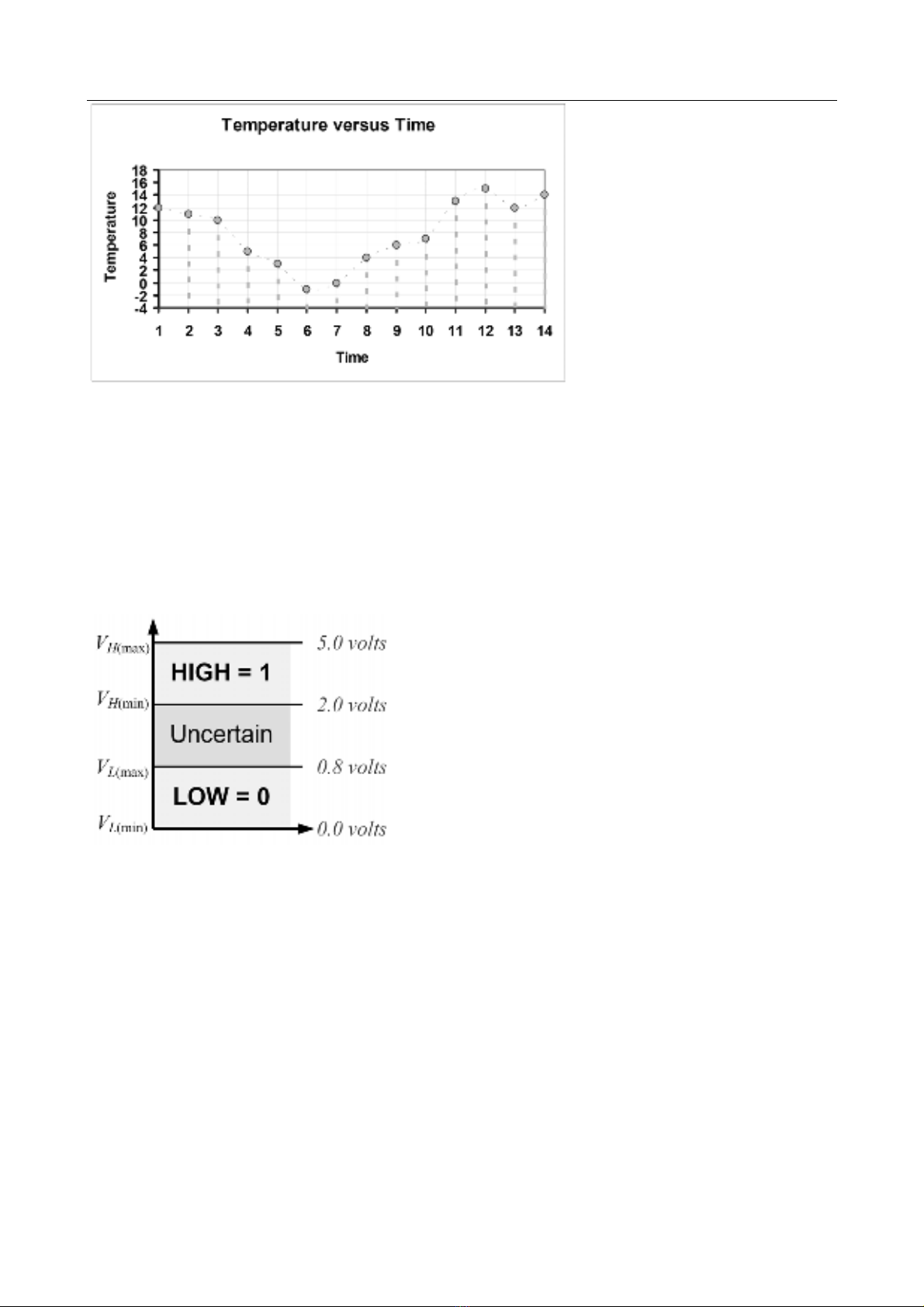

Tín hiệu số (digital signal) là tín hiệu có tập hợp các giá trị là rời rạc. Tín hiệu số thường được

tạo ra từ tín hiệu tương tự thông qua quá trình lấy mẫu và lượng tử hóa. Hình 13-2 minh họa tín

hiệu số được tạo ra bằng cách lấy mẫu tín hiệu tương tự trong hình 13-1.

Hình 13-1

Tín hiệu tương tự.

Biên soạn: Võ Kỳ Châu – Bộ môn Điện tử, Khoa Điện – Điện tử

Email: vkchau@dee.hcmut.edu.vn

2

13-1-3 Hệ thống nhị phân và các mức điện áp

Các số trong hệ thống nhị phân, thường gọi là số nhị phân, được tạo nên chỉ từ hai chữ số 0 và

1. Hai chữ số này được gọi là các bit. Trong mạch số, hai mức điện áp khác nhau sẽ được dùng để

biểu diễn hai bit này. Bit 1 thường được biểu diễn bằng mức điện áp cao HIGH và bit 0 được biểu

diễn bằng mức điện áp thấp LOW.

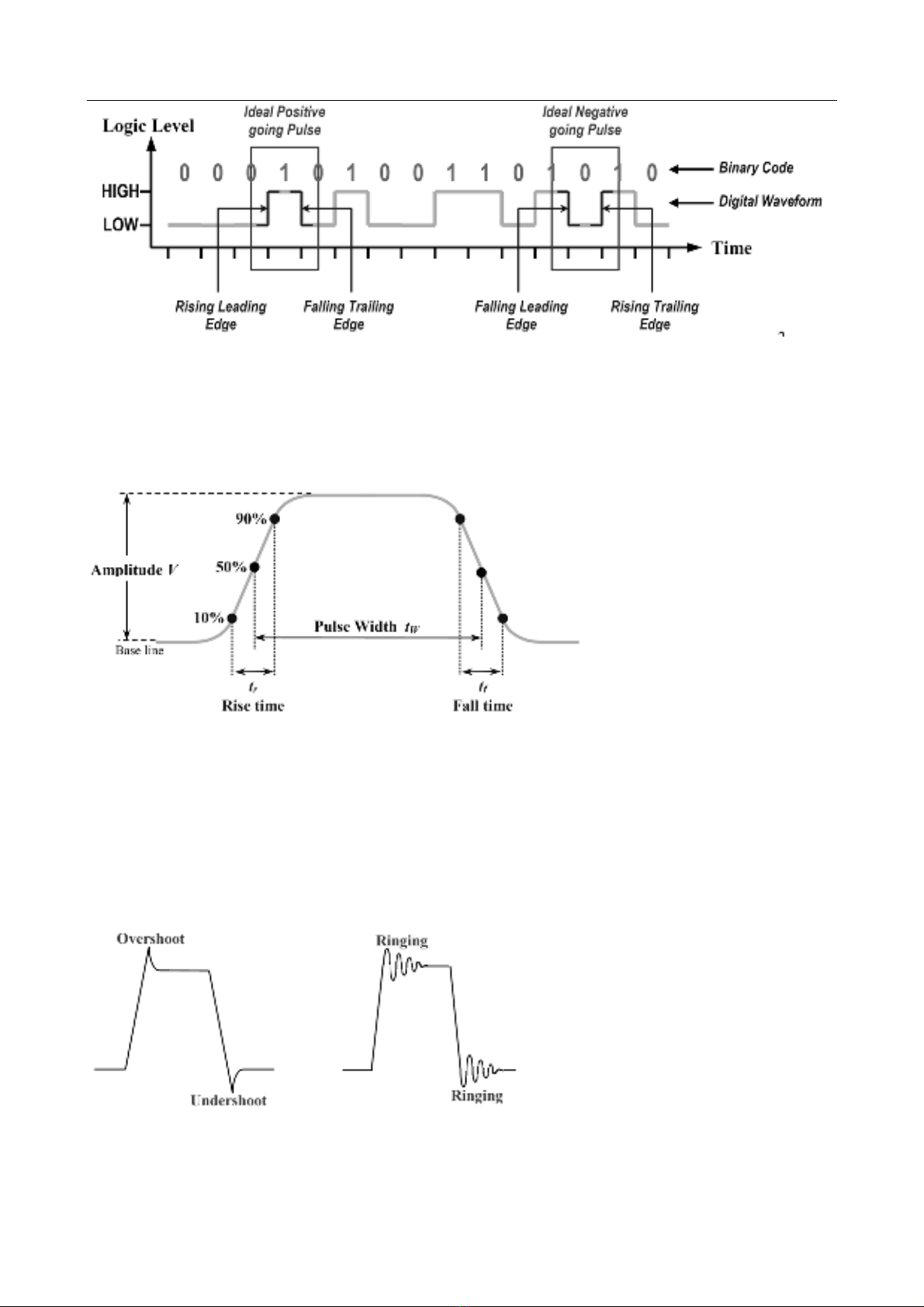

13-1-4 Mức logic

Giá trị điện áp dùng để biểu diễn hai bit 0 và 1 được gọi là mức logic, một mức điện áp biểu

diễn trạng thái HIGH, một mức biểu diễn trạng thái LOW. Trong thực tế, một tầm điện áp sẽ xác

định một mức logic chứ không phải một giá trị điện áp duy nhất. Ta thử xét sơ đồ trong hình 13-3.

Trong sơ đồ này, mức HIGH tương ứng với các giá trị điện áp từ

2 V

(

(min)H

V) đến 5 V

(

(max)H

V

) và mức LOW tương ứng với các giá trị điện áp từ 0 V (

(min)L

V

) đến 0.8 V (

(max)L

V

). Nếu

điện áp rơi vào khoảng 0.8 V đến 2 V , mức logic là không xác định. Đây là tầm điện áp không

được xuất hiện trong các thiết kế số.

13-1-5 Dạng sóng số

Dạng sóng số là dạng tín hiệu trong các mạch số. Dạng sóng này bao gồm sự chuyển đổi giữa

hai mức logic, HIGH và LOW, trong một khoảng thời gian. Hình 13-4 là ví dụ của một dạng sóng

số.

Hình 13-3

Sơ đồ mức logic.

Hình 13-2

Tín hiệu số được tạo ra từ tín

hiệu tương tự trong hình 13-1.

Biên soạn: Võ Kỳ Châu – Bộ môn Điện tử, Khoa Điện – Điện tử

Email: vkchau@dee.hcmut.edu.vn

3

Vị trí tín hiệu chuyển từ LOW sang HIGH được gọi là cạnh lên của tín hiệu (Rising Leading

Edge). Vị trí tín hiệu chuyển từ HIGH sang LOW được gọi là cạnh xuống của tín hiệu (Falling

Leading Edge). Dạng sóng này là dạng sóng lý tưởng vì trong thực tế thời gian cạnh lên và cạnh

xuống không bao giờ bằng không. Hình 13-5 cho thấy dạng sóng trong thực tế của tín hiệu số.

Trong dạng sóng này, khoảng thời gian khi tín hiệu tăng từ 10% đến 90% giá trị lớn nhất được

gọi là thời gian lên (rise time), tương tự, thời gian khi tín hiệu giảm từ 90% xuống 10% được gọi là

thời gian xuống (fall time). Thời gian lên và thời gian xuống là hai thông số không thể bỏ qua trong

thực tế khi xét cạnh lên và cạnh xuống của tín hiệu số. Tuy nhiên, trong trường hợp độ rộng xung

(pulse width) lớn hơn rất nhiều so với thời gian lên và thời gian xuống, ta có thể xem tín hiệu số

xấp xỉ tín hiệu lý tưởng.

Bên cạnh sự không lý tưởng của tín hiệu tại cạnh lên và cạnh xuống, một số đặc điểm khác có

thể xuất hiện trên dạng sóng của tín hiệu số như overshoot, undershoot, và ringing như trong hình

13-6.

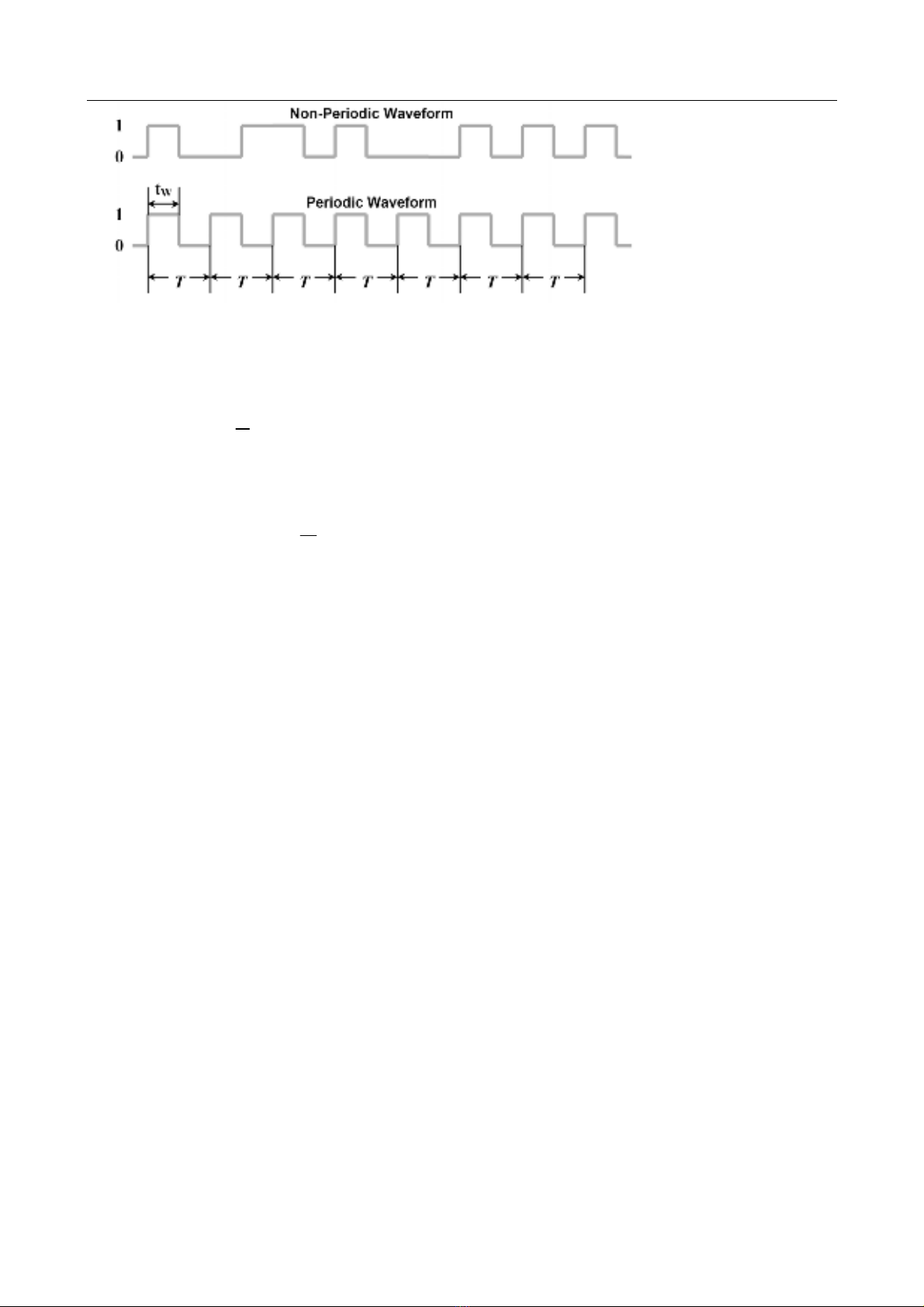

Tín hiệu số có thể là tín hiệu tuần hoàn hoặc không tuần hoàn. Hình 13-7 minh họa hai trường

hợp này.

Hình 13-6

Minh họa một số khả năng có thể

xảy ra trong dạng sóng tín hiệu số.

Hình 13-5

Dạng sóng số trong thực tế.

Hình 13-4

Dạng sóng lý tưởng của tín hiệu số.

Biên soạn: Võ Kỳ Châu – Bộ môn Điện tử, Khoa Điện – Điện tử

Email: vkchau@dee.hcmut.edu.vn

4

Trong hình trên,

T

là chu kỳ của tín hiệu tuần hoàn, do đó tần số của tín hiệu số tuần hoàn này

là

1

fT

=

(13-1)

Duty cycle của tín hiệu tuần hoàn được định nghĩa bằng tỉ số của độ rộng xung

W

t

và chu kỳ

của tín hiệu T.

(%)

w

t

Duty cycle T

=

(13-2)

13-1-6 Mạch tích hợp số

Thông thường các mạch logic thường có sẵn dưới dạng mạch tích hợp (IC – Integrated

Circuit). IC được dùng nhiều trong các hệ thống số vì kích thước nhỏ, độ ổn định và tin cậy cao, giá

thành thấp.

IC thường được tạo nên từ một thanh bán dẫn silicon, sau đó đặt vào trong một lớp vỏ

(package) bằng plastic. Các linh kiện bán dẫn trên thanh silicon được nối ra ngoài package bằng các

dây kim loại mỏng tạo nên các chân linh kiện. IC loại này được gọi là monolithic IC, trong đó, tất

cả các thành phần tạo nên mạch như điện trở, transistor, diode, tụ điện đều là một phần tích hợp từ

một thanh silicon duy nhất.

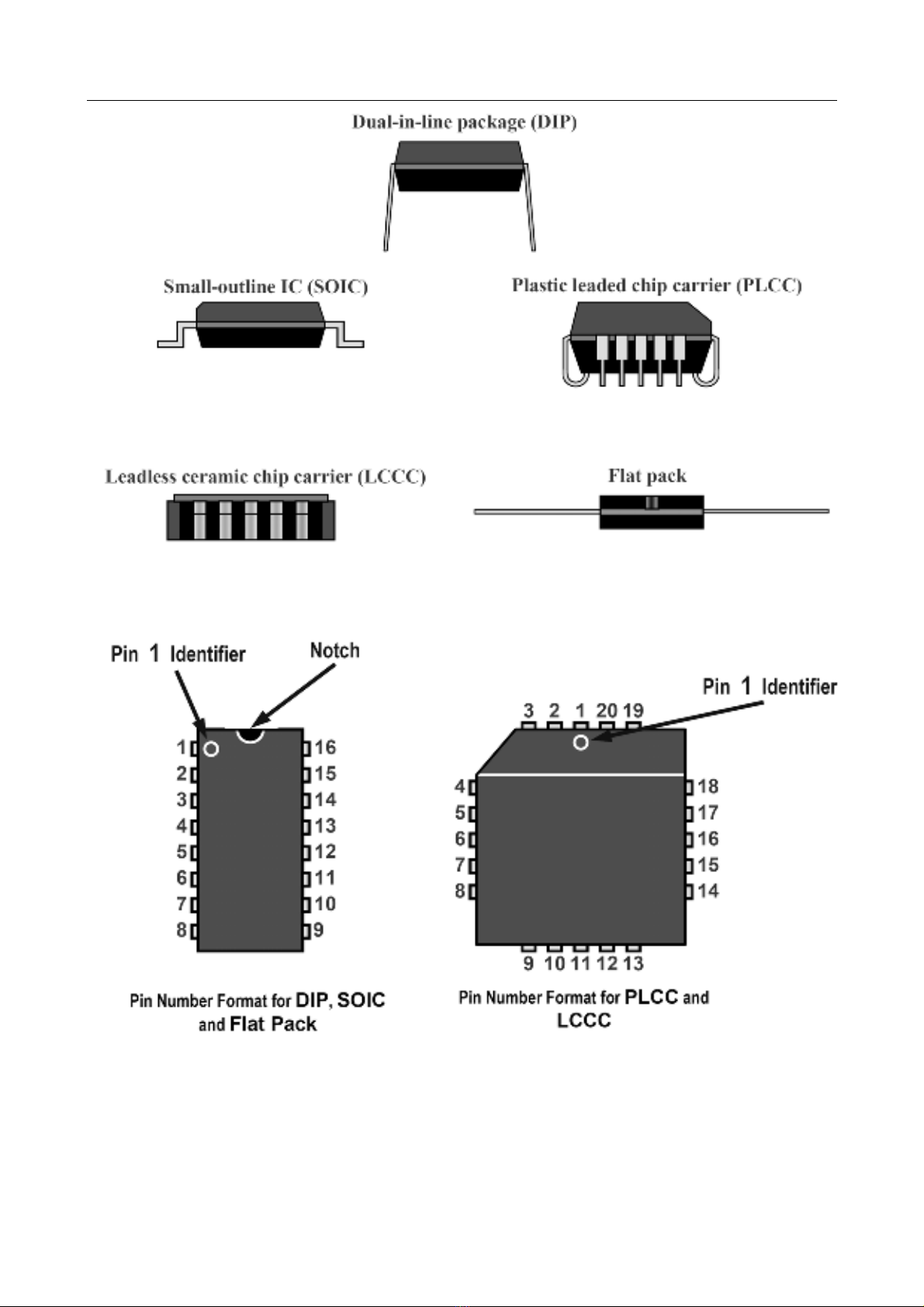

Các IC package thường có hình dạng rất khác nhau, tuy nhiên có thể chia thành hai loại: gắn

xuyên lỗ (through-hole mounted) và gắn bề mặt (surface mounted) dựa vào cách thức mà package

được gắn trong một mạch điện. DIP (Dual-in-inline package) là dạng package xuyên lỗ thường gặp

nhất. Với DIP, IC được đặt trên một phía của board mạch in, các chân IC được cắm xuyên qua và

hàn ở mặt bên kia của board mạch. Đối với dạng gắn bề mặt (SMT), package thường bao gồm

nhiều loại khác nhau như: SOIC (small-outline IC), PLCC (plastic leaded chip carrier), LCCC

(leadless ceramic chip carrier), và flat pack. Hình 13-8 vẽ một số dạng package thường gặp.

Hình 13-7

Tín hiệu số không tuần hoàn (hình trên) và tuần hoàn (hình dưới).

Biên soạn: Võ Kỳ Châu – Bộ môn Điện tử, Khoa Điện – Điện tử

Email: vkchau@dee.hcmut.edu.vn

5

Mỗi dạng package sẽ có một qui tắc để đánh số chân cho IC. Hình 13-9 minh họa qui tắc này.

IC còn được phân loại dựa vào độ phức tạp của nó. Việc phân loại này dựa vào số cổng chứa

trong một IC. Ta có một số dạng như sau

SSI – Small-Scale Integration: có từ 1 – 11 cổng. Ví dụ như các cổng cơ bản, flip-flop,…

Hình 13-9

Qui tắc đánh số thứ tự chân cho các loại package.

Hình 13-8

Một số dạng package thường gặp.

![Đặc tính cơ bản của sợi quang: Tổng quan [chuẩn SEO]](https://cdn.tailieu.vn/images/document/thumbnail/2015/20150507/tung_utc/135x160/1754814_048.jpg)

![Bài giảng công tắc tơ [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260506/vispacex_27/135x160/93891778142285.jpg)

![Giáo trình Điện tử tương tự 1: Phần 1 [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260506/vispacex_27/135x160/69111778210056.jpg)