LUAÄN VAÊN TOÁT NGHIEÄP GVHD : TRAÀN VAÊN TROÏNG

ÖÙng duïng vi maïch soá laäp trình Trang 40

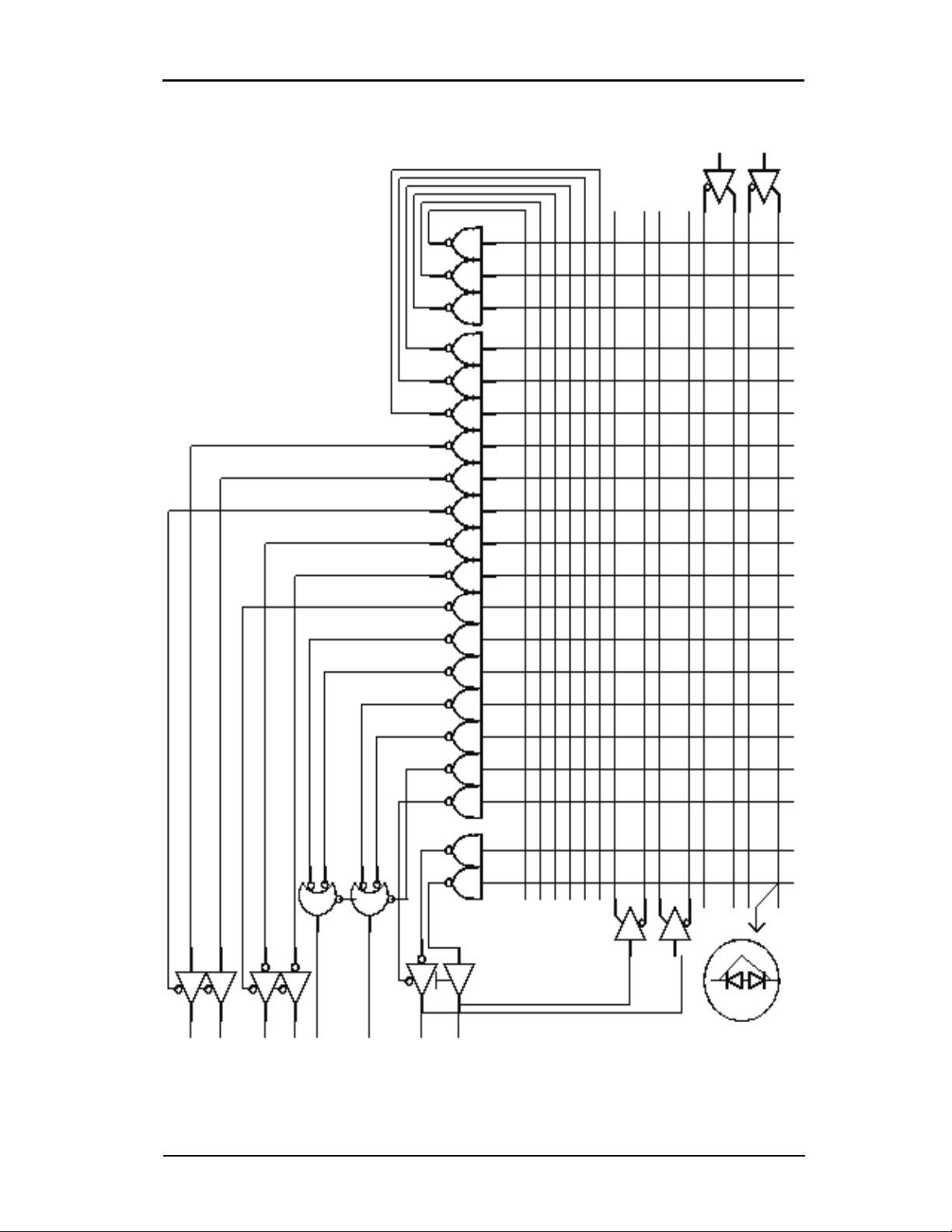

Hình 3.12 . Sô ñoà logic khoái caáu truùc ñieàu khieån EPLD EP900

OE/ CLK

Caáu truùc ñieàu khieån

Vaøo/ra

Clock

ñoàng boä

39

38

37

36

35

34

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

7

6

5

4

3

2

71

70

69

68

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

4

3

2

1

0 1 2 3 4 5

6 7

CLEAR

LUAÄN VAÊN TOÁT NGHIEÄP GVHD : TRAÀN VAÊN TROÏNG

ÖÙng duïng vi maïch soá laäp trình Trang 41

9. Hoï vi maïch PML ( Programmable Macro Logic).

Hoï vi maïch ñöôïc coâng ty Signetics söû duïng caáu truùc môùi goïi laø “foldback”

(gaáp veà). Maïch logic “foldback” söû duïng moät coång NAND ñôn hay maûng NOR

keát hôïp vôùi moät caáu truùc lieân keát laäp trình trung taâm cho pheùp thöïc hieän nhieàu

möùc logic khaùc nhau ñeå lieân keát vôùi macro ngoû vaøo vaø ngoû ra. Nhö trong hoï vi

maïch PML, moät maûng NAND ñöôïc söû duïng vì coång NAND coù toác ñoä truyeàn

nhanh nhaát trong coâng ngheä löôõng cöïc.

Töø khoùa macro ñeå tham khaûo moät khoái chöùc naêng vaø coù theå xaùc ñònh moät

tín hieäu ngoû vaøo, moät coång ñeäm ngoû ra hay baát cöù moät haøm logic naøo nhö FF,

maïch ñeám hay maïch toå hôïp. Coâng ty Signetics phaân loaïi caùc macro nhö sau:

ngoû vaøo laø macro ngoû vaøo, macro ngoû ra vaø nhöõng khoái chöùc naêng khaùc nhö

thanh ghi hay maïch toå hôïp thì goïi laø macro chöùc naêng. Macro cuûa hoï ML moâ taû

ôû hình 3.13. So vôùi caáu truùc maûng AND – OR cuûa caùc hoï IC PAL vaø FPLA thì

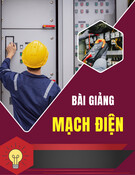

caáu truùc maûng NAND phöùc taïp hôn. Ñeå ñôn giaûn cho vieäc tìm hieåu, xeùt ví duï

sau:

Hình 3.14 a trình baøy moät maïch logic ñôn giaûn söû duïng caáu truùc AND – OR

cuûa hoï vi maïch PAL vaø hình 3.14 b söû duïng caáu truùc NAND – NAND vôùi chöùc

naêng töông töï nhöng coù öu ñieåm laø khoâng bò giôùi haïn vôùi caùc haøm coù hôn 2 caáp

logic. Maëc khaùc, caáu truùc cuûa PML taän duïng toái ña caùc coång logic vaø caùc khaû

naêng hoaït ñoäng cuûa vi maïch.

Ví duï nhö ôû hoï PAL vaø FPLA khi caàn theâm moät bieán ôû ngoû vaøo seõ choïn

ñöôøng tín hieäu ngoû ra xem nhö moät ñöôøng tín hieäu ngoû vaøo, do ñoù seõ laøm taêng

thôøi gian truyeàn vaø laõng phí moät ngoû ra. Ñoái vôùi hoï PML thì taát caû caùc ngoû vaøo

cuûa coång NAND ñöôïc söû duïng nhö laø ngoû vaøo cuûa tín hieäu vaø caùc haøm logic

ñöôïc thöïc hieän vôùi caáu truùc 3 caáp logic. Vi maïch ñaïi dieän cho hoï PML laø PLHS

501 coù caáu taïo goàm 72 coång NAND trong ñoù coù 44 coång NAND ñöôïc duøng ñeå

hoã trôï cho macro ngoû ra. Vi maïch coù 24 ngoû vaøo, 8 coång ñeäm XOR ôû ngoû ra vôùi

4 coång taùc ñoäng ôû möùc thaáp , coù 4 coång taùc ñoäng ôû möùc cao vaø coù 8 ñöôøng döõ

lieäu 2 chieàu. Vi maïch coù 52 chaân vôùi kieåu chaân theo daïng PLCC. Hình 3.15

trình baøy caáu truùc cuûa PLHS 501 .

Caùc coång ñeäm ngoû ra 3 traïng thaùi ñöôïc ñieàu khieån baèng töøng coång NAND

rieâng ñeå taïo neân tính linh hoaït trong thieát keá.

LUAÄN VAÊN TOÁT NGHIEÄP GVHD : TRAÀN VAÊN TROÏNG

ÖÙng duïng vi maïch soá laäp trình Trang 42

Maûng NAND MxN

Hình 3.13 . Sô ñoà logic laäp trình macro

a) b)

Hình 3.14. Maïch logic söû duïng caáu truùc “ flodback”

Ngoû

vaøo

macro

1

Ngoû ra

macro

0

Ngoû ra

macro

0

Haøm

macro

LUAÄN VAÊN TOÁT NGHIEÄP GVHD : TRAÀN VAÊN TROÏNG

ÖÙng duïng vi maïch soá laäp trình Trang 43

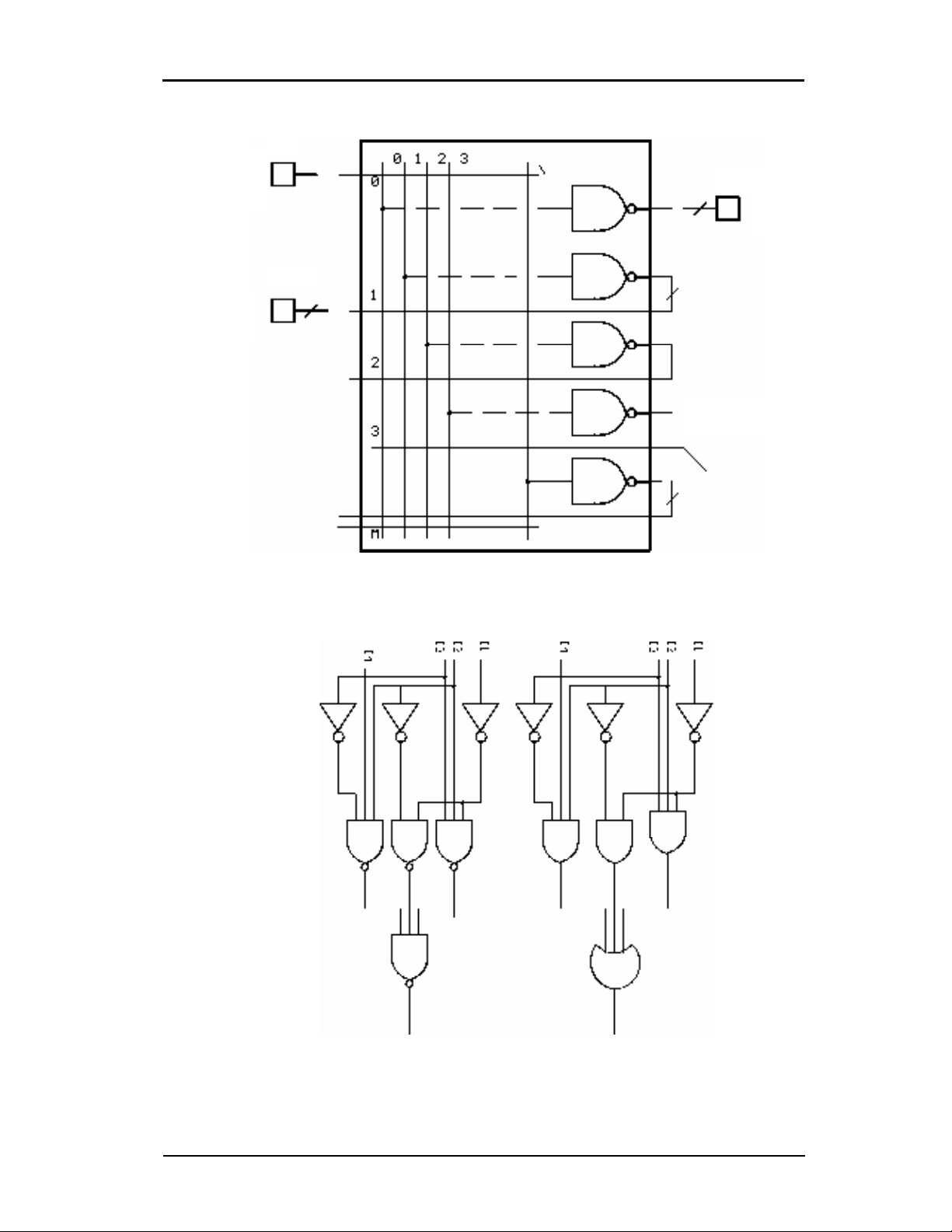

Hình 3.15 . Maïch laät RS vaø D söû duïng caáu truùc PML

b) Maïch laät D

a) Maïch laät RS

LUAÄN VAÊN TOÁT NGHIEÄP GVHD : TRAÀN VAÊN TROÏNG

ÖÙng duïng vi maïch soá laäp trình Trang 44

Hình 3.16. Sô ñoà chöùc naêng PLS 501

I23 . . I0

I

71

70

.

.

.

.

.

0

1

![PROFIBUS và mạng truyền thông: Tổng quan, ứng dụng [Năm hiện tại]](https://cdn.tailieu.vn/images/document/thumbnail/2019/20191208/camtucau99/135x160/9551575800543.jpg)

![Thiết bị công nghệ nào ngốn điện nhất? [Top thiết bị ngốn điện]](https://cdn.tailieu.vn/images/document/thumbnail/2012/20121217/bibocumi21/135x160/1315182_0610.jpg)

![Bài giảng Nhập môn Kỹ thuật điện [chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251208/nguyendoangiabao365@gmail.com/135x160/60591765176011.jpg)

![Bài giảng Cảm biến và ứng dụng: Chương 1 - Các khái niệm và đặc trưng cơ bản [Chuẩn SEO]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251204/kimphuong1001/135x160/51101764832169.jpg)