PVP_bk3i1_k50

M C L C :Ụ Ụ

L I M Đ UỜ Ở Ầ

Ngày nay công ngh vi đi n t đã tr thành m t lĩnh v c phát tri n và đ c r t nhi u cácệ ệ ử ở ộ ự ể ượ ấ ề

n c trên th gi i chú tr ng phát tri n.T i sao nó l i đ c chú tr ng đ n v y,xét v ph mướ ế ớ ọ ể ạ ạ ượ ọ ế ậ ề ạ

vi ng d ng ta th y h Nhúng có liên quan, nh h ng đ n nhi u lĩnh v c trong đ i s ng.ứ ụ ấ ệ ả ưở ế ề ự ờ ố

Trong sinh ho t c a con ng i,nó làm cho cu c s ng c a con ng i ngày càng ti nạ ủ ườ ộ ố ủ ườ ệ

nghi,tho i mái.s xu t hi n hàng lo t các thi t b ph c v nhu c u đ i s ng c a con ng iả ự ấ ệ ạ ế ị ụ ụ ầ ờ ố ủ ườ

không ch tăng v s l ng mà còn tăng v tính năng,ch t l ng và đ an toàn nh máyỉ ề ố ượ ề ấ ượ ộ ư

gi t,t l nh,lò vi sóng…ặ ủ ạ

Trong s n xu t,nó làm tăng năng su t lao đ ng,gi m s c lao đ ng c a con ng i,thayả ấ ấ ộ ả ứ ộ ủ ườ

con ng i ho t đ ng nh ng n i có đi u ki n h t s c kh c nhi t…Và nó liên quan đ nườ ạ ộ ở ữ ơ ề ệ ế ứ ắ ệ ế

các ng d ng công ngh cao nh ứ ụ ệ ư vũ tr …ụ

V i t m quan tr ng c a công ngh vi đi n t .Nó x ng đáng là lĩnh v c mang t m chi nớ ầ ọ ủ ệ ệ ử ứ ự ầ ế

l c trong s phát tri n c a các n c trên th gi i.N c ta cũng không ngo i l ,vi c xácượ ự ể ủ ướ ế ớ ướ ạ ệ ệ

đ nh đ c t m quan tr ng đó.Nhà n c cũng u tiên trong đ u t ,vi c h c,nghiênị ượ ầ ọ ướ ư ầ ự ệ ọ

c u.Nhi u c s và trung tâm nghiên c u đã và đang ho t đ ng ,phát tri n.ứ ề ơ ở ứ ạ ộ ể

V i sinh viên tr ng kĩ thu t thì đây là nghành h c đ y ti m năng.Nhi u cu c thi, nhi uớ ườ ậ ọ ầ ề ề ộ ề

công trình nghiên c u khoa h c ph c v cho vi c h c và nghiên c u đã ra đ i,nh m m cứ ọ ụ ụ ệ ọ ứ ờ ằ ụ

đích phát tri n s h c h i,s sáng t o,t duy,g n li n v i th c ti n.ể ự ọ ỏ ự ạ ư ắ ề ớ ự ễ

Theo yêu c u c a mô h c cũng nh đ s d ng thành th o công ngh FPGA em đã quy tầ ủ ọ ư ể ử ụ ạ ệ ế

đ nh ch n đ tài :ị ọ ể

“Thi t k b x lý hình nh qu ng cáo trên n n LED matrix s d ng FPGA”. ế ế ộ ử ả ả ề ử ụ

N i dung đè tài :ộ

Tìm hi u v LED matrixể ề

Tìm hi u v FPGAể ề

Tìm hi u ph n m m h tr thi t k xilinx ISE ể ầ ề ỗ ợ ế ế

Thi t k h th ngế ế ệ ố

Vì đây là trong khuôn kh bài t p l n, nên em ch thi t k trên mô hình thíổ ậ ớ ỉ ế ế

nghi m, s d ng ngôn ng VHDL đ mô hình hóa h th ng ph n c ng . Em xin chânệ ử ụ ữ ể ệ ố ầ ứ

thành cám n th y LÊ H I SÂM đã h ng d n chi ti t v FPGA và ph ng pháp thi tơ ầ Ả ướ ẫ ế ề ươ ế

k mô hình hóa ph n c ng.ế ầ ứ

Hà N i, ngày 30-10-2009ộ

Sinh viên th c hi n : ự ệ

Ph m Văn Phongạ

PVP_bk3i1_k50

CH NG I Đ T V N Đ VÀ NHI M V C A Đ ÁNƯƠ Ặ Ấ Ề Ệ Ụ Ủ Ồ

CH NG 1 :ƯƠ I – Đ t v n đặ ấ ề

Trong th i đ i ngày nay, khoa h c công ngh ngày càng phát tri n và đ c ngờ ạ ọ ệ ể ượ ứ

d ng r t nhi u trong th c t . Trong đó thì các lĩnh v c nh gi trí, d ch v qu ng cáoụ ấ ề ự ế ự ư ả ị ụ ả

khu ch tr ng s n ph m đ thu hút s chú ý c a các doanh nghi p cũng nh cá nhânế ươ ả ầ ể ự ủ ệ ư

ngày càng phát tri n m nh m . Đ làm cho s n ph m ho c hình nh công ty thu hút sể ạ ẽ ể ả ầ ặ ả ự

chú ý, quan tâm c a khách hàng thì d ch v qu ng cáo ph i th t n t ng, choáng ng p,ủ ị ụ ả ả ậ ấ ượ ợ

b t m t… Đ gi i quy t v n đ này thì có r t nhi u ph ng án, nh ng hi n nayắ ắ ể ả ế ấ ề ấ ề ươ ư ệ

ph ng án mà đ c các gi i kinh doanh s d ng hi u qu nh t là dùng b ng led matrix.ươ ượ ớ ử ụ ệ ả ấ ả

V i nh ng x lý hình nh s ng đ ng, màu s c n t ng đã là s l a ch n hàng đ u choớ ữ ử ả ố ộ ắ ấ ượ ự ự ọ ầ

các nhà kinh doanh. Do đó, thi t k h th ng b ng đi n t đ ph c v nhu c u qu ngế ế ệ ố ả ệ ử ể ụ ụ ầ ả

cáo, khu ch tr ng hình nh c a hàng, doanh nghi p, công ty là r t c n thi t. ế ươ ả ử ệ ấ ầ ế

II – Nhi m v c a đ án ệ ụ ủ ồ

V i s l a ch n đ tài này, tr c tiên em c n ph i tìm hi u chi ti t v LEDớ ự ự ọ ể ướ ầ ả ể ế ề

matrix cũng nh các ph ng pháp quét LED, hi n th x lý hình nh…Sau đó tìm hi uư ươ ể ị ử ả ể

các ph ng pháp ng d ng FPGA đ gi i quy t bài toán đ t ra. Vì gi i h n c a đ tàiươ ứ ụ ể ả ế ặ ớ ạ ủ ể

ch th c hi n mô ph ng và hi u cách th c ho t đ ng, ph ng pháp l p trình s d ngỉ ự ệ ỏ ể ứ ạ ộ ươ ậ ử ụ

FPGA cùng v i th i gian th c hi n ít nên em ch gi i quy t bài toán d i d ng mô hình,ớ ờ ự ệ ỉ ả ế ướ ạ

hi v ng khi có th i gian và đi u ki n thì em có th tri n khai ng d ng th c t .ọ ờ ề ệ ể ể ứ ụ ự ế

CH NG II C S LÝ THUY TƯƠ Ơ Ở Ế

CH NG 2 :ƯƠ I - LED Matrix

D a trên nguyên t c nh quét màn hình,ta có th th c hi n vi c hi n th ma tr n đènự ắ ư ể ự ệ ệ ể ị ậ

b ng cách quét theo hang và quét theo c t.M i Led trên ma tr n Led có th coi nh m tằ ộ ỗ ậ ể ư ộ

đi m nh.Đ a ch c a m i đi m nh này đ c xác đ nh đ ng th i b i m ch gi i mãể ả ị ỉ ủ ỗ ể ả ượ ị ồ ờ ở ạ ả

hang và gi i mã c t,đi m nh này s đ c xác đ nh nh d li u đ a ra t b đi đi uả ộ ể ả ẽ ượ ị ờ ữ ệ ư ừ ộ ề

khi n.ể

Nh v y t i m i th i đi m ch có tr ng thái c a m t đi m nh xác đ nh.Tuy nhiên khiư ậ ạ ỗ ờ ể ỉ ạ ủ ộ ể ả ị

xác đ nh đ a ch và tr ng thái c a đi m nh ti p theo thì các đi m nh còn l i s chuy nị ị ỉ ạ ủ ể ả ế ể ả ạ ẽ ể

v tr ng thái t t.Vì th đ hi n th đ c toàn b hình nh mà ta mu n thì ta ph i quétề ạ ắ ế ể ể ị ượ ộ ả ố ả

ma tr n nhi u l n v i t c đ quét r t l n,l n h n nhi u l n th i gian k p t t c aậ ề ầ ớ ố ộ ấ ớ ớ ơ ề ầ ờ ị ắ ủ

đèn.M t ng i ch nh n bi t đ c t i đa 24 hình/s do đó n u t c đ quét l n m t ng iắ ườ ỉ ậ ế ượ ố ế ố ộ ớ ắ ườ

s không nh n bi t đ c s gián đo n hay là nh p nháy c a đèn Led(đánh l a c m giácẽ ậ ế ượ ự ạ ấ ủ ừ ả

m t).ắ

M t đi u cũng quan tr ng đây là đi u ch nh đ sang c a Led,thong th ng Led sángộ ề ọ ở ề ỉ ộ ủ ườ

bình th ng đi n áp 2-3V,dòng đi n t 20-30mA.Đ đ m b o Led sáng bình th ngườ ở ệ ệ ừ ể ả ả ườ

thì yêu c u m ch thi t k ph i đáp ng đ 2 đi u ki n trên.ầ ạ ế ế ả ứ ủ ề ệ

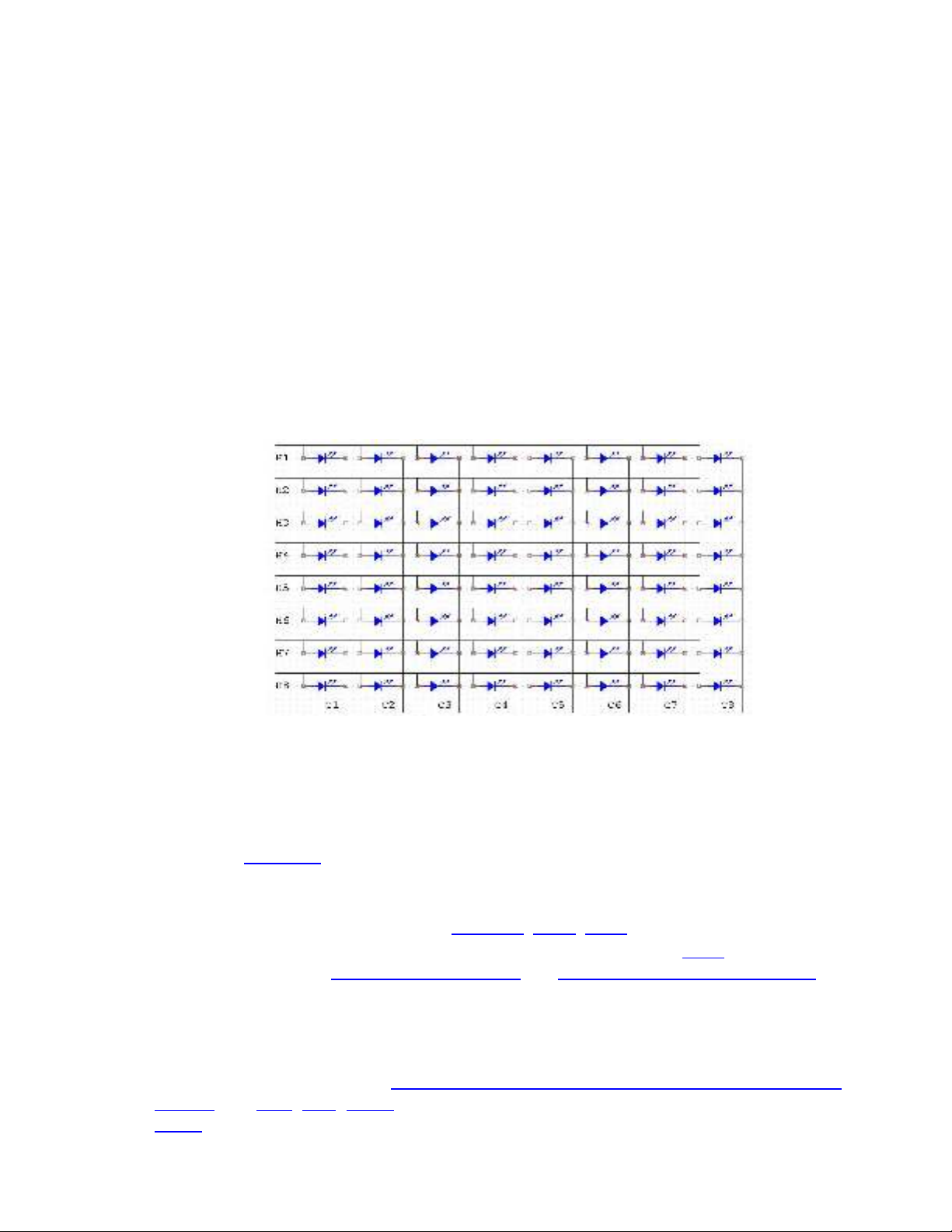

S đ kh i :ơ ồ ố

PVP_bk3i1_k50

Đ th c hi n đ c quét hang và quét c t thì ma tr n Led đ c thi t k t nh sau:ể ự ệ ượ ộ ậ ượ ế ế ư

Tr ng thái c a m t Led s đ c quy t đ nh b i tín hi u đi n áp đi vào đ ng th i c 2ạ ủ ộ ẽ ượ ế ị ở ệ ệ ồ ờ ả

chân.đ Led sáng thì ta ph i c p đi n áp phù h p vào chân d ng c a Led(chân Anot),cònể ả ấ ệ ợ ươ ủ

chân catot thì n i đ t.Đèn t t khi ta không c p ngu n cho Led ho c đ 2 đ u anot và catotố ấ ắ ấ ồ ặ ể ầ

cung m c đi n áp.ở ứ ệ

Ta có s đ m ch nguyên lý c a Led 8x8:ơ ồ ạ ủ

CH NG 3 :ƯƠ II – FPGA

Field-programmable gate array (FPGA) là vi mach dùng c u trúc m ng ph n t logic màấ ả ầ ử

ng i dùng có th l p trình đ c. (Ch ườ ể ậ ượ ữ field đây mu n ch đ n kh năng tái l p trìnhở ố ỉ ế ả ậ

“bên ngoài” c a ng i s d ng, không ph thu c vào dây chuy n s n xu t ph c t p c aủ ườ ử ụ ụ ộ ề ả ấ ứ ạ ủ

nhà máy bán d n). Vi m ch FPGA đ c c u thành t các b ph n:ẫ ạ ượ ấ ừ ộ ậ

•Các kh i logicố c b n l p trình đ c (ơ ả ậ ượ logic block)

•H th ng m ch liên k t l p trình đ cệ ố ạ ế ậ ượ

•Kh i vào/ra (ốIO Pads)

•Ph n t thi t k s n khác nh ầ ử ế ế ẵ ư DSP slice, RAM, ROM, nhân vi x lý...ử

FPGA cũng đ c xem nh m t lo i vi m ch bán d n chuyên d ng ượ ư ộ ạ ạ ẫ ụ ASIC, nh ng n u soư ế

sánh FPGA v i nh ng ớ ữ ASIC đ c ch hoàn toànặ ế hay ASIC thi t k trên th vi n logicế ế ư ệ thì

FPGA không đ t đ c m c đ t i u nh nh ng lo i này, và h n ch trong kh năngạ ựợ ứ ộ ố ư ư ữ ạ ạ ế ả

th c hi n nh ng tác v đ c bi t ph c t p, tuy v y FPGA u vi t h n ch có th táiự ệ ữ ụ ặ ệ ứ ạ ậ ư ệ ơ ở ỗ ể

c u trúc l i khi đang s d ng, công đo n thi t k đ n gi n do v y chi phí gi m, rútấ ạ ử ụ ạ ế ế ơ ả ậ ả

ng n th i gian đ a s n ph m vào s d ng.ắ ờ ư ả ẩ ử ụ

Còn n u so sánh v i các d ng ế ớ ạ vi m ch bán d n l p trình đ c dùng c u trúc m ng ph nạ ẫ ậ ượ ấ ả ầ

t logicử nh ưPLA, PAL, CPLD thì FPGA u vi t h n các đi m: tác v tái l p trình c aư ệ ơ ể ụ ậ ủ

FPGA th c hi n đ n gi n h n; kh năng l p trình linh đ ng h n; và khác bi t quanự ệ ơ ả ơ ả ậ ộ ơ ệ

PVP_bk3i1_k50

tr ng nh t là ki n trúc c a FPGA cho phép nó có kh năng ch a kh i l ng l n ọ ấ ế ủ ả ứ ố ượ ớ c ngổ

logic (logic gate), so v i các vi m ch bán d n l p trình đ c có tr c nó.ớ ạ ẫ ậ ượ ướ

Thi t k hay l p trình cho FPGA đ c th c hi n ch y u b ng các ngôn ng mô tế ế ậ ượ ự ệ ủ ế ằ ữ ả

ph n c ng ầ ứ HDL nh ưVHDL, Verilog, AHDL, các hãng s n xu t FPGA l n nh ả ấ ớ ư Xilinx,

Altera th ng cung c p các gói ph n m m và thi t b ph tr cho quá trình thi t k ,ườ ấ ầ ề ế ị ụ ợ ế ế

cũng có m t s các hãng th ba cung c p các gói ph n m m ki u này nh ộ ố ứ ấ ầ ề ể ư Synopsys,

Synplify... Các gói ph n m m này có kh năng th c hi n t t c các b c c a toàn bầ ề ả ự ệ ấ ả ướ ủ ộ

quy trình thi t k ế ế IC chu n v i đ u vào là mã thi t k trên HDL (còn g i là mã ẩ ớ ầ ế ế ọ RTL).

1) Ki n trúc FPGAế

C u trúc t ng th c a m t FPGA đ c minh h a hình sau.ấ ổ ể ủ ộ ượ ọ ở

Kh i logic FPGAố

Ph n t chính c a FPGA là các kh i logic (ầ ử ủ ố logic block). Kh i logic đ c c u thành tố ượ ấ ừ

LUT và m t ph n t nh đ ng b ộ ầ ử ớ ồ ộ flip-flop, LUT (Look up table) là kh i logic có thố ể

th c hi n b t kì hàm logic nào t 4 đ u vào, kêt qu c a hàm này tùy vào m c đích màự ệ ấ ừ ầ ả ủ ụ

g i ra ngoài kh i logic tr c ti p hay thông qua ph n t nh flip-flop.ử ố ự ế ầ ử ớ

Trong tài li u h ng d n c a các dòng FPGA c a Xilinx còn s d ng khái ni m ệ ướ ẫ ủ ủ ử ụ ệ SLICE,

1 Slice t o thành t g m 4 ạ ừ ồ kh i logicố, s l ng các Slices thay đ i t vài nghìn đ n vàiố ượ ổ ừ ế

ch c nghìn tùy theo lo i FPGA.ụ ạ

N u nhìn c u trúc t ng th c a m ng LUT thì ngoài 4 đ u vào k trên còn h tr thêm 2ế ấ ổ ể ủ ả ầ ể ỗ ợ

đ u vào b xung t các kh i logic phân b tr c và sau nó nâng t ng s đ u vào c aầ ổ ừ ố ố ướ ổ ố ầ ủ

LUT lên 6 chân. C u trúc này là nh m tăng t c các b s h c logic.ấ ằ ố ộ ố ọ

thumb|200px|Kh i chuy n m ch c a FPGAố ể ạ ủ M ng liên k t trong FPGA đ c c u thànhạ ế ượ ấ

t các đ ng k t n i theo hai ph ng ngang và đ ng, tùy theo t ng lo i FPGA mà cácừ ườ ế ố ươ ứ ừ ạ

đ ng k t n i đ c chia thành các nhóm khác nhau, ví d trong XC4000 c a Xilinx có 3ườ ế ố ượ ụ ủ

lo i k t n i: ng n, dài và r t dài. Các đ ng k t n i đ c n i v i nhau thông qua cácạ ế ố ắ ấ ườ ế ố ượ ố ớ

kh i chuy n m chố ể ạ l p trình đ c (ậ ượ programable switch), trong m t kh i chuy n m chộ ố ể ạ

ch a m t s l ng nút chuy n l p trình đ c đ m b o cho các d ng liên k t ph c t pứ ộ ố ượ ể ậ ượ ả ả ạ ế ứ ạ

khác nhau.

Ngoài các kh i logic tùy theo các lo i FPGA khác nhau mà có các ph n t tích h p thêmố ạ ầ ử ợ

khác nhau, ví d đ thi t k nh ng ng d ng SoC, trong dòng Virtex 4,5 c a Xilinx cóụ ể ế ế ữ ứ ụ ủ

ch a nhân x lý ứ ử PowerPC, hay trong Atmel FPSLIC tích h p nhân ợARV…, hay cho nh ngữ

ng d ng x lý tín hi u s ứ ụ ử ệ ố DSP trong FPGA đ c tích h p các ượ ợ DSP Slide là b nhânộ

PVP_bk3i1_k50

c ngộ t c đ cao, th c hi n hàm A*B+C, ví d dòng Virtex c a Xilinx ch a t vài ch cố ộ ự ệ ụ ủ ứ ừ ụ

đ n hàng trăm ếDSP slices v i A, B, C 18-bit.ớ

2) ngôn ng VHDLữ

Thi t k hay l p trình cho FPGA đ c th c hi n ch y u b ng các ngôn ng mô tế ế ậ ượ ự ệ ủ ế ằ ữ ả

ph n c ng ầ ứ HDL nh ưVHDL, Verilog, AHDL.. .Em quy t đ nh ch n ngôn ng VHDL đế ị ọ ữ ể

l p trình cho FPGA. ậ

VHDL (VHSIC Hardware Description Laguage) lµ mét ng«n ng÷ ®−îc dïng ®Ó m« t¶

c¸c hÖ thèng ph n c ngầ ứ ®iÖn tö sè. Nã ®−îc ch−¬ng tr×nh quèc gia vÒ c¸c m¹ch tÝch hîp

tèc ®é rÊt cao - VHSIC (Very High Speed Integrated Circuits) do chÝnh phñ Mü khëi

x−íng vµo ®Çu nh÷ng n¨m 1980. C¸c c«ng ty tham gia ch−¬ng tr×nh VHSIC nhËn thÊy

r»ng hä cÇn ph¶i cã mét c«ng cô nµo ®ã ®Ó thiÕt kÕ c¸c gi¶n ®å ®Çu vµo cho c¸c IC

chuyªn dông cì lín, vµ hä ®· ®Ò xuÊt viÖc lËp ra mét ng«n ng÷ m« t¶ phÇn cøng dïng ®Ó

m« t¶ cÊu tróc vµ chøc n¨ng cña c¸c m¹ch tÝch hîp (cßn ®−îc gäi lµ IC - Integrated

Circuits).

KÓ tõ ®ã, VHDL ra ®êi vµ ®−îc ph¸t triÓn, råi sau ®ã ®−îc HiÖp héi c¸c kü s− §iÖn

vµ §iÖn tö - IEEE (Institude of Electrical and Electronic Engineers) chÊp nhËn coi nh− lµ

tiªu chuÈn t¹i Mü. Phiªn b¶n ®Çu tiªn lµ Tiªu chuÈn IEEE 1076-1987 (cßn ®−îc gäi lµ

VHDL-87). Phiªn b¶n nµy ®−îc bæ sung söa ®æi n¨m 1993 thµnh IEEE 1076-1993 (cßn

®−îc gäi lµ VHDL-93).

* M« t¶ cÊu tróc

Mét hÖ thèng ®iÖn tö sè cã thÓ ®−îc m« t¶ thµnh c¸c khèi - cßn gäi lµ module víi

c¸c ®Çu vµo vµ ®Çu ra. C¸c gi¸ trÞ ®iÖn ë ®Çu ra cã mèi quan hÖ víi c¸c gi¸ trÞ trªn c¸c

®Çu vµo. H×nh 2.16a biÓu diÔn mét vÝ dô nh− vËy. Khèi F cã hai ®Çu vµo A vµ B, vµ

cã mét ®Çu ra Y. Sö dông ng«n ng÷ VHDL ®Ó m« t¶ khèi F, th× ta gäi khèi F lµ mét thùc

thÓ (entity) thiÕt kÕ, vµ c¸c ®Çu vµo vµ ®Çu ra lµ c¸c cæng (port). Cã mét c¸ch ®Ó m«

t¶ chøc n¨ng cña khèi F, ®ã lµ chóng ta m« t¶ c¸c khèi con (sub-module) thµnh phÇn cña

nã. Mçi mét khèi con ®−îc gäi lµ mét tËp hîp (instance) cña mét sè thùc thÓ, vµ c¸c cæng

cña c¸c tËp hîp ®ã ®−îc nèi l¹i b»ng c¸c ®−êng tÝn hiÖu (signal).

H×nh d iướ m« t¶ khèi F lµ mét tËp hîp gåm c¸c thùc thÓ G, H vµ I. KiÓu m« t¶ nµy ®−îc

gäi lµ m« t¶ cÊu tróc (structural). C¸c thùc thÓ G, H vµ I còng ®−îc m« t¶ theo cÊu tróc

t−¬ng tù nh− vËy.

(a) Khèi F cã hai ®Çu vµo vµ mét ®Çu ra; (b) Khèi F gåm cã 3 thùc thÓ G, H, I

* M« t¶ ho¹t ®éng

![Ăn cắp tư duy thiết kế từ mẫu quảng cáo: Tài liệu [chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250308/lbdarkprince/135x160/173_tai-lieu-an-cap-tu-duy-thiet-ke-tu-nhung-mau-quang-cao.jpg)

![Giáo trình Phối cảnh trong thiết kế quảng cáo, minh họa (Ngành Thiết kế đồ họa Trung cấp) - Trường Cao đẳng Xây dựng số 1 [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2024/20240624/gaupanda039/135x160/9351719229809.jpg)

![Bài giảng thiết kế poster quảng cáo [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2022/20221212/hoabingan205/135x160/1731670826655.jpg)

![Đề cương bài giảng Mỹ thuật đại cương [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250715/kimphuong1001/135x160/30821752564027.jpg)