Thiết kế mạch tổ hợp

Nguyễn Quốc Cường – 3i

Nội dung

• Một số quy ñịnh khi viết tài liệu • Biểu ñồ thời gian của các mạch • Các PLD tổ hợp • Các mạch mã hóa • Các mạch giải mã • Multiplexer • So sánh • Các mạch số học

Combinational logic design 2

Tài liệu tham khảo

• Digital Design: Principles & Practices – John F

Wakerly – Printice Hall

Combinational logic design 3

Một số quy ñịnh khi viết tài liệu

• Sơ ñồ khối • Ký hiệu các gate • Mức tích cực cho các chân

Combinational logic design 4

Sơ ñồ khối

• Thể hiện các khối chức năng chính của hệ

thống

• Không quá chi tiết • Cố gắng thể hiện trong một trang

Combinational logic design 5

Combinational logic design 6

Combinational logic design 7

Ký hiệu các gate

Combinational logic design 8

các ký hiệu tương ñương sử dụng ñịnh lý DeMorgan

Combinational logic design 9

Mức tích cực cho các chân

• Thường quy ñịnh nếu có “vòng tròn nhỏ” ñể chỉ

tích cực mức thấp

• Nếu không có “vòng tròn nhỏ” thì hiểu là tíchc

cực mức cao

Combinational logic design 10

• (a): nếu cả hai input = HIGH thì output = HIGH • (b): nếu cả hai input = HIGH thì output = LOW • (c): nếu cả hai input = LOW thì output = LOW

Combinational logic design 11

• Tín hiệu:

– Nếu có hậu tố _L thì hiểu là tích cực ở mức thấp – Nếu không có haụa tố _L thì hiểu là tích cực ở mức

cao

Combinational logic design 12

Biểu ñồ thời gian

• Biễu diễn hoạt ñộng của các tín hiệu là hàm của

thời gian

• Sử dụng các mũi tên ñể chỉ quan hệ “nhân-quả”

của các tín hiệu trong mạch

Combinational logic design 13

Combinational logic design 14

Mạch logic tổ hợp PLD

• PLD: Programmable Logic Device • Loại PLD ñầu tiên ñược gọi là PLA

(Programmable Logic Arrays): – Mạch logic tổ hợp 2 tầng AND-OR – ðặc trưng bởi: • Số inputs: n • Số output: m • Số các tích: p (thường p nhỏ hơn rất nhiều 2^n) – Tổng hợp các hàm logic theo kiểu tổng các tích

Combinational logic design 15

Combinational logic design 16

• input nối với một buffer ñể tạo ra:

– chính tín hiệu input (buffer) – bù của input (inverter)

• Các dây tín hiệu ñước nối sẵn trong mạch • X : dùng ñể ký hiệu nơi có thể thiết lập các kết

nối hay không thông qua các cột chì

• Các input của tầng AND khi ñể hở (không nối

với buffer) sẽ ñược thiết lập là HIGH

• Các input của tầng OR khi ñể hở (không nối với output của tầng AND) sẽ ñược thiết lập là LOW

Cách thể hiện khác của PALs

Combinational logic design 17

Combinational logic design 18

ðể thực hiện các hàm logic

ðể thực hiện các output là hằng số

Combinational logic design 19

Combinational logic design 20

• ðể output = const = 0 nên sử dụng phương

pháp O2 hơn là O3: – Khi tất cả input thay ñổi ñồng thời, O3 có khả năng sẽ

chuyển 0 (cid:1)1(cid:1)0 (glitch)

Combinational logic design 21

PALs

• PALs: Programmable Array Logic: – Chỉ có mảng AND là programmable – Mảng OR là fixed

• Phổ biến nhất là PAL16L8:

– 64 hàng, 32 cột, 32 x 64 = 2048 cột chì – Mỗi AND gate có 32 input ứng với 16 biến và phần bù

của các biến (cid:1) PAL 16L8

– 8 AND gate liên kết với một pin:

• 7 AND gate ñược nối với 7 input của một cổng OR • AND thứ 8 ñược nối với output-enable gate, nếu AND = 1 thì

output mới ñược ñưa ra pin

Combinational logic design 22

Combinational logic design 23

• PAL16L8 chỉ thực hiện ñược các hàm tổng của

7 tích hoặc ít hơn

• Trong sơ ñồ chân của PAL16L8: có 20 pin

– 2 pin cho VCC và GND – 10 pin cho I1 ñến I10 – 8 pin cho O1 ñến O8 – ðặc biệt: chân O2 ñến O7 là shared: • Input • Output

Combinational logic design 24

PLD với công nghệ bipolar

Combinational logic design 25

• Hàng ñầu: các mạch open-collector ñược nối

với nhau (cid:1) thực hiện chức năng như một mảng AND: – Chỉ một output của buffer là pull-low thì cả cột ñó sẽ

có mức LOW

– Các cột nối với một mạch ñảo (cid:1) gộp lại như một

mảng NAND

• Tương tự cho mảng thứ hai (cid:1) NAND • Với cấu trúc NAND-NAND có tác dụng giống

như AND-OR

Combinational logic design 26

• ðể tạo sự kết nối với các cột (cid:1) sử dụng một cột

chì nhỏ

• Cột chì sẽ ñược ñốt nóng và làm bốc hơi khi

thiết lập một ñiện áp cỡ 20V ñến 30V

Combinational logic design 27

PLD với công nghệ CMOS

Combinational logic design 28

• Việc ñặt cột chì cho các phần tử ñược thực hiện

ngay tại bước chế tạo IC: – không linh hoạt, cần ñặt hàng với nhà sản xuất IC – hợp với các ứng dụng có số lượng sản phẩm lớn • ðể linh hoạt hơn (cid:1) sử dụng EPLD (Erasable

Programmable Logic Device)

Combinational logic design 29

EPLD

Combinational logic design 30

• Cực thả nổi (floating gate) của MOS transistor:

– Bao quanh bởi các chất cách ñiện – Ban ñầu không có ñiện tích (cid:1) MOS transistor hoạt ñộng bình

thường:

connected

• nếu input = LOW (cid:1) n-MOS transistor sẽ “off” • nếu input = HIGH (cid:1)n-MOS transistor sẽ “on”

• Khi có ñiện áp cao ñặt vào nonfloating gate:

– floating gate sẽ nhiễm ñiện tích âm do tác dụng của ñiện trường

mạnh

– ñiện tích âm vẫn bị giữ lại tại floating gate khi bỏ ñiện áp cao – ñiện tích âm tại floating gate (cid:1) ngăn cản hoạt ñộng của MOS

transistor:

disconnected

• nếu input = LOW (cid:1) MOS transistor “off” • nếu input = HIGH (cid:1) MOS transistor sẽ vẫn “off”

Combinational logic design 31

• ðể xóa trạng thái “disconnected”:

– Thiết lập ñiện áp trên nonfloating gate ñiện áp cao và ngược dấu (cid:1) ñiện tích trên floating gate sẽ phóng

Combinational logic design 32

Các bộ giải mã (decoder) • Giải mã: biến ñổi mã ở input sang một mã khác

ở output: – n input (cid:1) 2n mã tổ hợp, m output (cid:1) 2m mã tổ hợp – Thường n < m – Bộ giải mã sử dụng nhiều:

• Mỗi tổ hợp input sẽ ứng với một bit trong m bit output

Combinational logic design 33

• Chân EN (Enable):

– Tích cực: các từ mã input sẽ ñược ánh xạ ñến các từ

mã output

– Không tích cực: tất cả các từ mã input ñều ñược gán

ñến một từ mã duy nhất ở ñầu ra

Combinational logic design 34

74x139

Combinational logic design 35

Combinational logic design 36

Combinational logic design 37

74x138

Combinational logic design 38

Combinational logic design 39

Combinational logic design 40

Combinational logic design 41

Bộ giải mã 7 thanh

• Bộ giải mã 7 thanh: – input mã BCD – output ñiều khiển hiển thị 7 thanh

Combinational logic design 42

74x49

Combinational logic design 43

Combinational logic design 44

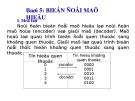

Bộ mã hóa (encoder)

• Mã hóa: biến ñổi mã ở input sang một mã khác

ở output: – n input (cid:1) 2n mã tổ hợp, m output (cid:1) 2m mã tổ hợp – Thường n > m – Bộ giải mã sử dụng nhiều:

• Mỗi bit input sẽ ứng với một tổ hợp của m bit output

Combinational logic design 45

Combinational logic design 46

Mã hóa ưu tiên 74x149

Combinational logic design 47

Combinational logic design 48

Combinational logic design 49

Combinational logic design 50

Dồn kênh (Multiplexer)

• Multiplexer:

– khóa số nối n input tới ñầu ra của nó phụ thuộc vào

tín hiệu ñiều khiển s – thường n = 2, 4, 8,... – s = log2(n)

• Không như dồn kênh tương tự, dồn kênh số chỉ cho tín hiệu ñi theo một chiều: input (cid:1)output

Combinational logic design 51

Combinational logic design 52

74x151

Combinational logic design 53

Combinational logic design 54

74x157

Combinational logic design 55

Combinational logic design 56

mở rộng nhiều multiplexer

Combinational logic design 57

Demultiplexer

• Bộ tách kênh: ngược lại với Multiplexer

– 1 input với n output – s tín hiệu chọn kênh output

Combinational logic design 58

Multiplexer – Demultiplexer

Combinational logic design 59

EXCLUSIVE OR

• Exclusive OR (XOR) và XNOR

Combinational logic design 60

thực hiện XOR

Combinational logic design 61

Combinational logic design 62

Kiểm tra chẵn – lẻ

• Một số ứng dụng (truyền tin) cần xem xét:

– số bit 1 trong dãy số là chẵn (even) ? – số bit 1 trong dãy số là lẻ (odd) ?

Combinational logic design 63

Combinational logic design 64

Bộ so sánh

• Sử dụng trong các hệ thống máy tính • Sử dụng trong các giao diện thiết bị ñể kiểm tra

ID

• So sánh 2 số nhị phân:

– So sánh bằng hoặc không bằng (cid:1) comparator – So sánh bằng, lớn hơn, nhỏ hơn (cid:1) magnitude

comparator

Combinational logic design 65

74x86

Bộ so sánh bằng và không bằng (comparator) sử dụng 74x86 kết hợp với NOR (74x02) và NAND (74x00)

Combinational logic design 66

74x85

So sánh =, > , < (magnitude comparator)

Combinational logic design 67

Combinational logic design 68

nối tầng 74x85

Combinational logic design 69

Bộ cộng

• Bộ cộng một nửa (halft adder): cộng hai toán

hạng X và Y 1 bit, kết quả cất trong 2 bit: – bit thấp của kết quả ký hiệu HS (halft sum) – bit cao của kết quả ky hiệu CO (carry out)

Combinational logic design 70

• Bộ cộng ñầy ñủ (full adder): dùng ñể cộng hai bit ở vị trí bất kỳ trong dãy số của số hạng nhiều bit X và Y: – Cần có bit carry-in (ñể nhận carry-out từ bit thấp) – Tổng cất trong 2 bit: • bit thấp ký hiệu S • bit cao ký hiệu là COUT

Combinational logic design 71

bộ cộng ñầy ñủ

Combinational logic design 72

Ripple adder

• Cộng hai số nhị phân n bit:

– Sử dụng full adder ñể cộng từng bit – n full adder ñược nối tầng ñể cộng n bit

Combinational logic design 73

ALU

• ALU (Arithemetic and Logic Unit): Là mạch tổ

hợp: – thực hiện các phép tính số học và logic trên 1 hoặc 2

biến n bit:

– Lựa chọn chế ñộ hoạt ñộng thông qua các tín hiệu

ñiều khiển

Combinational logic design 74

74x181

Combinational logic design 75

Combinational logic design 76

• minus: trừ (số học) • plus: cộng (số học)

Combinational logic design 77

Bộ nhân

• Tham khảo

Combinational logic design 78

Combinational logic design 79