Nội dung

▪Giới thiệu chung về hệ tổ hợp

▪Mạch mã hóa (Encoder)

▪Mạch giải mã (Decoder)

▪Mạch ghép kênh (MUX)

▪Mạch phân kênh (DEMUX)

▪Mạch số học

–Mạch cộng (Adder)

–Các mạch số học khác

▪Mạch so sánh (Comparator)

▪Mạch tạo và kiểm tra chẵn/lẻ (Parity Generator/Checker)

2

Khái niệm chung

▪Hệ tổ hợp (Combinational Circuits) là hệ có các ngõ

ra chỉ là các hàm logic theo ngõ vào:

–ngõ vào thay đổi trạng thái lập tức làm cho ngõ ra thay đổi

trạng thái ngay (giả sử bỏ qua thời gian trễ của các phần tử

logic) mà không chịu ảnh hưởng của trạng thái ngõ ra

trước đó.

▪Các cổng logic AND, OR, NOR, NAND, XOR,

XNOR là các phần tử logic cơ bản, và còn được gọi là

hệ tổ hợp đơn giản.

▪Các cổng NOR và NAND là các hệ tổ hợp đầy đủ.

3

Đặc điểm hệ tổ hợp

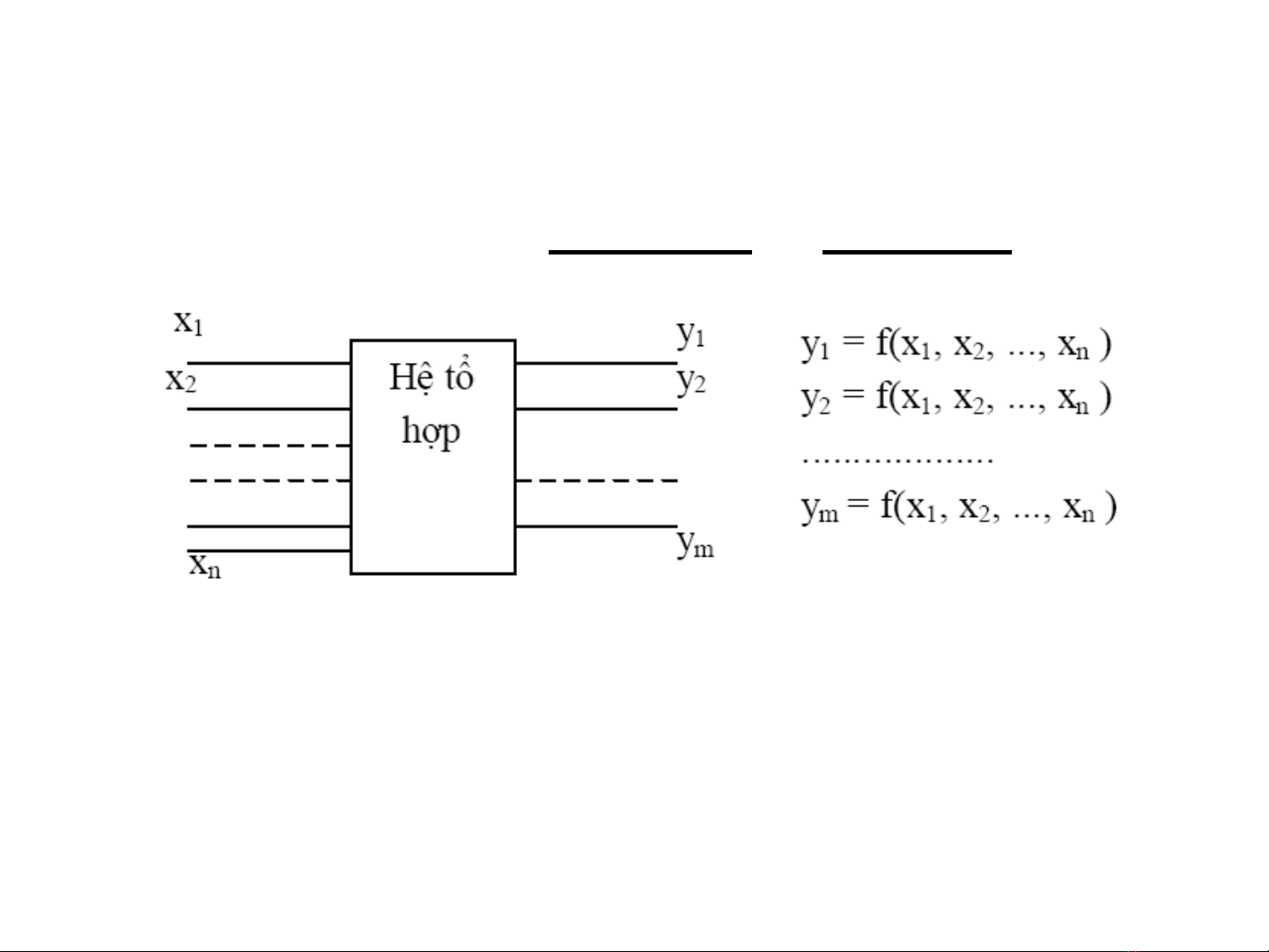

▪Xét một hệ tổ hợp có n ngõ vào và m ngõ ra

▪Đặc điểm cơ bản của hệ tổ hợp là tín hiệu ra tại mỗi

thời điểm chỉ phụ thuộc vào giá trị các tín hiệu vào ở

thời điểm đó mà không phụ thuộc vào giá trị các tín

hiệu ngõ ra ởcác thời điểm trước đó.

4

Trình tự thiết kế Hệ tổ hợp

1. Từ yêu cầu thực tế của hệ tổ hợp ta lập bảng giá trị

(Truth Table) mô tả hoạt động của mạch (hệ tổ hợp).

2. Dùng các phương pháp tối thiểu (đại số Boole hoặc/và Bìa

Karnaugh) để tối thiểu hoá các hàm logic

3. Thành lập sơ đồ logic (dựa vào pt logic đã tối giản)

4. Thực hiện sơ đồ logic bằng HDL (Verilog/VHDL)

5. Mô phỏng mạch (nếu cần)

6. Thi công mạch thực tế và kiểm tra mạch thực tế

5

![Giáo trình Kỹ thuật lắp đặt điện (Trình độ sơ cấp 2) - Trường Cao đẳng Cơ điện Tây Bắc: [Hướng dẫn chi tiết/Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260402/hoacattuong2026/135x160/37031775190349.jpg)

![Ngân hàng câu hỏi thi trắc nghiệm môn Máy điện [năm]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260401/190848/135x160/51431775038236.jpg)