Chương 5 :

TÔCHC VAO RA DLIÊU

•Sơđôchân tin hiêu

•Môt sômach phutr

•Nôi ghep vi bônh

•Nôi ghep vi thiêt bivao ra

4.1.Sơđôchân tin hiêu

AD7 -AD0 [I/O] :chân dồn kênh

cho tín hiệu phần thấp của bus địa

chỉ và dữ liệu (ALE=1 chân có tín

hiê u đia chi)

A15-A8 [O]: Là các bit pha n cao

của bus địa chỉ

A16/S3 – A19/S6 [O] :cha n don

kê nh cu a đia chi pha n cao cu a tin

hiê u tra ng tha i. (ALE=1 cha n la tín

hiê u đia chi)

RD[O]:Tin

hiê u cho

phê p đo c khi

RD=0 cho

phê p nha n dl

READY[I]:Tin

hiê u ba o cho

CPU biê t tinh

tra ng sa n sa ng

cu a ca c TBNV

hoa c cu a bo nhơ

INTR[I]:Tin

hiê u yê u

ca u nga t

chê đươ c.

TEST[I]:CPU sê chơ

đê n khi TEST=0

mơ i thư c hiê n lê nh

tiê p thêo

NMI[I]:Tin hiê u yê u ca u

nga t kho ng chê đươ c

RESET[I]:Tin

hiê u rêsêt la i

8088

CLK[I]:Tin

hiê u xung

đo ng ho

Vcc[I]:Cha n

nguo n

GND[O]:2

cha n nguo n

no i vơ i 0v

MN/MX[I]: cha n điê u

khiê n hoa t đo ng cu a

CPU thêo chê đo

min/max

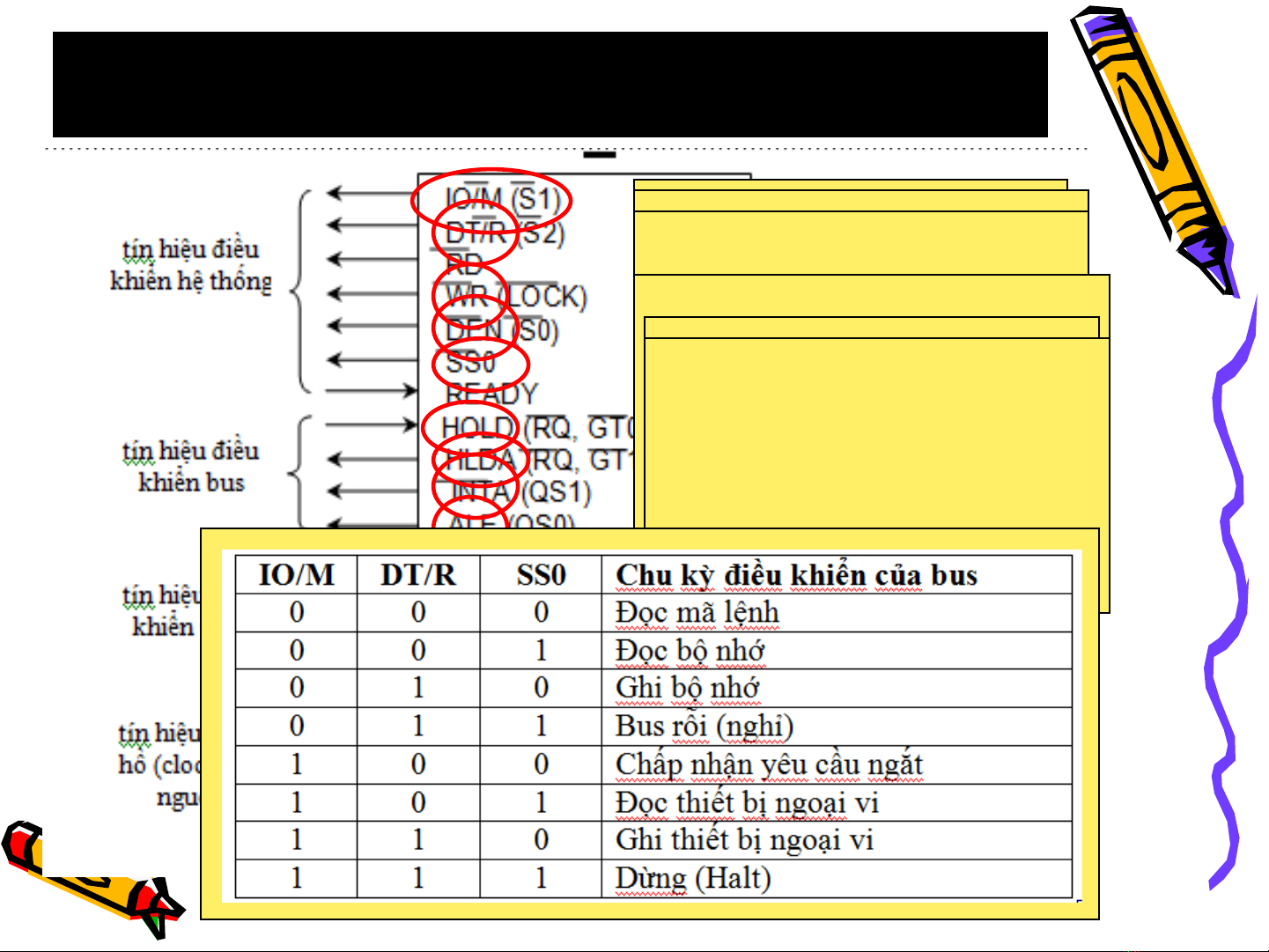

S4 S3 Chu k hot đng

0 0 truy cp dl đon m rng

0 1 truy cp dl đon ngăn xp

1 0 truy cp đon m hoc không

1 1 truy cp đon dl

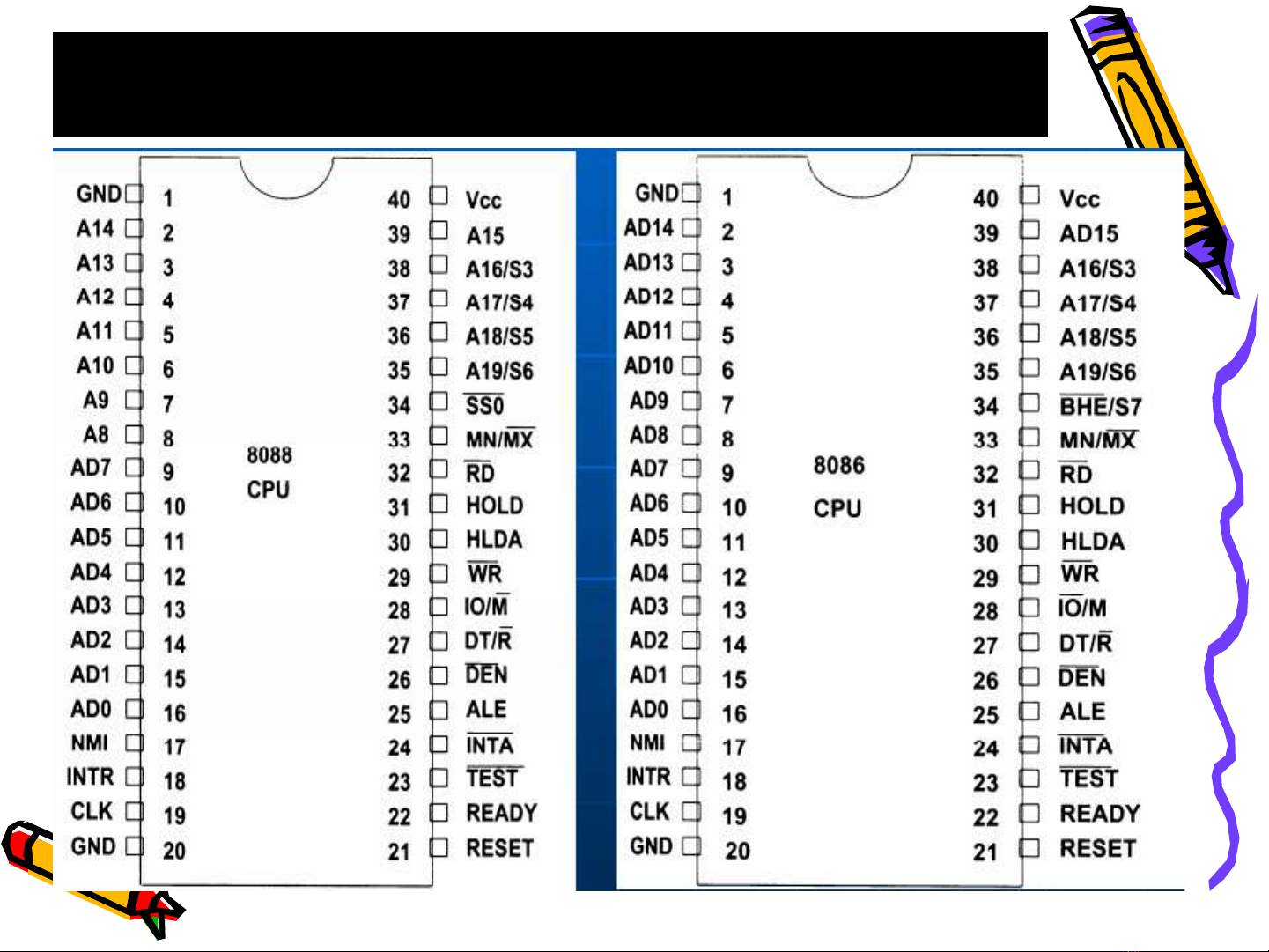

Sơđôchân 8088/8086

ChêđôMin/Max

• Anh hươ ng tơ i cac chân 24-31

•ChêđôMin:

– Cac chân 24-31 lacac tin hiêu đk I/O va

bônhơ

– Cac tin hiêu đk đêu tư 8088/8086

•ChêđôMax:

– Môt sôtin hiêu đk đươ c tao ra tư ngoai

– Môt sôchân cothêm chư c năng mơ i

– Sư dung bôđông xư lytoan 8087

ChêđôMin

IO/M[O]:phân bit trng

thi CPU truy cp b

nh hay vo ra.Tc

đng mc thp trong

chu k xut b nh

WR[O]: tc đng mc

thp cho php ghi vo

b nh hoc thit b

vo ra

ITNA[O]:INTA=0 bo

cho mch bên ngoi

bit CPU đ chp nhn

yêu cu ngt

ALE[O]:ng ra tc đng

mc cao đ ci tn hiu

đa ch trên bus đa h

DT/R[O]: xc đnh chiu

truyn d liu trên bus

DEN[O]:thông bo trng

thi ca CPU truyn nhn

d liu đa hp

HOLD[I]:yêu cu treo

CPU đ mch ngoi thc

hin trao đi vi b nh

bng cch truy nhp trc

tip (DMA)

HLDA[O]:thông bo yêu

cu treo CPU đ đưc

chp nhn

![Bài giảng Vi xử lí: Chương 3 - Hồ Trung Mỹ [Full]](https://cdn.tailieu.vn/images/document/thumbnail/2022/20220423/lavender2022/135x160/2530593_8215.jpg)

![Bài giảng Kỹ thuật vi xử lý Đại học Hàng Hải [Tài liệu chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2017/20171018/kloi1122/135x160/6951508314474.jpg)

![Giáo trình Trang bị điện nước (TC) - Trường Cao đẳng Công nghiệp Thanh Hóa [Ngành Điện nước]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260511/hoatrami2026/135x160/14221778681890.jpg)