1

MÔN HỌC

Ứng dụng Vi điều khiển

(Microcontroller Applications)

By Trần Văn Hùng

Mechatronics Dept

http://www.ntu.edu.vn/

Email: tvh42th@gmail.com

Tài liệu tham khảo

1.Microprofessors and microcpmputers hardware and softwware, Ronaid J.Tocci, Frank J.Ambrosio,

Prentice Hall, 2003

2.Interfacing Sensors To The Pc, Willis J.Tompkin, Jonh G.webster,Prentice Hall, 1998

3.Vi xử lý, Văn ThếMinh, NXB Giáo Dục.

4.Họ vi điều khiển 8051, Tống Văn On.

5.Kỹthuật Vi điều khiển AVR, Tống Văn On.

2

Nội dung chương trình

nCh01: Các hệ đếm vàmã hoá

nCh02: Hệthống vi xửlý

nCh03: Bộnhớ

nCh04: Họ vi điều khiển AVR

nCh05: Ngôn ngữlập trình CodevisionAVR

nCh06: Input/Output

Các bài toán

1. Thiếtkếmạch điềukhiểnánhsángtheochươngtrình địnhtrước

2. Thiếtkếmạchtrangtríbằng đènLED

3. Thiếtkếmạchnhậndạng điểmphụcvụ(thêm ít nhất 2IC)

4. Thiếtkếmạch đolượngmưa

5. Thiếtkếmạch điềukhiểnnhiệtđộ không khí

6. Thiết kếmạch điều khiển nhiệt độ dung dịch

7. Thiết kếmạch đồng hồ điện tử

8. Thiết kếmạch tính thời gian cho các môn điền kinh

9. Thiết kếbảng quang báo

10. Thiết kếmạch khoá điện tử

11. Thiết kếmạch điều khiển thiết bịbằng remote

12. Kết nối bàn phím máy tính với VXL, hiển thịký tựlên LCD

13. Thiết kếmạch điều khiển Robot chạy theo qũy đạo (sd motor bước)

14. Thiết kếmạch điều khiển tốc độ động cơ DC

15. Thiết kếmạch điều khiển góc quay của môtơ, ổn tốc cho motor.

1

Chương 1: Các hệ đếm vàmã hoá

nCác hệ đếm dùng trong máy tính

nCác phép toán sốhọc đối với hệhai

nMã ASCII

1.1 Các hệ đếm dùng trong máy tính

1.1.1 Hệ mười vàhệhai

nCon người thìquen dùng hệ cơ số mười (hệ mười)

1234,56 = 1.103+ 2.102+ 3.101+ 4.100+ 5.10-1 + 6.10-2

nMáy tính thìchỉlàm việc với hệ cơ sốhai (hệhai)

1011,01 = 1.23+ 0.22+ 1.21+ 1.20+ 0.2-1 + 1.2-2

nNibble gồm 4 bit

nByte gồm 8 bit

nWord gồm 16 bit

03

7 0

15 0

MSB LSB

2

1.1.1 Chuyển đổi giữa hệ mười vàhệhai

nĐổi hệhai sang hệ mười

1011,012= 1.23+ 0.22+ 1.21+ 1.20+ 0.2-1 + 1.2-2 = 11,2510

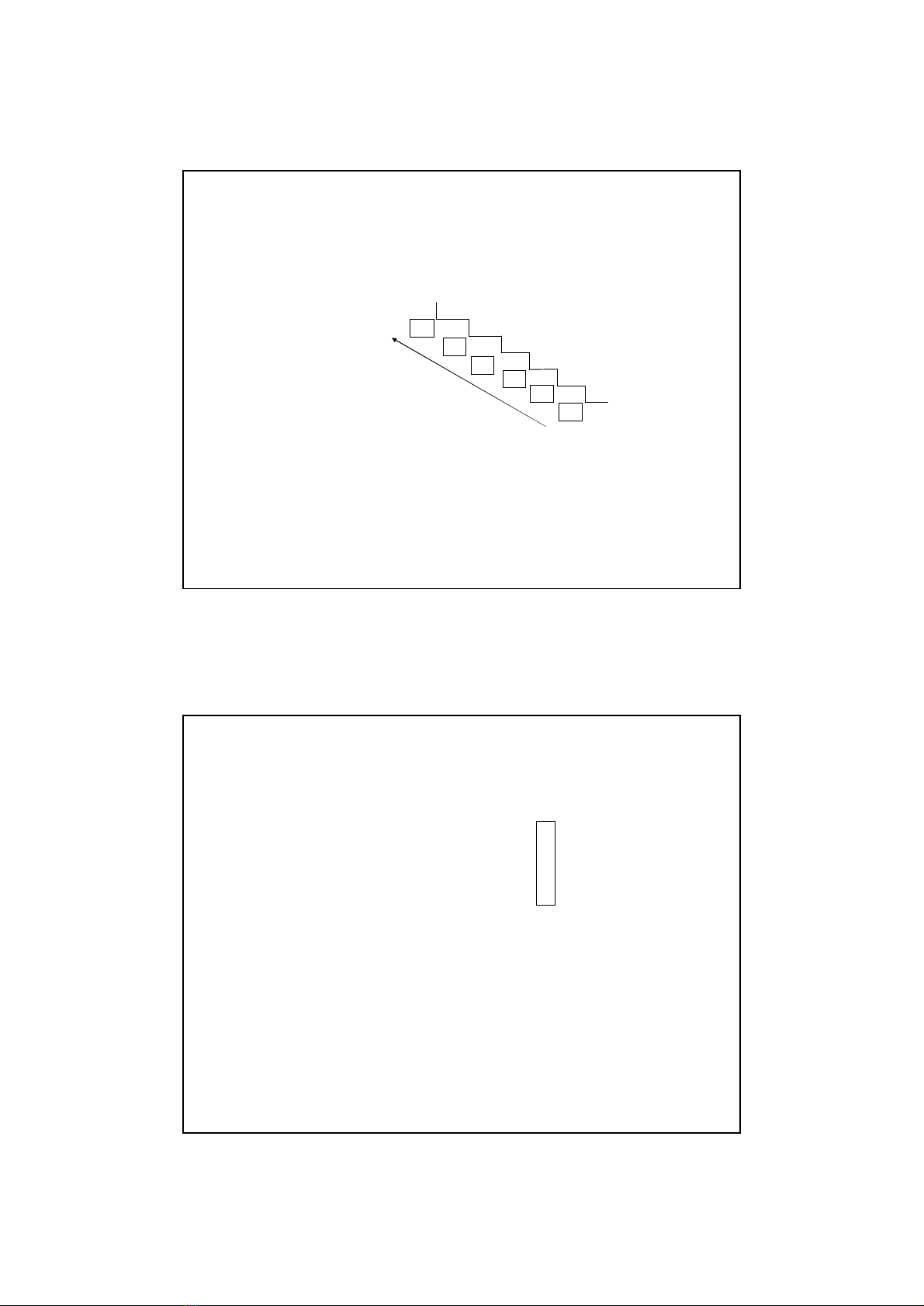

nĐổi hệ mười sang hệhai

4610 = 1011102

Hình 1. Một cách đổi hệ mười sang hệhai

0

1

46 2

23 2

11 2

5 2

2 2

1 2

0

11

0

1

1.1.1 Chuyển đổi giữa hệ mười vàhệhai (tiếp)

nĐổi sốthập phân hệ mười sang hệhai

0,12510 = 0,0012

nSốBCD (sốhệ mười mã hoábằng hệhai)

SốBCD thích hợp cho các thiếbị đo cóhiển thịsốở đầu ra.

123410 = 0001 0002 0003 0004BCD

nHệ mười sáu

123410 = 0100 1101 00102= 4D216

0,125 x 2 =

0,250 x 2 =

0,500 x 2 =

,250

,500

,000

0

0

1

3

1.2 Các phép toán sốhọc đối với hệhai

1.2.1 Phép cộng

ana(n-1) ... a2a1a0 + bmb(m-1) ... b2b1b0 = ckc(k-1) ... c2c1c0 (hệ cơ sốx)

ci = (ai + bi + (ai-1 + bi-1)%x )/x

Vídụcộng hệhai

1.2.2 Phép trừvàsốbùhai

a. Phép trừ

ana(n-1) ... a2a1a0 -b

m

b

(m-1) ... b2b1b0 = ckc(k-1) ... c2c1c0 (hệ cơ sốx)

ci = (ai –B

i-1) –b

i (nếu (ai –B

i-1) >= bivàB

i

= 0)

ci = (ai –B

i-1 + x) –b

i (nếu (ai –B

i-1) < bi vàB

i

= 1)

Vídụtrừhệhai

1101 1001

0001 1011

1111 0100

+

1101 1001

0001 1011

1011 1110

-

1.2.2 Phép trừvàsốbùhai (tiếp)

b. Sốbùhai

Ta cóthểthay phép trừbằng phép cộng: cộng sốbịtrừvới đối sốcủa sốtrừ.

Để tìm sốbùhai của một sốA ta làm theo các bước sau:

+ Biểu diễn sốA sốhệhai của nó.

+ Tìm sốbùmột (bùlogic) của số đó(đảo bít).

+ Cộng một vào sốbùmột ở trên để nhận được sốbùhai của A.

1.2.3 Phép nhân

Vídụnhân 2 sốhệhai có độ dài 4 bít

Bảng 1. Quy tắc phép nhân

a.bba

1

0

0

0

11

01

10

00

1011

0000

11

0

0

0

1

1

1

1

0

1

0

1

0

0

0

0

0

1

1

1

1

1

![Bài giảng Vi điều khiển Nguyễn Huy Hoàng: Tổng hợp kiến thức [Chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260316/hoatrami2026/135x160/72211773806757.jpg)

![Tài liệu thực tập cơ sở điều khiển tự động [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260507/hoahongxanh0906/135x160/26581778488080.jpg)