BT-VXL-Ch 1 – trang 1

ĐHBK Tp HCM–Khoa ĐĐT–BMĐT

GVPT: Hồ Trung Mỹ

Môn: Vi Xử Lý – AY1213

Bài tập – Chương 1. Giới thiệu hệ VXL tổng quát

Chú ý: Trong tất cả các bài tập chương này chúng ta giả sử là các chân chọn chip của bộ nhớ ROM, RAM, và

thiết bị I/O là tích cực thấp (/CS hay /CE) nếu không có qui định trước trong đề bài hay hình vẽ.

1. Viết các “từ điều khiển” (control word) (hình 1.14 trong sách VXL) để thực hiện các phép toán sau:

a) R3 2R1 – 3R2

b) R3 3R1 – 2R2

c) R5 4R1 – 2(R2 R4)

d) R1

Input/4 + (bù 1 của R3)/2

e) Output (bù 2 của R1) + (bù 2 của R2)

f) R5 16R1 + 8R2 – 4R3–2R4

2. Hãy cho biết dung lượng bộ nhớ lớn nhất (tính theo byte và word) mà CPU có thể quản lý được nếu nó có:

a) Số đường địa chỉ là 16 và số đường dữ liệu là 8.

b) Số đường địa chỉ là 20 và số đường dữ liệu là 8.

c) Số đường địa chỉ là 20 và số đường dữ liệu là 16.

d) Số đường địa chỉ là 24 và số đường dữ liệu là 32.

e) Số đường địa chỉ là 32 và số đường dữ liệu là 64.

3. Hãy cho biết giá trị của các cờ trong thanh ghi trạng thái sau khi CPU 8 bit thực thi lệnh sau (giả sử ban đầu

tất cả các cờ có trị là 0 trước khi thực thi lệnh)

a) Cộng 2 số 8 bit: +125 với –18

b) Cộng 2 số 8 bit: –125 với –18

c) Cộng 2 số 8 bit: F5H với 0BH

d) Trừ 2 số 8 bit: 104 với 12

e) Trừ 2 số 8 bit: –118 với –37

f) Trừ 2 số 8 bit: –128 với +57

4. Viết mã để tính biểu thức F = A * (B + C) + D trên các CPU có lệnh 3, 2, 1, và 0 địa chỉ. Không sắp xếp

lại biểu thức và khi tính toán không làm thay đổi các biến A, B, C, và D.

5. Viết mã để tính biểu thức F = (A + B) * C + D trên các CPU có lệnh 3, 2, 1, và 0 địa chỉ. Không sắp xếp

lại biểu thức và khi tính toán không làm thay đổi các biến A, B, C, và D.

6. Viết mã để tính biểu thức F = A * C + (B + C)* D trên các CPU có lệnh 3, 2, 1, và 0 địa chỉ. Không sắp

xếp lại biểu thức và khi tính toán không làm thay đổi các biến A, B, C, và D.

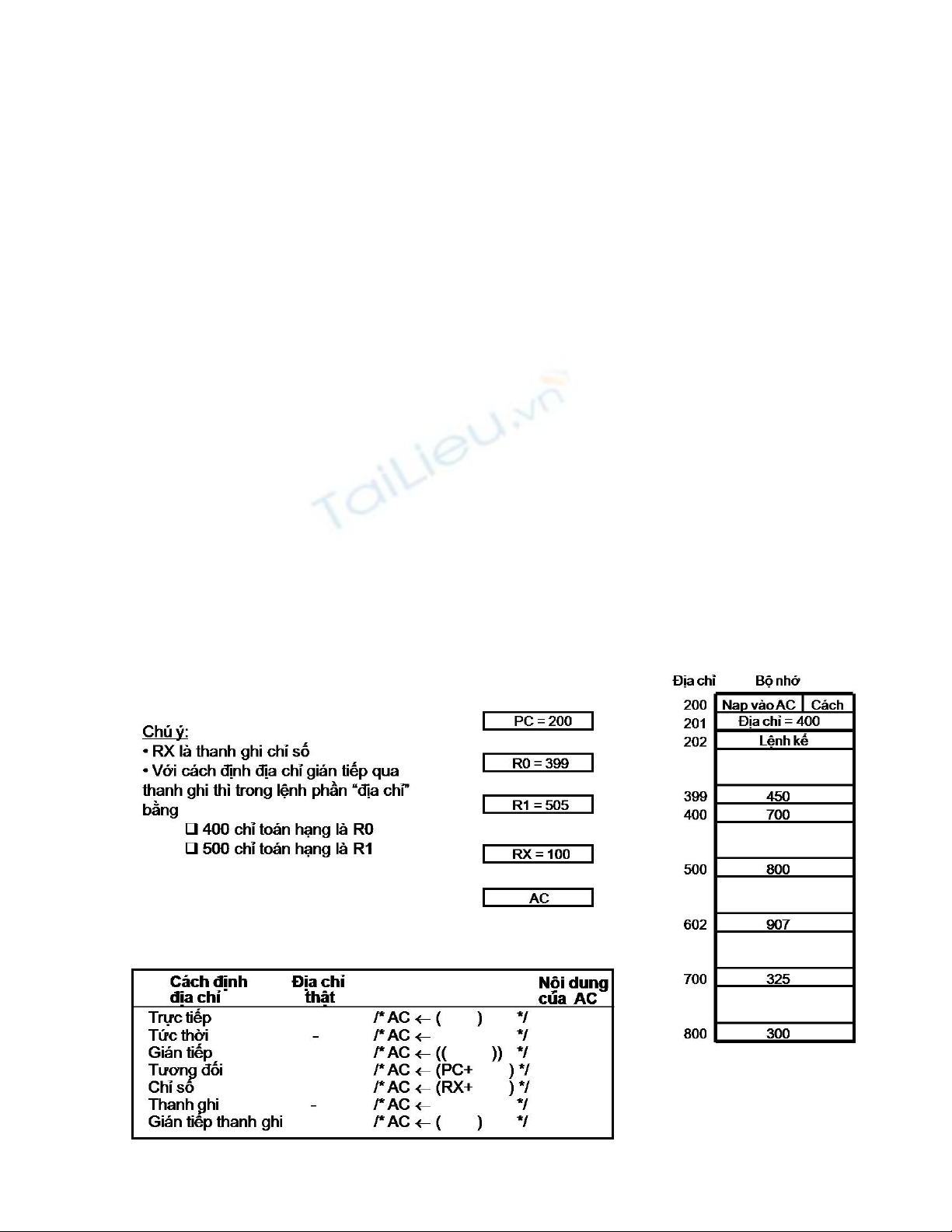

7. Hãy điền vào các chỗ trống trong hình sau cho thấy hiệu ứng của các cách định địa chỉ

Hình 1. Các cách định địa chỉ

BT-VXL-Ch 1 – trang 2

8. Xét một bộ nhớ có dung lượng 2M x 16, word đầu tiên của bộ nhớ này có byte thấp là EDH và byte cao là

05H. Hai byte này biểu diễn giá trị của 1 số nguyên có dấu 16 bit, hãy tìm giá trị thập phân của số nguyên này

nếu:

a) Bộ nhớ được lưu trữ theo “little endian”

b) Bộ nhớ được lưu trữ theo “big endian”

9. Xét một bộ nhớ có dung lượng 2M x 16, word đầu tiên của bộ nhớ này có byte thấp là D3H và byte cao là

25H, và word kế tiếp có byte thấp là 17H và byte cao là 36H. Bốn byte này biểu diễn giá trị của 1 số nguyên

có dấu 32 bit, hãy tìm giá trị thập phân của số nguyên này nếu:

a) Bộ nhớ được lưu trữ theo “little endian”

b) Bộ nhớ được lưu trữ theo “big endian”

10. Xét các bộ nhớ 32K x 8, 64K x 4, 128K x 16, và 256K x 1, với mỗi loại bộ nhớ hãy cho biết

a) Số chân địa chỉ và số chân dữ liệu của bộ nhớ này?

b) Dung lượng của bộ nhớ này tính theo bit, byte và word?

11. Giả sử một bộ nhớ 1M x 16 bit được xây dựng từ các chip SRAM 256K x 8 bit và word nhớ được tổ chức

định địa chỉ theo word 16 bit.

a) Số SRAM cần dùng là bao nhiêu?

b) Một word bộ nhớ cần truy cập bao nhiêu chip SRAM?

c) Số bank bộ nhớ là bao nhiêu? (bank bộ nhớ là 1 vùng nhớ được xây dựng từ các bộ nhớ có cùng kết

nối địa chỉ)

d) Số bit địa chỉ cần cho 1 chip RAM ?

e) Số bit địa chỉ cần cho bộ nhớ này?

12. Thiết kế ROM 3K x 8 từ các chip ROM 1K x 4.

13. Thiết kế ROM 2K x 8 từ các ROM 256 x 4.

14. Thiết kế module ROM 64K x 8 từ ROM 16K x 32

15. Thiết kế SRAM 8 x 32 từ các SRAM 8 x 8.

16. Thiết kế SRAM 16 x 4 từ các SRAM 4 x 4.

17. Thiết kế SRAM 16K x 8 từ: a) Các SRAM 1K x 1; b) Các SRAM 2K x 4; c) Các SRAM 1K x 8

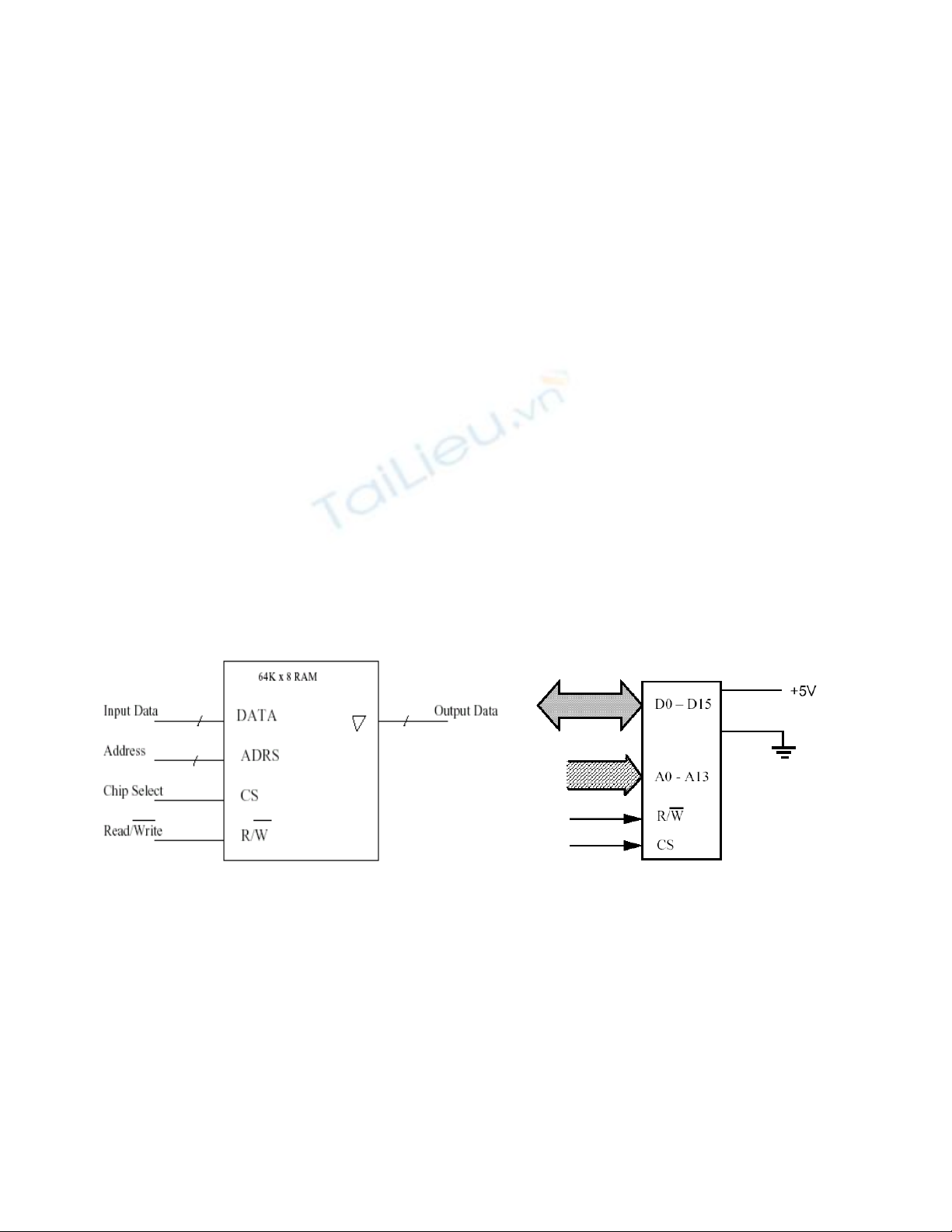

18. Sử dụng các RAM 64K x 8 (hình 2) và 1 mạch giải mã, xây dựng sơ đồ khối cho RAM 256K x 32.

Hình 2. RAM 64K x 8 Hình 3. RAM

19. Cho một chip bộ nhớ chuẩn như hình 3.

a) Tính số ô nhớ của chip này (theo K với 1 K=1024)

b) Viết phương trình tính số đường địa chỉ khi biết số ô nhớ?

c) Hãy thiết kế bộ nhớ 40K từ các chip bộ nhớ trên (có thể sử dụng thêm các cổng logic).

20. Hãy dùng các mạch logic thích hợp để thiết kế mạch nhận dữ liệu ở đơn vị đích với truyền dữ liệu song

song bất đồng bộ dùng xung strobe (xung lấy mẫu) xuất phát từ đơn vị nguồn.

21. Hãy dùng các mạch logic thích hợp để thiết kế mạch phát dữ liệu ở đơn vị nguồn với truyền dữ liệu song

song bất đồng bộ dùng xung strobe (xung lấy mẫu) xuất phát từ đơn vị đích.

22. Vẽ dạng sóng của khung truyền trong truyền dữ liệu nối tiếp bất đồng bộ khi truyền 1 byte 57H với LSB

được truyền đi trước cho các trường hợp sau: (nếu biết tốc độ truyền là 4800 bps)

a) Dữ liệu 7 bit, không có parity và 1 bit stop.

b) Dữ liệu 7 bit, có parity lẻ và 2 bit stop.

c) Dữ liệu 8 bit, không có parity và 1 bit stop.

d) Dữ liệu 8 bit, có parity lẻ và 1 bit stop.

BT-VXL-Ch 1 – trang 3

e) Dữ liệu 8 bit, có parity chẵn và 1 bit stop.

Chú ý: Phải ghi rõ chu kỳ bit, tên của các bit Start, Stop, Parity, và dữ liệu (D0=LSB . . .)

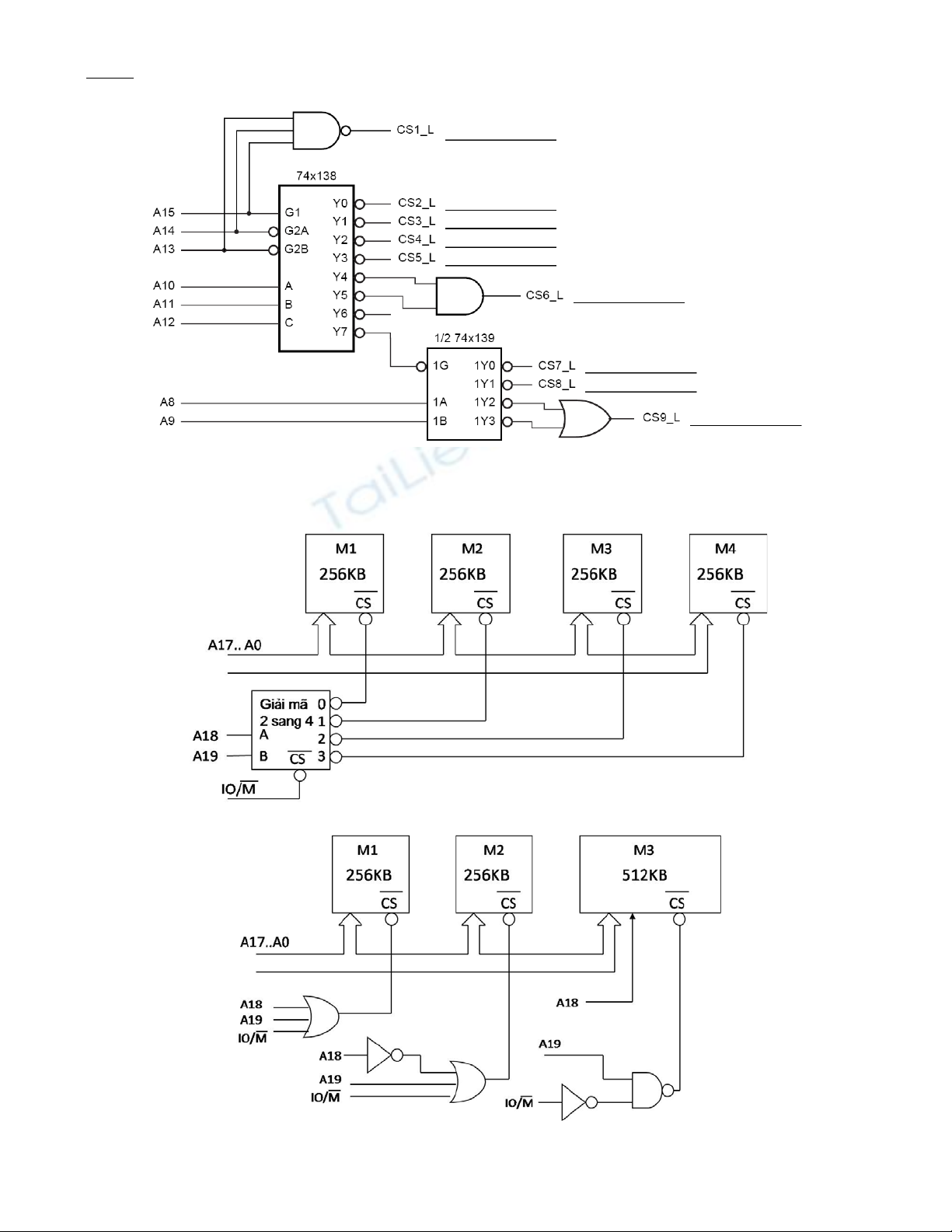

23. Hãy lập bảng bộ nhớ cho các tín hiệu CS trong hình sau:

Hình 4.

24. Hãy lập bảng bộ nhớ của các mạch ở hình 5 và 6, từ đó suy ra dung lượng của các hệ thống bộ nhớ này.

Các mạnh này dùng kiểu giải mã địa chỉ gì? (toàn phần hay 1 phần). Biết hệ thống này dùng CPU có 20

đường địa chỉ và có tín hiệu IO/M để điều khiển truy cập bộ nhớ hay I/O (0: bộ nhớ, 1: I/O)

Hình 5. Giải mã địa chỉ chỉ bằng decoder.

Hình 6. Giải mã địa chỉ chỉ bằng các cổng logic.

BT-VXL-Ch 1 – trang 4

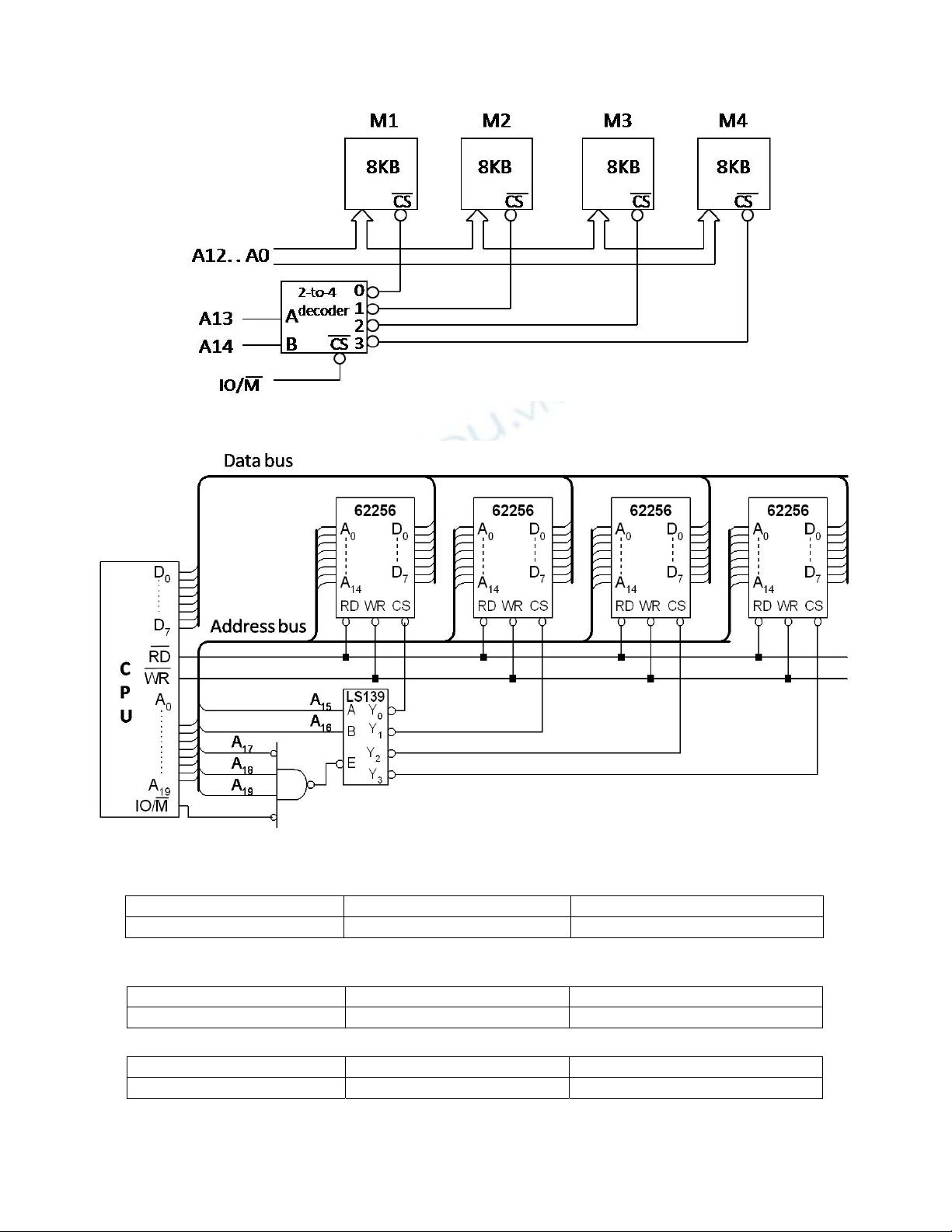

25. Hãy lập bảng bộ nhớ của hình sau, từ đó suy ra dung lượng của các hệ thống bộ nhớ này. Mạnh này dùng

kiểu giải mã địa chỉ gì? (toàn phần hay 1 phần).Biết hệ thống này dùng CPU có 16 đường địa chỉ và có tín

hiệu IO/M để điều khiển truy cập bộ nhớ hay I/O (0: bộ nhớ, 1: I/O)

Hình 7. Giải mã địa chỉ chỉ bằng decoder.

26. Hãy tìm dung lượng của mỗi SRAM và lập bảng bộ nhớ của mạch sau: (74139 là mạch giải mã 2 sang 4)

Hình 8. Giải mã địa chỉ chỉ bằng decoder và các cổng logic.

27. Thiết kế 1 module bộ nhớ chỉ bằng các ROM 4K, SRAM 1K và các mạch giải mã 74138 với dải địa chỉ

của các các bộ nhớ như sau:

ROM 1: 0000H–0FFFH ROM 3: 2000H–2FFFH SRAM 2: 6400H–67FFH

ROM 2: 1000H–1FFFH SRAM 1: 6000H–63FFH

28. Thiết kế 1 module bộ nhớ chỉ bằng ROM 4K, SRAM 1K và các mạch giải mã 74138 với dải địa chỉ của

các các bộ nhớ như sau:

ROM 1: 0000H–0FFFH ROM 3: 4000H–4FFFH SRAM 2: A000H–A3FFH

ROM 2: 2000H–2FFFH SRAM 1: 8000H–83FFH

29. Thiết kế mạch giải mã địa chỉ dùng 74138 với bảng bộ nhớ sau

SRAM 1: 2000H–3FFFH ROM 2: 6000H–7FFFH ROM 3: C000H–DFFFH

ROM 1: 4000H–5FFFH SRAM 2: A000H–BFFFH

30. Xét 1 hệ VXL dùng CPU có 8 đường dữ liệu và 16 đường địa chỉ. Hệ này dùng 1 ROM 8K x 8 và 2

SRAM 8K x8 với bảng bộ nhớ sau:

ROM: 0000H–1FFFH SRAM 1: 2000H–3FFFH SRAM 2: 4000H–5FFFH

BT-VXL-Ch 1 – trang 5

Hãy thiết kế mạch giải mã địa chi theo: a) giải mã toàn phần; b) giải mã một phần.

31. Thiết kế mạch giải mã địa chỉ cho CPU có 20 bit địa chỉ, 8 bit dữ liệu để có thể truy cập RAM 64KB với

vùng địa chỉ là 00000H – 0FFFFH. Biết RAM có số hiệu là HM62864 với các đường tín hiệu:

/CS1, CS2 là 2 đường chọn chip

/OE cho phép xuất

/WE cho phép ghi

16 đường địa chỉ A15...A0

8 đường dữ liệu I/O7...I/O0

và CPU có các đường điều khiển bộ nhớ là /MEMW và /MEMR.

32. Thiết kế mạch giải mã địa chỉ cho CPU có 20 bit địa chỉ, 8 bit dữ liệu với bảng bộ nhớ như sau:

00000 H – 3FFFFH : RAM 0 256 KB

40000 H – 7FFFFH : RAM 1 256 KB

80000 H – BFFFFH: RAM 2 256 KB

E0000 H – EFFFFH: ROM 0 64 KB

F0000 H – EFFFFH: ROM 1 64 KB

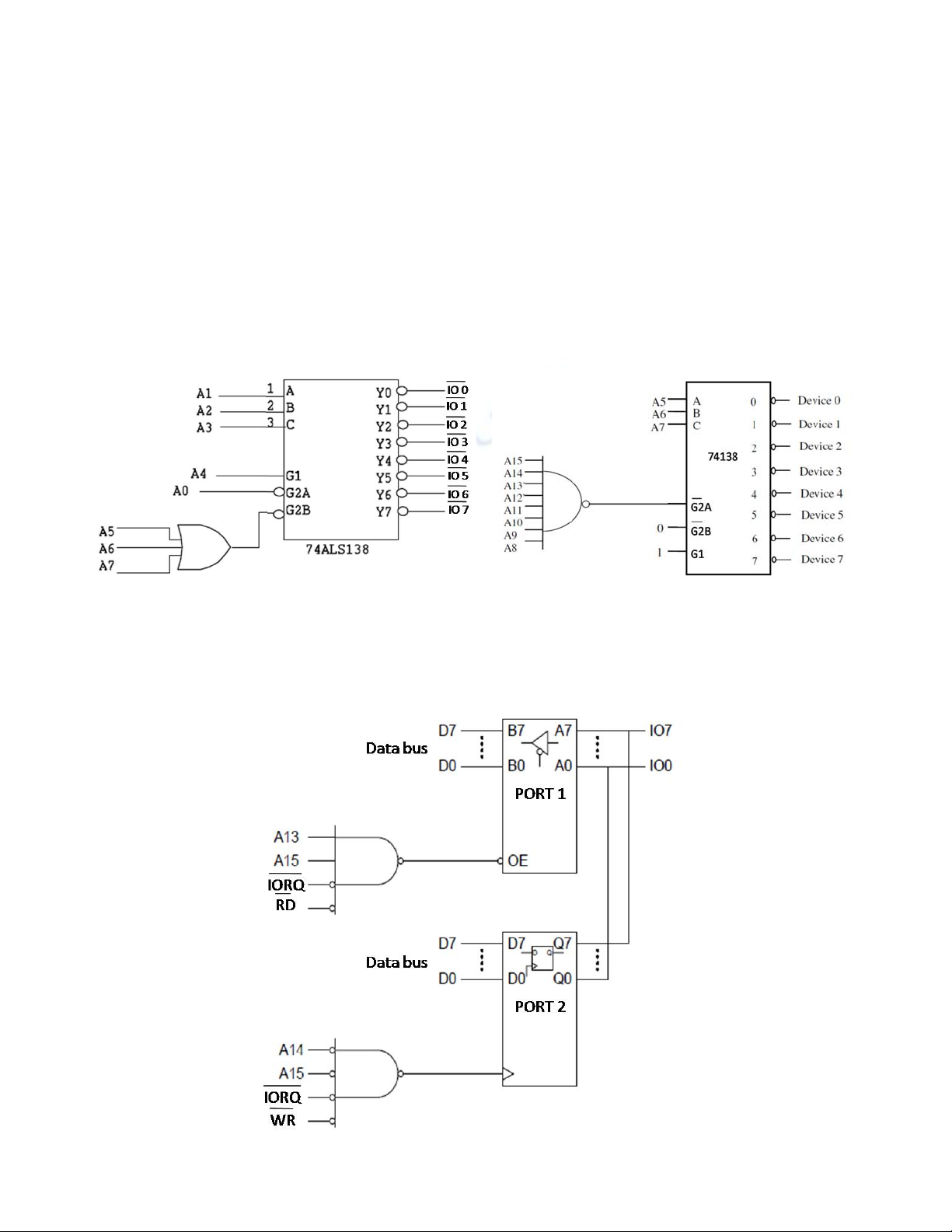

33. Hãy lập bảng I/O cho các mạch giải mã địa chỉ I/O sau:

Hình 9. Hình 10.

34. Với mạch giải mã địa chỉ thiết bị I/O sau ở hình 11. Biết khi truy cập I/O thì tín hiệu /IORQ = 0.

a) Hãy cho biết các PORT 1 và PORT 2 đóng vai trò gì? (cổng xuất hay nhập)

b) Tìm địa chỉ của các PORT 1 và PORT 2. Mô tả làm cách nào CPU có thể đọc vào hay xuất ra qua các

chân IO của mạch.

Hình 11. Giải mã địa chỉ của cổng I/O.

![Bài tập thực hành mạch điện tử [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2011/20110526/thuongduongk12/135x160/bai_tap_thuc_hang_mach_dien_tu_4058.jpg)

![Bài tập mạch điện tử [chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2010/20100914/thanhquangvaa/135x160/bai_tap_mach_dien_1_5954.jpg)

![Giáo trình Vô tuyến điện viên hàng hải GMDSS hạng tổng quát: Phần 1 [Chuẩn Nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260504/vispacex_27/135x160/45101777969769.jpg)

![Giáo trình Thực tập điện tử cơ bản: Phần 1 [Full]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260504/vispacex_27/135x160/66001778032993.jpg)