Đ I H C ĐÀ N NGẠ Ọ Ẵ

TR NG Đ I H C BÁCH KHOAƯỜ Ạ Ọ

KHOA ĐI N T -VI N THÔNGỆ Ử Ễ

Đ ÁN Ồ

VI X LÝ VÀ MÁY TÍNHỬ

LAB 3 : MIPS Single-cycle CPU

SINH VIÊN TH C HI N: PHAN QU C TH NG 08DT3Ự Ệ Ố Ắ

HOÀNG THANH TÚ 08DT3

NGUY N TH TÙNG 08DT4Ễ Ị

1. M C ĐÍCH:Ụ

Thi t k m t chip MIPS single-cycle đ n gi n đ th c thi các l nh ế ế ộ ơ ả ể ự ệ LW, SW, J , JR,

BNE, XORI, SLT, ADD, SUB trong m t chu kỳ l nh.ộ ệ

2. T NG QUAN:Ố

2.1. Các b c th c thi l nh:ướ ự ệ G m có 3 b c chínhồ ướ

- Dùng b đ m ch ng trình PC l y đ a ch l nh trong b nh l nh ( Instructionộ ế ươ ấ ị ỉ ệ ộ ớ ệ

Memory), và c p nh t PC đ n giá tr ti p theo.ậ ậ ế ị ế

- Gi i mã l nh b ng cách g i cái OPCODE vào kh i CONTROL.(Đ c giá tr cácả ệ ằ ử ố ọ ị

thanh ghi t REGISTER FILE)ừ

- Th c thi l nh.ự ệ

2.2. Gi i thi u các l nh:ớ ệ ệ

Page 1

Trong MIPS có 3 khuôn d ng l nh R-Format, I-Format và J-Formatạ ệ

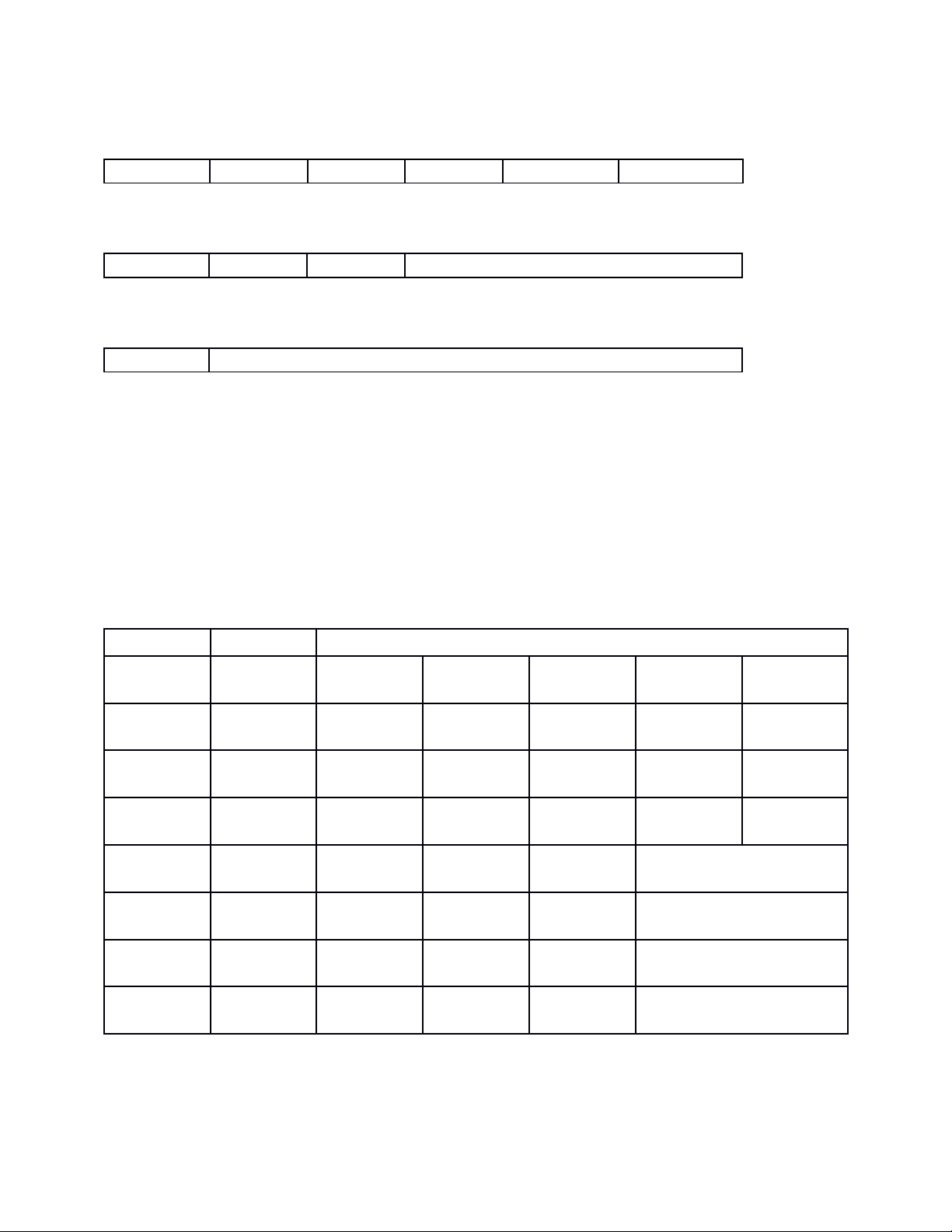

•R-Format:

op rs rt rd shamt funct

6 bits 5 bits 5 bits 5 bits 5 bits 6 bits

•I-Format:

op rs rt immediate

6 bits 5 bits 5 bits 16 bits

•J-Format:

op immediate

6 bits 26 bits

V i ớ op : 6 bits OPCODE

rs : 5 bits ch a mã đ a ch c a thanh ghi ngu nứ ị ỉ ủ ồ

rt : 5 bits ch a mã đ a ch c a thanh ghi ngu nứ ị ỉ ủ ồ

rd : 5 bits ch a mã đ a ch c a thanh ghi đíchứ ị ỉ ủ

shamt : 5 bits dùng trong các l nh d chệ ị

funct: 6 bits dùng đ phân lo i trong các l nh R-Formatể ạ ệ

immediate : 16 bits ch a toán h ng và đ a ch ofsetứ ạ ị ỉ

immediate : 26 bits ch a đ a ch đích trong l nh JUMPứ ị ỉ ệ

-Khuôn d ng c th c a m i l nh:ạ ụ ể ủ ỗ ệ

Instruction Meaning Format

add rd,

rs, rt

C ngộ0 rs rt rd 0x20

sub rd,

rs, rt

Trừ0 rs rt rd 0x22

slt rd,

rs, rt

So sánh 0 rs rt rd 0x2a

jr rs Nh y đ nả ế

[rs]

0 rs rt 0 0x08

xori rt,

im

Xor

immediate

0x0e rs rt im

lw rt,

im

Load word 0x23 rs rt im

sw rt,

im

Store word 0x2b rs rt im

bne rs,

rt, im

Nh y n uả ế

không

0x05 rs rt im

Page 2

b ngằ

j im Jump 0x02 im

2.3. Phân tích l nh:ệ

- Đ i v i các lênh x lý d li u khuôn d ng R-Format – ố ớ ử ữ ệ ạ ADD, SUB, SLT :

Fetch instruction: Instruction ← MEM[PC]

Fetch operands: data1 ← Reg(Rs), data2 ← Reg(Rt)

Execute operation: ALU_result ← funct(data1, data2)

Write ALU result: Reg(Rd) ← ALU_result

Next PC address: PC ← PC + 4

- Đ i v i các lênh x lý d li u (I_FORMAT – XORI) : ố ớ ử ữ ệ

Fetch instruction: Instruction ← MEM[PC]

Fetch operands: data1 ← Reg(Rs), data2 ← extend-sign (imm16)

Execute operation: ALU_result ← XOR(data1, data2)

Write ALU result: Reg(Rt) ← ALU_result

Next PC address: PC ← PC + 4

- Đ i v i lênh load d li u (I_FORMAT – LW) : ố ớ ữ ệ

Fetch instruction: Instruction ← MEM[PC]

Fetch base register: base ← Reg(Rs)

Calculate address: address ← base + extend-sign (imm16)

Read memory: data ← MEM[address]

Write register Rt:Reg(Rt) ← data

Next PC address: PC ← PC + 4

- Đ i v i lênh l u d li u (I_FORMAT – SW) : ố ớ ư ữ ệ

Fetch instruction: Instruction ← MEM[PC]

Fetch registers: base ← Reg(Rs), data ← Reg(Rt)

Calculate address: address ← base + extend-sign (imm16)

Write memory: MEM[address] ← data

Next PC address: PC ← PC + 4

- Đ i v i lênh r nhánh (I_FORMAT – BNE) : ố ớ ẻ

Fetch instruction: Instruction ← MEM[PC]

Fetch operands: data1 ← Reg(Rs), data2 ← Reg(Rt)

Execute operation: ALU_result ← SUB (data1, data2)

Branch: if (zero!=0) PC ← (PC + 4) + 4×extend-sign(imm16)

else PC ← PC + 4

Page 3

- Đ i v i lênh nh y (J_FORMAT – JUMP) : ố ớ ả

Fetch instruction: Instruction ← MEM[PC]

Target PC address: target ← PC[31:28] , Imm26 , ‘00’

Jump: PC ← target

- Đ i v i lênh nh y (R_FORMAT –JR) : ố ớ ả

Fetch instruction: Instruction ← MEM[PC]

Fetch operands: address ← Reg(Rs)

Jump: PC ← address

3. CÁC KH I C S C N THI T:Ố Ơ Ở Ầ Ế

- Sau khi phân tích cách ho t đ ng m i l nh, ta s xây d ng các kh i c b n đ th c thiạ ộ ỗ ệ ẽ ự ố ơ ả ể ự

các l nh đóệ

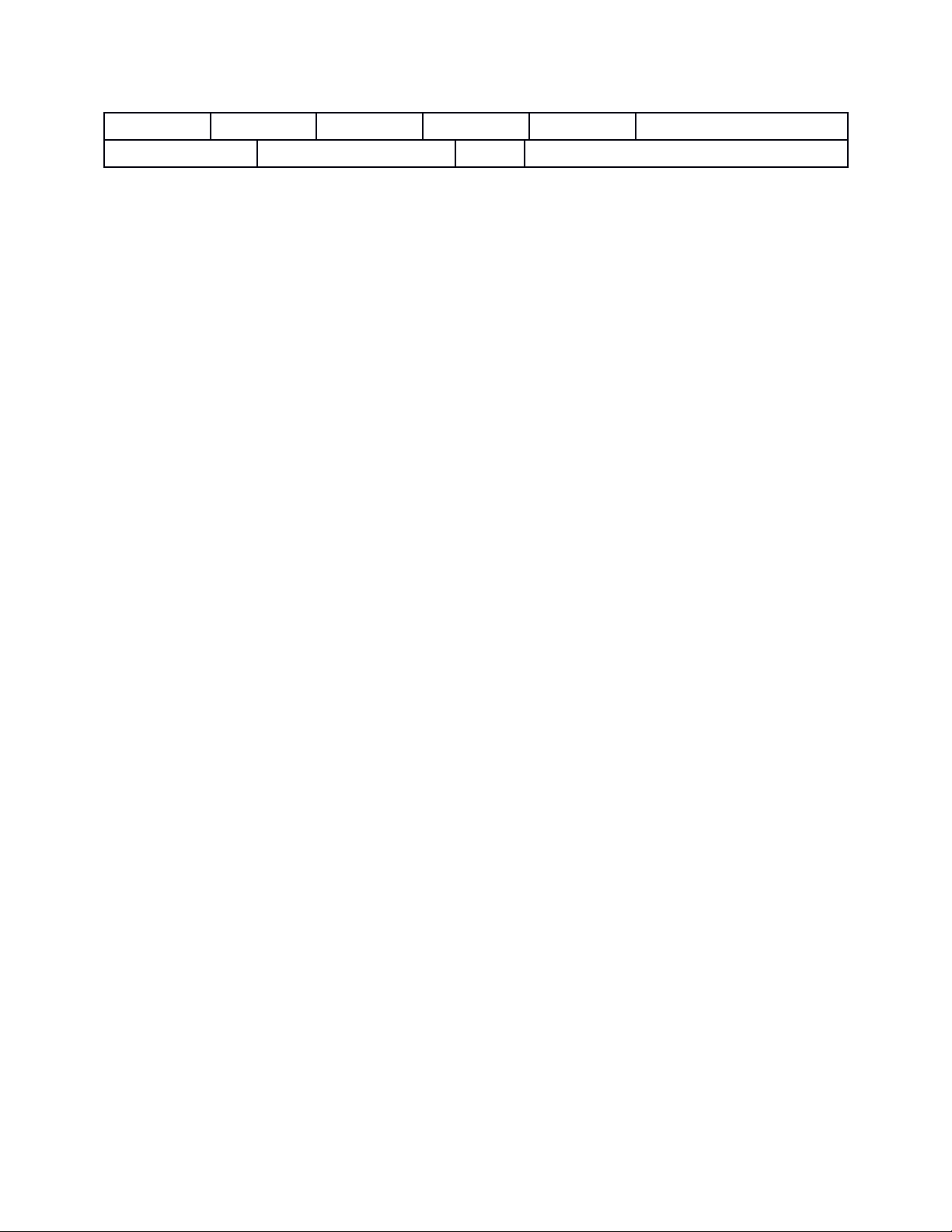

3.1 Kh i PC:ố

- Kh i b đ m ch ng trình, có tác d ng nh m t b đ m đ ch đ n đ a ch c aố ộ ế ươ ụ ư ộ ộ ệ ể ỉ ế ị ỉ ủ

câu l nh ti p theo.ệ ế

- Giá tr đ u vào đ c xác đ nh tùy theo câu l nh m i đ c th c hi n.ị ầ ượ ị ệ ớ ượ ự ệ

3.2 Kh i Instruction Memory:ố

- Là kh i l u các l nh c n th c thi, g m 1 đ u vào 32 bits address và đ u ra là 32ố ư ệ ầ ự ồ ầ ầ

bits instruction

- Đ a ch đ u vào đ c l y t PC và s tham chi u đ n file l u l nh d i tênị ỉ ầ ượ ấ ừ ẽ ế ế ư ệ ướ

instr.dat ( đây Instruction Memory đ c đánh đ a ch theo word nên ta ph i l y đ a chở ượ ị ỉ ả ấ ị ỉ

trong

PC / 4 và làm tròn.)

- File instr.dat là file ch a mã máy c a các câu l nh c n th c hi n. Đ u ra s là mãứ ủ ệ ầ ự ệ ầ ẽ

máy ng v i đ a ch c a instruction memory đ c tham chi u t i.ứ ớ ị ỉ ủ ượ ế ớ

Page 4

WE

DATAIN[31..0]

WADDR[9..0]

RADDR[9..0]

DATAOUT[31..0]

SYNC_RAM

BUF (SOFT)

0buf[31..0]

instruction[31..0]

instrmem

32' h00000000 --

10' h000 --

address[31..0]

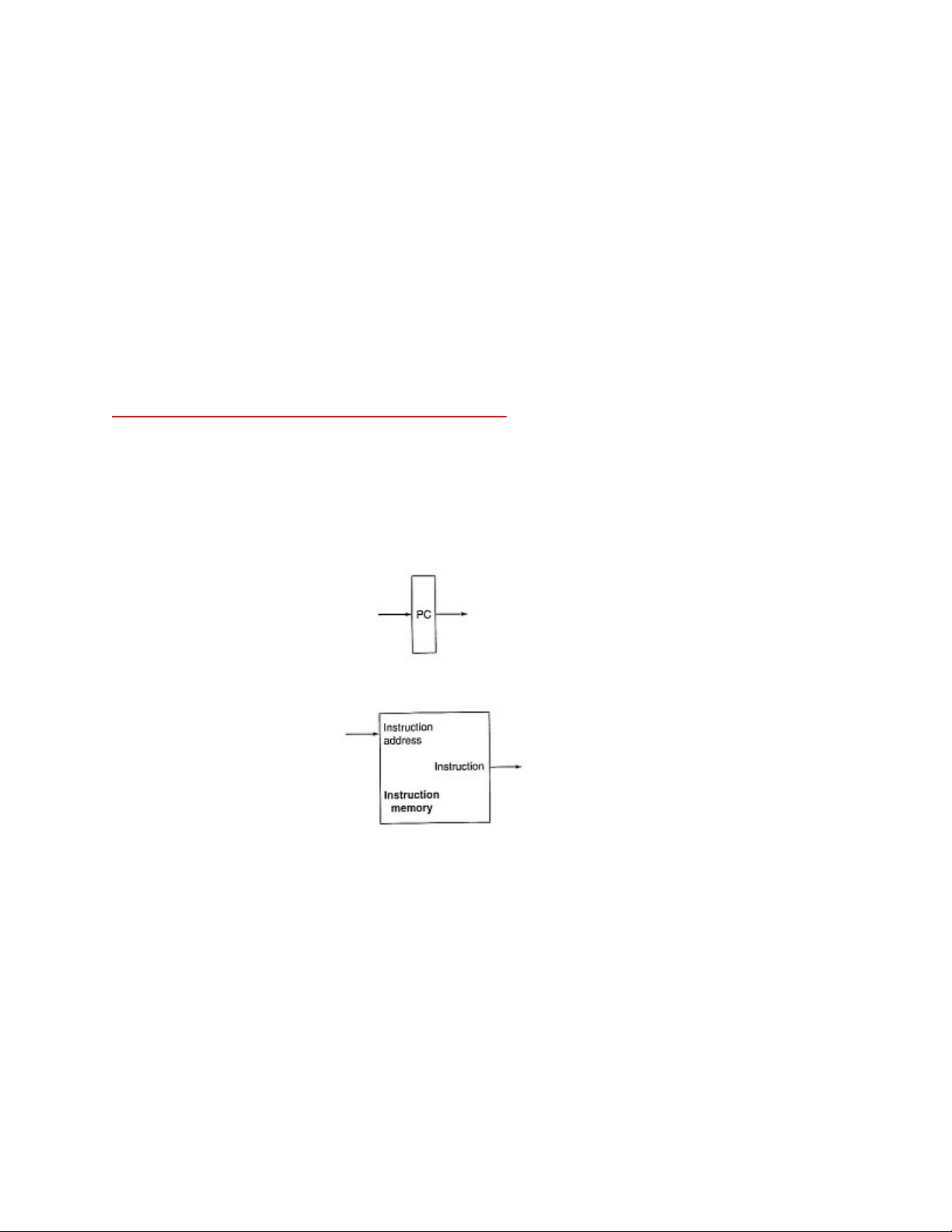

3.3 Kh i ADD: ốC ng 2 tín hi u vào 32bit, kh i này đ c xây d ng t 32 kh i add_bitộ ệ ố ượ ự ừ ố

đã đ c làm rõ trong bài 2.ượ

3 kh i dùng đ ố ể Store/Fetch Instruction, và tăng thanh ghi PC lên.T 3 kh i trên ta xâyừ ố

d ng đ c datapath nh sau:ự ượ ư

3.4 Kh i register file:ố

Page 5

![Bài thi cuối kì Xây dựng các hệ thống nhúng [năm]](https://cdn.tailieu.vn/images/document/thumbnail/2021/20210629/khiemthocu/135x160/9311624952206.jpg)

![Phát triển website cho thuê xe Việt Key: Đồ án tốt nghiệp [Chuẩn SEO]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260423/hoacattuong2026/135x160/69001777431707.jpg)

![Xây dựng website bán hàng và cung cấp dịch vụ hosting: Đồ án tốt nghiệp [Chuẩn SEO]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260423/hoacattuong2026/135x160/75141777431708.jpg)