Bài giảng Hệthống máy tính

Nguyễn Kim Khánh - ĐHBKHN 1

8 September 2009 1

NKK-HUT

Hệthống máy tính

Chương 2

KIẾN TRÚC BỘNHỚ

Nguyễn Kim Khánh

Trường Đại học Bách khoa Hà Nội

8 September 2009 2

NKK-HUT

Nội dung học phần

Chương 1. Giới thiệu chung

Chương 2. Kiến trúc bộnhớ

Chương 3. Kiến trúc vào-ra

Chương 4. Kiến trúc bộxử lý

Chương 5. Kiến trúc máy tính tiên tiến

8 September 2009 3

NKK-HUT

2.1. Tổng quan vềhệthống nhớ

2.2. Bộnhớbán dẫn

2.3. Bộnhớchính

2.4. Bộnhớcache

2.5. Bộnhớảo

2.6. Hệthống lưu trữRAID

Nội dung

8 September 2009 4

NKK-HUT

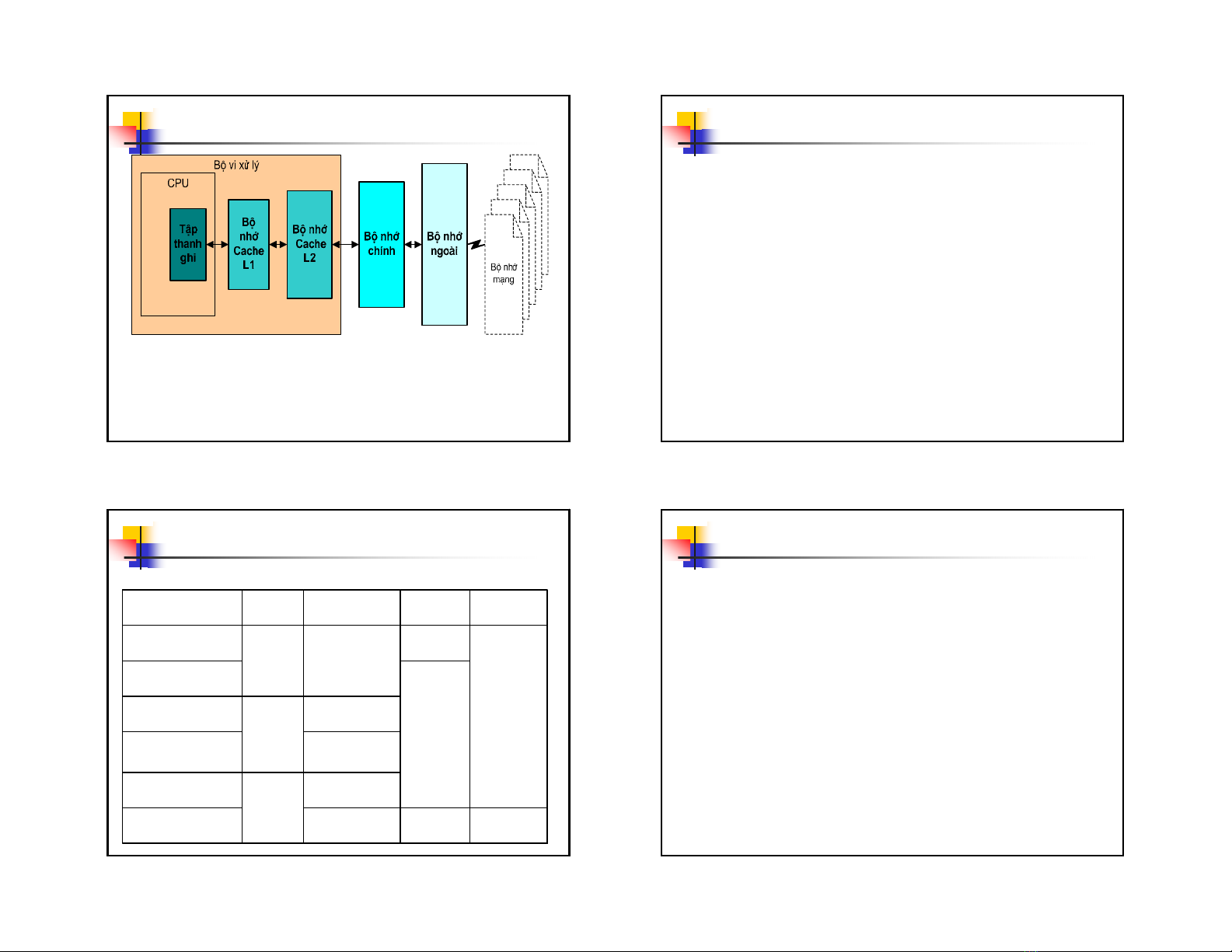

2.1. Tổng quan vềhệthống nhớ

Vịtrí

Bên trong CPU:

tập thanh ghi

Bộnhớtrong:

bộnhớchính

bộnhớcache

Bộnhớngoài: các thiết bịnhớ

Dung lượng

Độ dài từnhớ(tính bằng bit)

Số lượng từnhớ

1. Các đặc trưng của hệthống nhớ

Bài giảng Hệthống máy tính

Nguyễn Kim Khánh - ĐHBKHN 2

8 September 2009 5

NKK-HUT

Các đặc trưng của hệthống nhớ(tiếp)

Đơn vịtruyền

Từnhớ

Khối nhớ

Phương pháp truy nhập

Truy nhập tuần tự (băng từ)

Truy nhập trực tiếp (các loại đĩa)

Truy nhập ngẫu nhiên (bộnhớbán dẫn)

Truy nhập liên kết (cache)

8 September 2009 6

NKK-HUT

Các đặc trưng của hệthống nhớ(tiếp)

Hiệu năng (performance)

Thời gian truy nhập

Chu kỳnhớ

Tốc độ truyền

Kiểu vật lý

Bộnhớbán dẫn

Bộnhớtừ

Bộnhớquang

8 September 2009 7

NKK-HUT

Các đặc trưng của hệthống nhớ(tiếp)

Các đặc tính vật lý

Khảbiến / Không khảbiến

(volatile / nonvolatile)

Xoá được / không xoá được

Tổchức

8 September 2009 8

NKK-HUT

2. Phân cấp hệthống nhớ

Bài giảng Hệthống máy tính

Nguyễn Kim Khánh - ĐHBKHN 3

8 September 2009 9

NKK-HUT

Ví dụhệthống nhớthông dụng

Từtrái sang phải:

dung lượng tăng dần

tốc độ giảm dần

giá thành/1bit giảm dần

8 September 2009 10

NKK-HUT

Nguyên lý cục bộhoá tham chiếu bộnhớ

Trong một khoảng thời gian đủ nhỏ CPU

thường chỉtham chiếu các thông tin

trong một khối nhớcục bộ

Ví dụ:

Cấu trúc chương trình tuần tự

Vòng lặp có thân nhỏ

Cấu trúc dữliệu mảng

8 September 2009 11

NKK-HUT

2.2. Bộnhớbán dẫn

Khảbiến

Bằng điện

bằng điện,

mức từng byte

Bộnhớ

đọc-ghi

Random Access

Memory (RAM)

bằng điện,

từng khối

Flash memory

bằng điện,

mức từng byte

Electrically Erasable

PROM (EEPROM)

bằng tia cực tím,

cảchip

Bộnhớ

hầu như

chỉ đọc

Erasable PROM

(EPROM)

Bằng điện

Programmable ROM

(PROM)

Không

khảbiến

Mặt nạ

Không xoá

được

Bộnhớ

chỉ đọc

Read Only Memory

(ROM)

Tính

khảbiến

Cơ chếghiKhả năng xoáTiêu

chuẩn

Kiểu bộnhớ

1. Phân loại

8 September 2009 12

NKK-HUT

ROM (Read Only Memory)

Bộnhớkhông khảbiến

Lưu trữcác thông tin sau:

Thư viện các chương trình con

Các chương trình điều khiển hệthống (BIOS)

Các bảng chức năng

Vi chương trình

Bài giảng Hệthống máy tính

Nguyễn Kim Khánh - ĐHBKHN 4

8 September 2009 13

NKK-HUT

Các kiểu ROM

ROM mặt nạ:

thông tin được ghi khi sản xuất

rất đắt

PROM (Programmable ROM)

Cần thiết bịchuyên dụng để ghi bằng chương

trình Æchỉ ghi được một lần

EPROM (Erasable PROM)

Cần thiết bịchuyên dụng để ghi bằng chương

trình Æghi được nhiều lần

Trước khi ghi lại, xóa bằng tia cực tím

8 September 2009 14

NKK-HUT

Các kiểu ROM (tiếp)

EEPROM (Electrically Erasable PROM)

Có thểghi theo từng byte

Xóa bằng điện

Flash memory (Bộnhớcực nhanh)

Ghi theo khối

Xóa bằng điện

8 September 2009 15

NKK-HUT

RAM (Random Access Memory)

Bộnhớ đọc-ghi (Read/Write Memory)

Khảbiến

Lưu trữthông tin tạm thời

Có hai loại: SRAM và DRAM

(Static and Dynamic)

8 September 2009 16

NKK-HUT

SRAM (Static) – RAM tĩnh

Các bit được lưu trữbằng các Flip-Flop

Æthông tin ổn định

Cấu trúc phức tạp

Dung lượng chip nhỏ

Tốc độ nhanh

Đắt tiền

Dùng làm bộnhớcache

Bài giảng Hệthống máy tính

Nguyễn Kim Khánh - ĐHBKHN 5

8 September 2009 17

NKK-HUT

DRAM (Dynamic) – RAM động

Các bit được lưu trữtrên tụ điện

Æcần phải có mạch làm tươi

Cấu trúc đơn giản

Dung lượng lớn

Tốc độ chậm hơn

Rẻtiền hơn

Dùng làm bộnhớchính

8 September 2009 18

NKK-HUT

Một sốDRAM tiên tiến

Enhanced DRAM

Cache DRAM

Synchronous DRAM (SDRAM): làm việc

được đồng bộbởi xung clock

DDR-SDRAM (Double Data Rate SDRAM)

8 September 2009 19

NKK-HUT

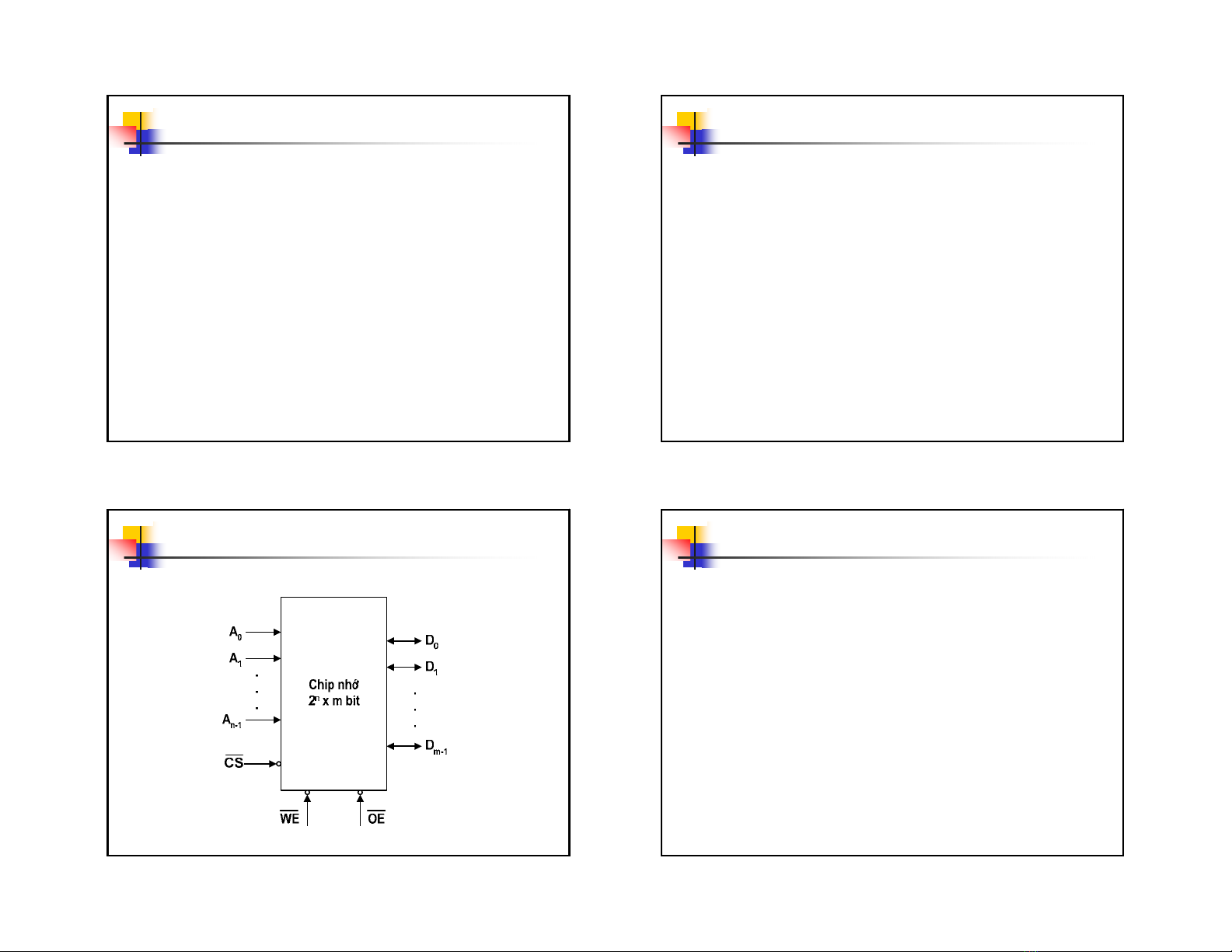

2. Tổchức của chip nhớ

Sơ đồ cơ bản của chip nhớ

8 September 2009 20

NKK-HUT

Các tín hiệu của chip nhớ

Các đường địa chỉ: An-1 ÷A0 Æcó 2ntừnhớ

Các đường dữliệu: Dm-1 ÷D0Æ độ dài từ

nhớ= m bit

Dung lượng chip nhớ= 2nxm bit

Các đường điều khiển:

Tín hiệu chọn chip CS (Chip Select)

Tín hiệu điều khiển đọc OE (Output Enable)

Tín hiệu điều khiển ghi WE (Write Enable)

(Các tín hiệu điều khiển thường tích cực với mức 0)

![Giáo trình Ngôn ngữ lập trình C: Phần 2 [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260424/vispacex_27/135x160/55231777433747.jpg)