Mạch khống chế nhiệt độ

2. SƠ LƯỢC VỀ CÁC PHƯƠNG PHÁP BIẾN ĐỔI AD

Tín hiệu trong thế giới thực thường ở dạng tương tự (analog), nên mạch điều

khiển thu thập dữ liệu từ đối tượng điều khiển về (thông qua các cảm biến) cũng ở

dạng tương tự. Trong khi đó, bộ điều khiển ngày nay thường là các μP, μC xử lý dữ

liệu ở dạng số (digital). Vì vậy, cần phải chuyển đổi tín hiệu ở dạng tương tự thành tín

hiệu ở dạng số thông qua bộ biến đổi AD.

Có nhiều phương pháp biến đổi AD khác nhau, ở đây chỉ giới thiệu một số

phương pháp điển hình.

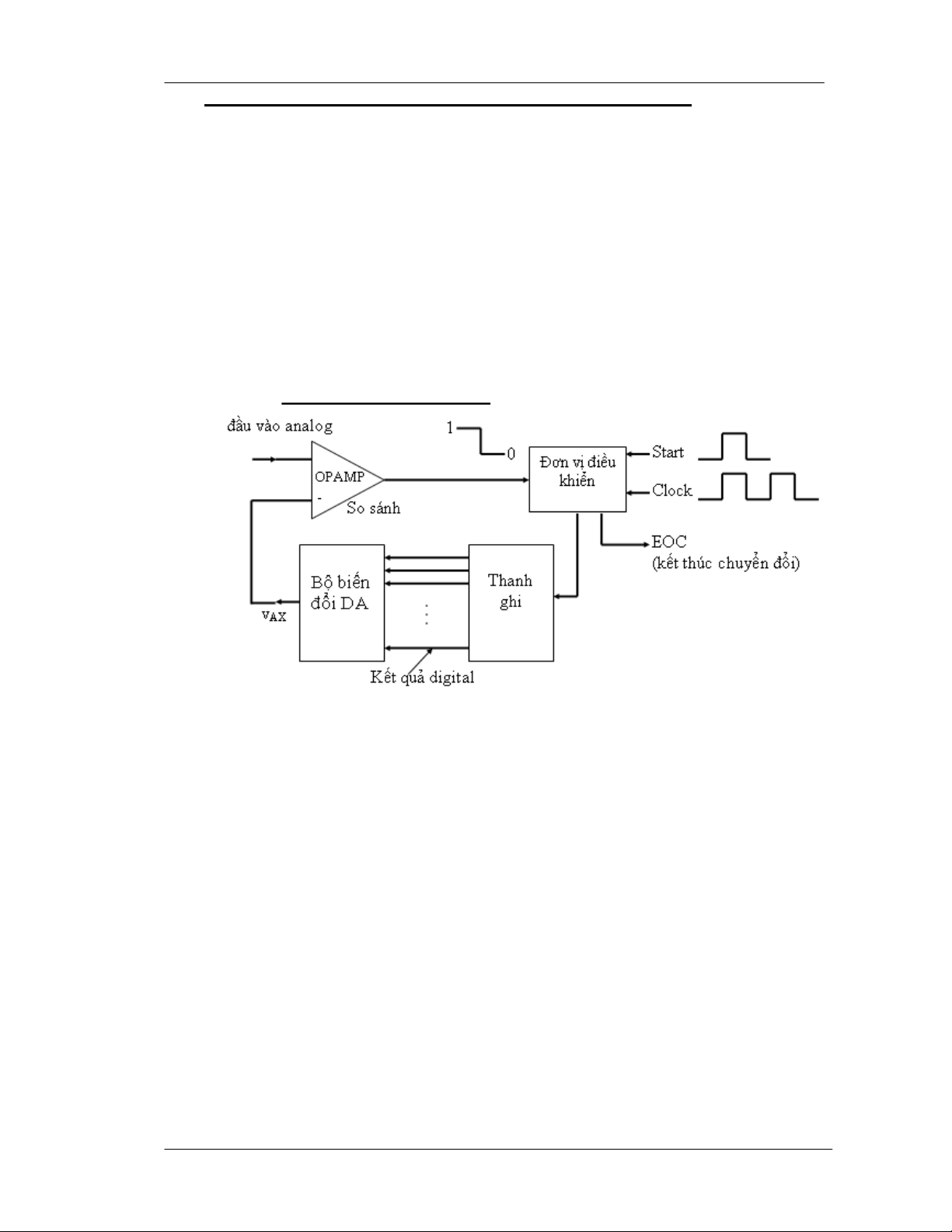

2.1. Biến đổi AD dùng bộ biến đổi DA.

Trong phương pháp này, bộ biến đổi DA được dùng như một thành phần trong

mạch. Khoảng thời gian biến đổi được chia bởi nguồn xung clock bên ngoài. Đơn vị

điều khiển là một mạch logic cho phép đáp ứng với tín hiệu Start để bắt đầu biến đổi.

Khi đó, OPAMP so sánh hai tín hiệu vào analog để tạo ra tín hiệu digital biến đổi trạng

thái của đơn vị điều khiển phụ thuộc vào tín hiệu analog nào có giá trị lớn hơn. Bộ

biến đổi hoạt động theo các bước :

• Tín hiệu Start để bắt đầu biến đổi.

• Cứ mỗi xung clock, đơn vị điều khiển sửa đổi số nhị phân đầu ra và đưa

vào lưu trữ trong thanh ghi.

• Số nhị phân trong thanh ghi được chuyển đổi thành áp analog vAX qua bộ

biến đổi DA.

• OPAMP so sánh vAX với điện áp đầu vào vA. Nếu vAX < vA thì đầu ra ở

mức cao, còn ngược lại, nếu vAX vượt qua vA một lượng vT (áp ngưỡng)

Mạch khống chế nhiệt độ

thì đầu ra ở mức thấp và kết thúc quá trình biến đổi. Ở thời điểm này,

vAX được xấp xỉ bằng vA số nhị phân chứa trong thanh ghi chính l giá trị

digital xấp xỉ của vA (theo một độ phân giải và chính xác nhất định của

từng hệ thống).

• Đơn vị điều khiển kích hoạt tín hiệu EOC, báo rằng được kết theo quá

trình biến đổi. Dựa theo phương pháp này, có nhiều bộ biến đổi như sau :

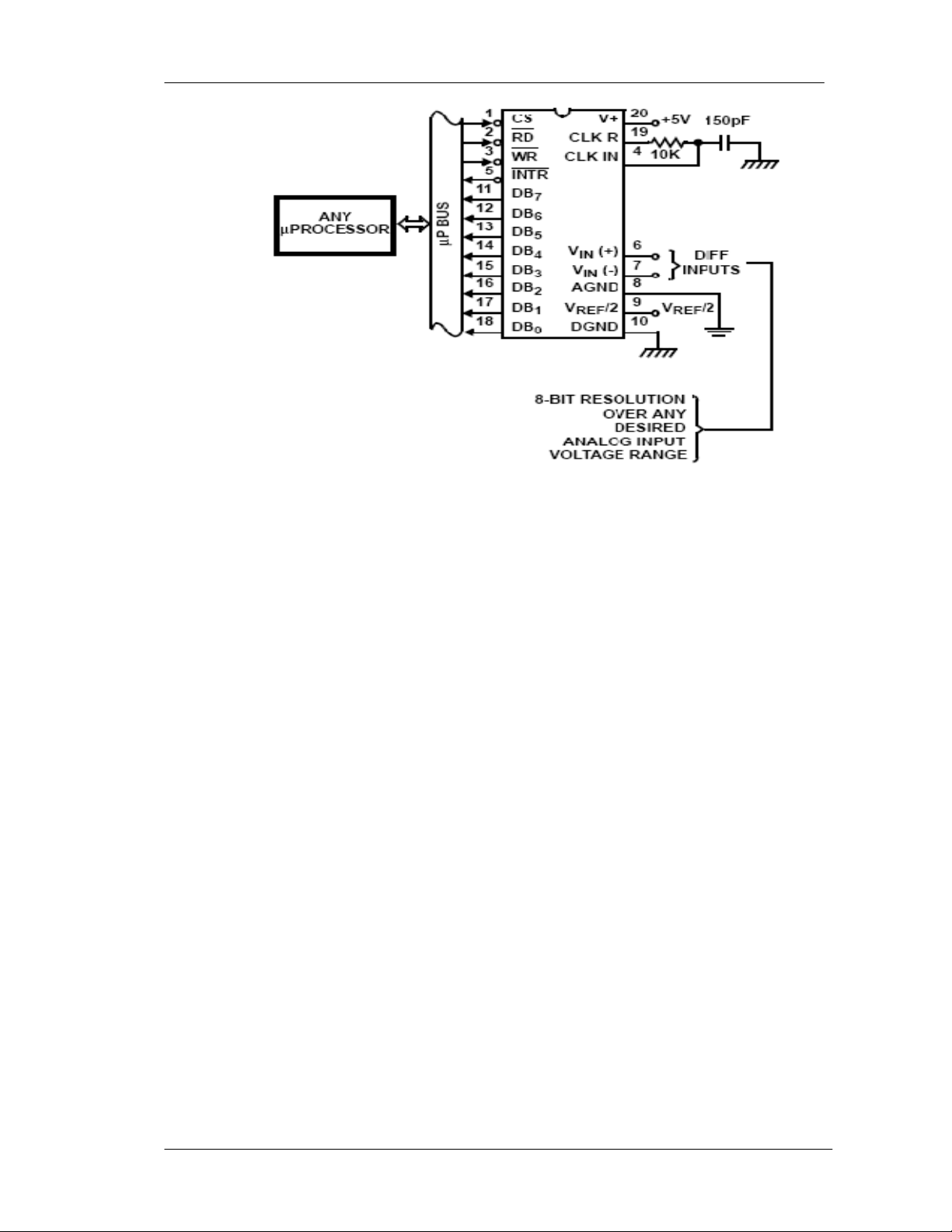

2.2. Giới thiệu về IC ADC 0804

Bộ ADC 0804 là một thiết bị CMOS tích hợp với một bộ chuyển đổi từ

tương tự sang số 8 bit, bộ chọn 1 kênh với một bộ logic điều khiển tương thích.

Bộ chuyển đổi AD 8 bit này dùng phương pháp chuyển đổi xấp xỉ tiếp.

Thiết bị này loại trừ khả năng cần thiết điều chỉnh điểm 0 bên ngoài và

khả năng điều chỉnh tỉ số làm tròn ADC 0804 dễ dàng giao tiếp với các bộ vi xử

lý.

• Sơ đồ chân ADC 0804:

+

-

vA

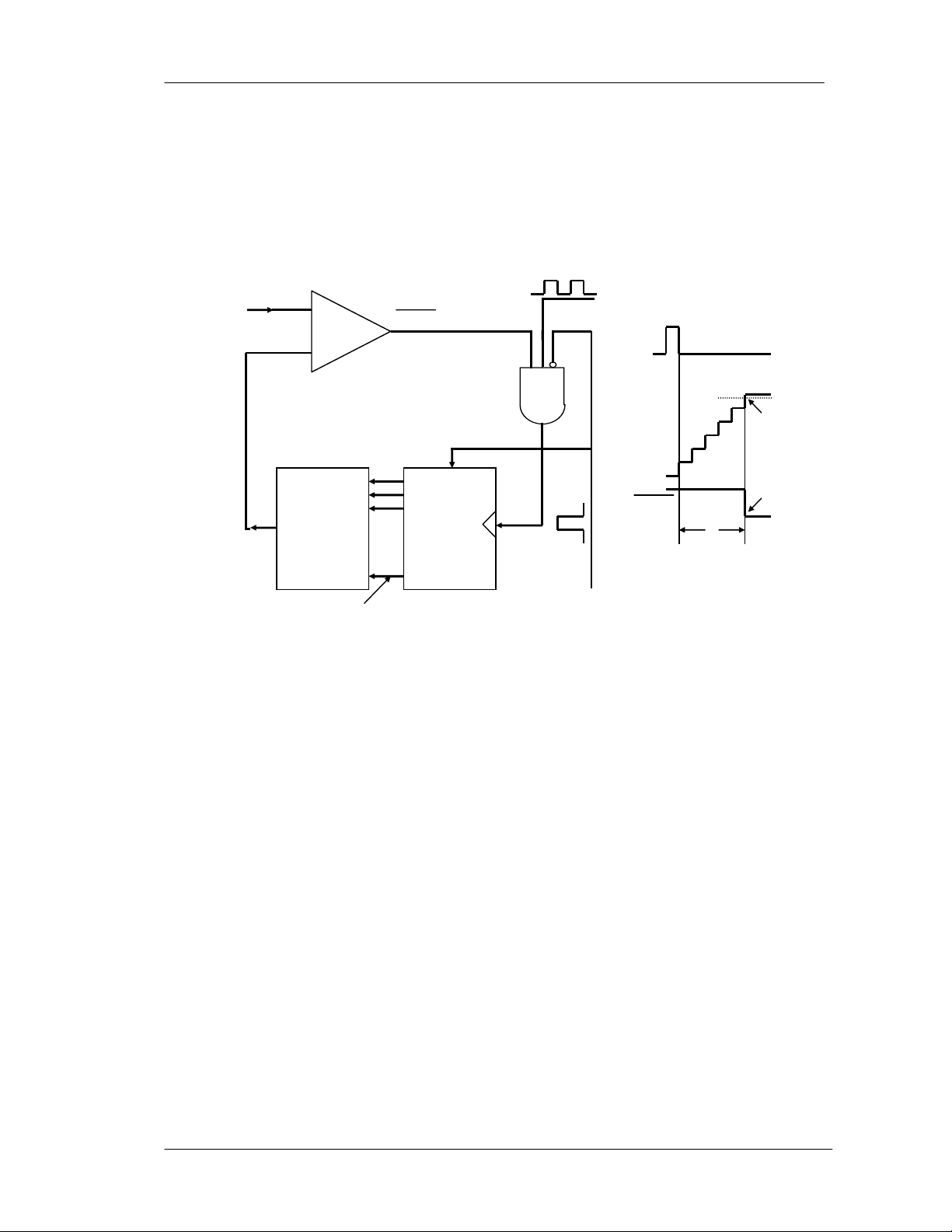

Đầu vào analog

Counter

Bộ biến

đổi DA

. . .

vAX

Kết quả digital

So snh

OPAMP

EOC

Start

Clock

Reset

Clock

vAX

Start

vA

EOC

tC

Khi chuyển

đổi hoàn tất,

counter

ngừng đếm

Mạch khống chế nhiệt độ

Chức năng các chân:

CS: Ngõ vào cho phép

RD,WR: Đọc ghi

INTR :cho phép chốt địa chỉ

DB0…DB7 : ngõ ra song song 8 bit

CLK : xung đồng hồ

VREF : điện thế tham chiếu

Vin+, Vin-: ngõ vào tương tự

VCC, GND: nguồn cung cấp

Các đặc điểm của ADC 0804:

Độ phân giải 8 bit

. Tổng sai số chưa chỉnh định ± ½ LSB; ± 1 LSB

. Thời gian chuyển đổi: 100μs ở tần số 640 kHz

. Nguồn cung cấp + 5V

. Điện áp ngõ vào 0 – 5V

. Tần số xung clock 10kHz – 1280 kHz

. Nhiệt độ hoạt động - 40oC đến 85oC

Mạch khống chế nhiệt độ

. Dễ dàng giao tiếp với vi xử lý hoặc dùng riêng

. Không cần điều chỉnh zero hoặc đầy thang

Nguyên lý hoạt động:

ADC 0804 có 1 vào tương tự để chuyển đổi sang số 8 bit.

Sau khi kích xung start thì bộ chuyển đổi bắt đầu hoạt động ở cạnh xuống

của xung INTR, lúc này bit cơ trọng số lớn nhất (MSB) được đặt lên mức 1, tất

cả các bit còn lại ở mức 0, đồng thời tạo ra điện thế có giá trị Vref/2, điện thế

này được so sánh với điện thế vào in.

+ Nếu Vin > Vref/2 thì bit MSB vẫn ở mức 1.

+ Nếu Vin < Vref/2 thì bit MSB vẫn ở mức 0.

Tương tự như vậy bit kế tiếp MSB được đặt lên 1 và tạo ra điện thế có giá

trị Vref/4 và cũng so sánh với điện áp ngõ vào Vin. Quá trình cứ tiếp tục như

vậy cho đến khi xác định được bit cuối cùng. Khi đó chân INTR lên mức 1 báo

cho biết đã kết thúc chuyển đổi.

Trong suốt quá trình chuyển đổi nếu có 1 xung start tác động thì ADC sẽ

ngưng chuyển đổi.

Mã ra N cho một ngõ vào tùy ý là một số nguyên.

)()(

)( ).(256

−+

−

−

−

=

refref

refIN

VV

VV

N

Trong đó Vin: điện áp ngõ vào hệ so sánh.

Vref(+): điện áp tại chân REF(+).

Vref(-): điện áp tại chân REF(-).

Nếu chọn Vref(-) = 0 thì N = 256.

V

ref(+) = Vcc = 5V thì đầy thang là 256.

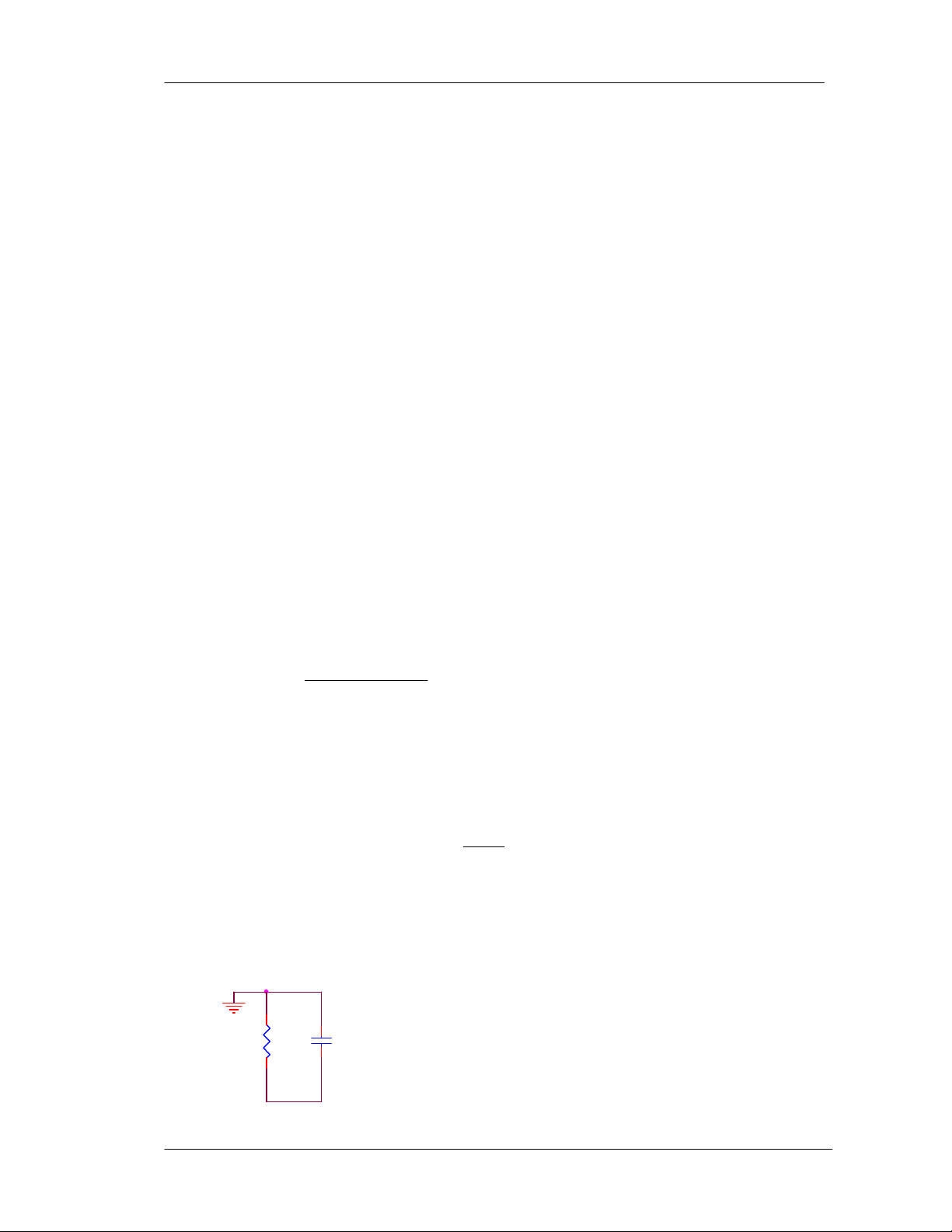

• Mạch tạo xung clock cho ADC 0804: Sử dụng mạch dao động dùng RC

để tạo dao động cho ADC như sau:

)(+ref

in

V

V

C1

100p

R1

10K

Mạch khống chế nhiệt độ

Tần số dao động của mạch là f = RC1.1

1

Tần số dao động chuẩn là 600 kHz đến 700Khz

Với R từ 1kΩ đến vài chục kΩ chọn R =15 kΩ ⇒ C = 100 pF

=> f = 93 10.100.10.15

1

−= 667Khz

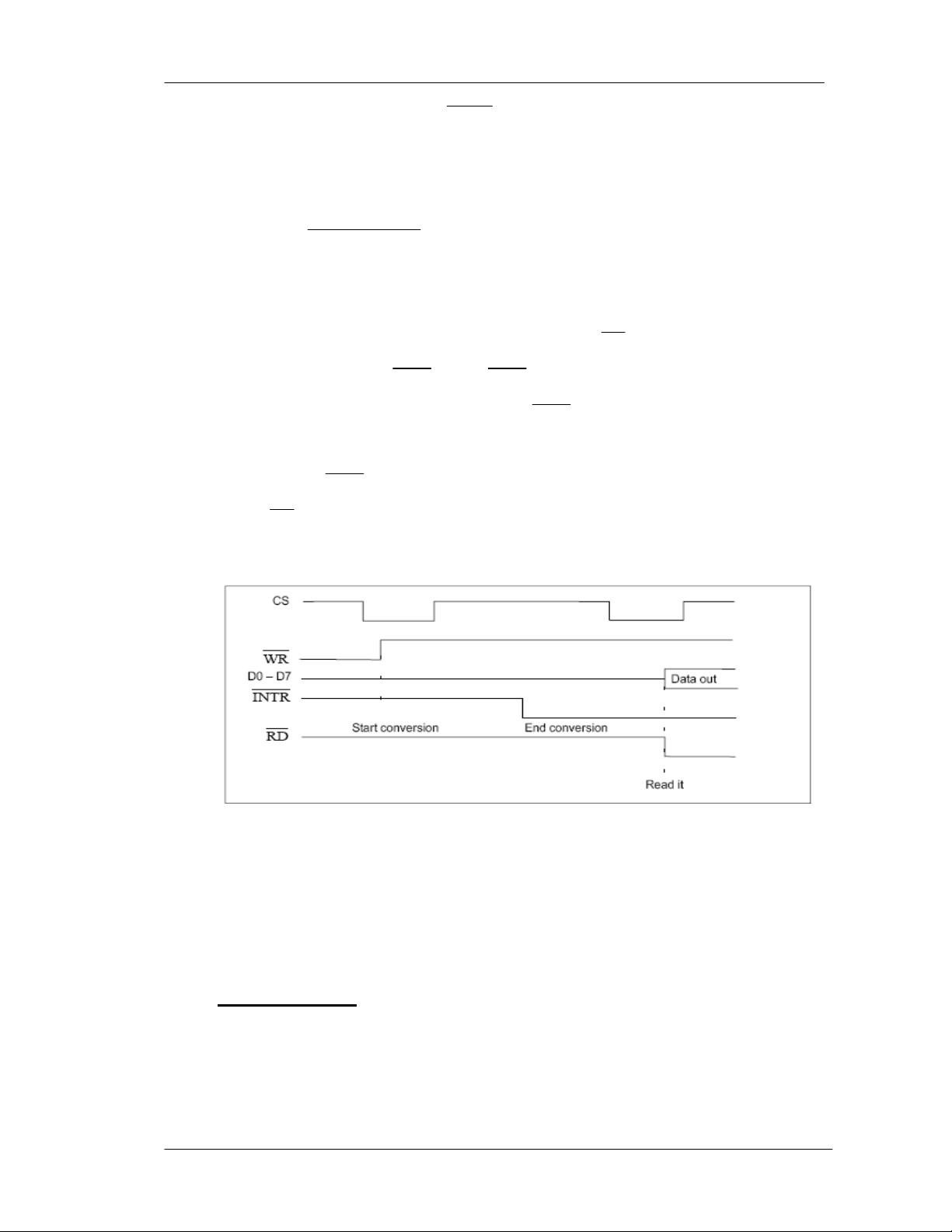

Từ những điều trên ta kết luận rằng các bước cần phải thực hiện khi chuyển đổi

dữ liệu bởi ADC0804 là:

9 Bật CS = 0 và gửi một xung thấp lên cao tới chân WR để bắt đầu chuyển đổi.

9 Duy trì hiển thị chân

I

NTR . Nếu

I

NTR xuống thấp thì việc chuyển đổi được

hoàn tất và ta có thể sang bước kế tiếp. Nếu

I

NTR cao tiếp tục thăm dò cho đến khi

nó xuống thấp.

9 Sau khi chân

I

NTR xuống thấp, ta bật CS = 0 và gửi một xung cao xuống thấp

đến chân

R

D để lấy dữ liệu ra khỏi chip ADC0804. Phân chia thời gian cho quá

trình này được trình bày như hình 8.

Hình 8: Phân chia thời gian đọc và ghi của ADC0804

CHƯƠNG 4

THIẾT KẾ PHẦN CỨNG

1.SƠ ĐỒ KHỐI

![Máy lạnh trung tâm (Central Air Conditioner Units) và ngành lạnh (Refrigeration): [Thông tin chi tiết/Hướng dẫn/ Tư vấn]](https://cdn.tailieu.vn/images/document/thumbnail/2012/20120202/luly_meo1/135x160/refrigeration_and_air_conditioning_equipment_cooling_split_2_9572.jpg)

![Mạch đo và khống chế nhiệt độ P2: Đề tài [Mô tả/Định tính]](https://cdn.tailieu.vn/images/document/thumbnail/2010/20100922/goixanh/135x160/mach_do_va_khong_che_nhiet_do_p2_6524.jpg)

![Giáo trình An toàn lao động, vệ sinh công nghiệp (Nghề Kỹ thuật máy lạnh và điều hòa không khí, Trình độ Cao đẳng) - Trường Cao đẳng Du lịch và Công thương [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260428/ronaldinho09/135x160/98891777571734.jpg)