B¸o c¸o tèt nghiÖp NguyÔn Duy Hoµng

Tr−êng §H N«ng nghiÖp I - 51 - T§H K46 - Khoa C¬ §iÖn

chöông trình con ñaõ ñöôïc goïi. Khi thöïc hieän xong chöông trình con vaø tröôùc

khi ñieàu khieån ñöôïc chuyeån trôû laïi chöông trình ñaõ goïi noù, noäi dung ngaên

xeáp ñaõ ñöôïc caát giöõ tröôùc ñoù seõ ñöôïc chuyeån trôû laïi ngaên xeáp.

Noäi dung cuûa thanh ghi AC khoâng ñöôïc caát giöõ khi goïi chöông trình

con, nhöng khi moät chöông trình xöû lyù ngaét ñöôïc goïi, noäi dung cuûa thanh ghi

AC seõ ñöôïc caát giöõ tröôùc khi thöïc hieän chöông trình xöû lyù ngaét vaø naïp laïi

khi chöông trình xöû lyù ngaét ñaõ ñöôïc thöïc hieän xong. Bôûi vaäy chöông trình

xöû lyù ngaét coù theå töï do söû duïng boán thanh ghi AC cuûa S7 – 200.

JMP, CALL

+ LBL, SBR : Leänh nhaûy JMP vaø leänh goïi chöông trình con SBR cho

pheùp chuyeån ñieàu khieån töø vò trí naøy ñeán moät vò trí khaùc trong chöông trình. Cuù

phaùp leänh nhaûy vaø leänh goïi chöông trình con trong LAD vaø STL ñeàu coù toaùn

haïng laø nhaõn chæ ñích (nôi nhaûy ñeán, nôi chöùa chöông trình con)

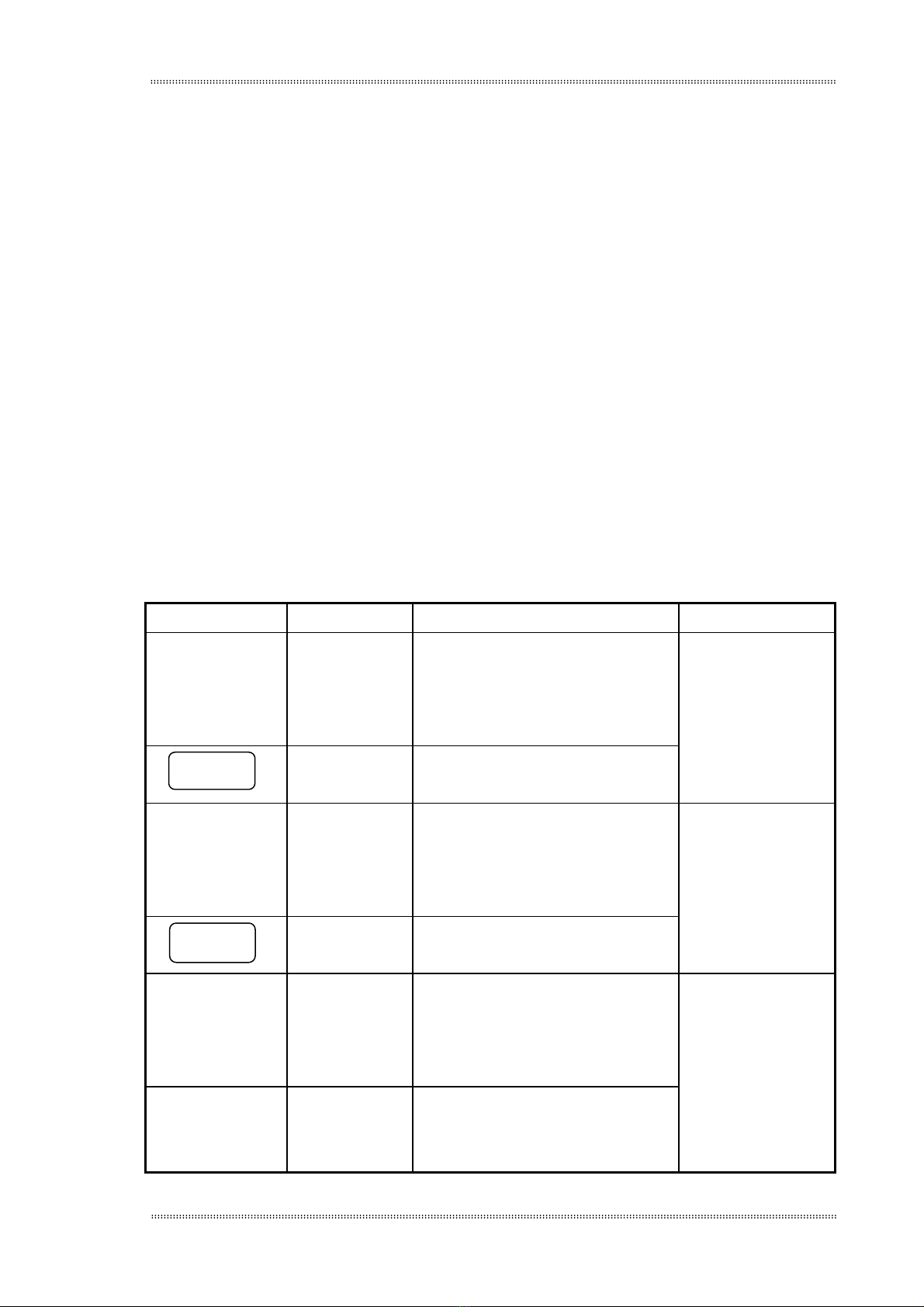

LAD STL Moâ taû Toaùn haïng

n

─( JMP)

JMP Kn

Leänh nhaûy thöïc hieän vieäc

chuyeån ñieàu khieån ñeán

nhaõn n trong moät chöông

trình.

JMP Kn

Leänh khai baùo nhaõn n trong

moät chöông trình.

n:

CPU 222: 0÷63

CPU 224:

0÷255

n

─( CALL)

CALL Kn

Leänh goïi chöông trình con,

thöïc hieän pheùp chuyeån

ñieàu khieån ñeán chöông

trình con coù nhaõn n.

SBR Kn Leänh gaùn nhaõn cho moät

chöông trình con.

n:

CPU 222: 0÷15

CPU 224:

0÷255

─( CRET)

CRET

Leänh trôû veà chöông trình

ñaõ goïi chöông trình con coù

ñieàu kieän (bit ñaàu cuûa ngaên

xeáp coù giaù trò logic baèng 1)

─( RET)

RET

Leänh trôû veà chöông trình

ñaõ goïi chöông trình con

khoâng ñieàu kieän.

Khoâng coù

LBL: n

SBR:n

B¸o c¸o tèt nghiÖp NguyÔn Duy Hoµng

Tr−êng §H N«ng nghiÖp I - 52 - T§H K46 - Khoa C¬ §iÖn

3.2.6. Caùc leänh can thieäp vaøo thôøi gian voøng queùt

MEND, END, STOP, NOP, WDR

Caùc leänh naøy ñöôïc duøng ñeå keát thuùc chöông trình ñang thöïc hieän, vaø

keùo daøi moät khoaûng thôøi gian cuûa moät voøng queùt.

Trong LAD vaø STL chöông trình phaûi ñöôïc keát thuùc baèng

leänh keát

thuùc khoâng ñieàu kieän

MEND. Coù theå söû duïng leänh keát thuùc coù ñieàu kieän

END tröôùc leänh keát thuùc khoâng ñieàu kieän.

Leänh STOP keát thuùc chöông trình, noù chuyeån ñieàu khieån chöông trình

ñeán cheá ñoä STOP. Neáu nhö gaëp leänh STOP trong chöông trình chính, hoaëc

trong chöông trình con thì chöông trình ñang ñöôïc thöïc hieän seõ keát thuùc

ngay laäp töùc.

Leänh roãng NOP khoâng coù taùc duïng gì trong vieäc thöïc hieän chöông

trình. Caàn löu yù leänh NOP phaûi ñöôïc ñaët beân trong chöông trình chính,

chöông trình con hoaëc trong chöông trình xöû lyù ngaét.

Leänh WDR seõ khôûi ñoäng laïi ñoàng hoà quan saùt (

watchdog timer

), vaø

chöông trình tieáp tuïc ñöôïc thöïc hieän trong voøng queùt ôû cheá ñoä quan saùt neân

caån thaän khi söû duïng leänh WDR.

Vieäc chuyeån coâng taéc cöùng cuûa S7 – 200 vaøo vò trí STOP hoaëc thöïc

hieän leänh STOP trong chöông trình seõ laø nguyeân nhaân ñaët ñieàu khieån vaøo

cheá ñoä döøng trong khoaûng thôøi gian 1,4s ...

3.2.7. Caùc leänh ñieàu khieån Timer

Timer laø boä taïo thôøi gian giöõa tín hieäu ra neân trong ñieàu khieån vaãn

thöôøng ñöôïc goïi laø

khaâu treã

. Neáu kyù hieäu tín hieäu (logic) vaøo laø x(t) vaø thôøi gian

treã taïo ra baèng Timer laø τ thì tín hieäu ñaàu ra cuûa Timer ñoù seõ laø x(t – τ)

S7 – 200 coù 256 Timer (vôùi CPU 224) ñöôïc chia laøm hai loaïi khaùc

nhau laø:

+ Timer taïo thôøi gian treã khoâng coù nhôù (On-Delay Timer), kyù hieäu laø TON.

+ Timer taïo thôøi gian treã coù nhôù (Retentive On-Delay Timer), kyù hieäu laø

TONR.

B¸o c¸o tèt nghiÖp NguyÔn Duy Hoµng

Tr−êng §H N«ng nghiÖp I - 53 - T§H K46 - Khoa C¬ §iÖn

Hai kieåu Timer cuûa S7 – 200 (TON vaø TONR) phaân bieät vôùi nhau ôû

phaûn öùng cuûa noù ñoái vôùi traïng thaùi ñaàu vaøo.

Caû hai Timer kieåu TON vaø TONR cuøng baét ñaàu taïo thôøi gian treã tín

hieäu keå töø thôøi ñieåm coù söôøn leân ôû tín hieäu ñaàu vaøo, töùc laø khi tín hieäu ñaàu

vaøo chuyeån traïng thaùi logic töø 0 leân 1, ñöôïc goïi laø

thôøi gian Timer ñöôïc

kích

, vaø khoâng tính khoaûng thôøi gian khi ñaàu vaøo coù giaù trò logic 0 vaøo thôøi

gian treã tín hieäu ñaët tröôùc.

Khi ñaàu vaøo coù giaù trò logic baèng 0, TON töï ñoäng reset coøn TONR

thì khoâng töï ñoäng reset. Timer TON ñöôïc duøng ñeå taïo thôøi gian treã trong

moät khoaûng thôøi gian (mieàn lieân thoâng), coøn vôùi TONR thôøi gian treã seõ

ñöôïc taïo ra trong nhieàu khoaûng thôøi gian khaùc nhau.

Timer TON vaø TONR bao goàm 3 loaïi vôùi ba ñoä phaân giaûi khaùc nhau,

ñoä phaân giaûi 1ms, 10ms vaø 100ms. Thôøi gian treã τ ñöôïc taïo ra chính laø tích

cuûa ñoä phaân giaûi cuûa boä Timer ñöôïc choïn vaø giaù trò ñaët tröôùc cho Timer. Ví

duï Timer coù ñoä phaân giaûi 10ms vaø giaù trò ñaët tröôùc laø 50 thì thôøi gian treã seõ

laø τ = 500ms.

Timer cuûa S7 – 200 coù nhöõng tính chaát cô baûn sau:

+ Caùc boä Timer ñöôïc ñieàu khieån bôûi moät coång vaøo vaø giaù trò ñeám

töùc thôøi. Giaù trò ñeám töùc thôøi cuûa Timer ñöôïc nhôù trong thanh ghi 2 byte

(goïi laø T-word) cuûa Timer, xaùc ñònh khoaûng thôøi gian treã keå töø khi Timer

ñöôïc kích. Giaù trò ñaët tröôùc cuûa caùc boä Timer ñöôïc kyù hieäu trong LAD vaø

STL laø PT. Giaù trò ñeám töùc thôøi cuûa thanh ghi T-word thöôøng xuyeân ñöôïc so

saùnh vôùi giaù trò ñaët tröôùc cuûa Timer.

+ Moãi boä Timer, ngoaøi thanh ghi 2 byte T-word löu giaù trò ñeám töùc

thôøi, coøn coù moät bit kyù hieäu laø T-bit, chæ thò traïng thaùi logic ñaàu ra. Giaù trò

logic cuûa bit naøy phuï thuoäc vaøo keát quaû so saùnh giöõa giaù trò ñeám töùc thôøi

vôùi giaù trò ñaët tröôùc.

+ Trong khoaûng thôøi gian tín hieäu x(t) coù giaù trò logic 1, giaù trò ñeám

töùc thôøi trong T-word luoân ñöôïc caäp nhaät vaø thay ñoåi taêng daàn cho ñeán khi

B¸o c¸o tèt nghiÖp NguyÔn Duy Hoµng

Tr−êng §H N«ng nghiÖp I - 54 - T§H K46 - Khoa C¬ §iÖn

noù ñaït giaù trò cöïc ñaïi. Khi giaù trò ñeám töùc thôøi lôùn hôn hay baèng giaù trò ñaët

tröôùc, T-bit coù giaù trò logic 1.

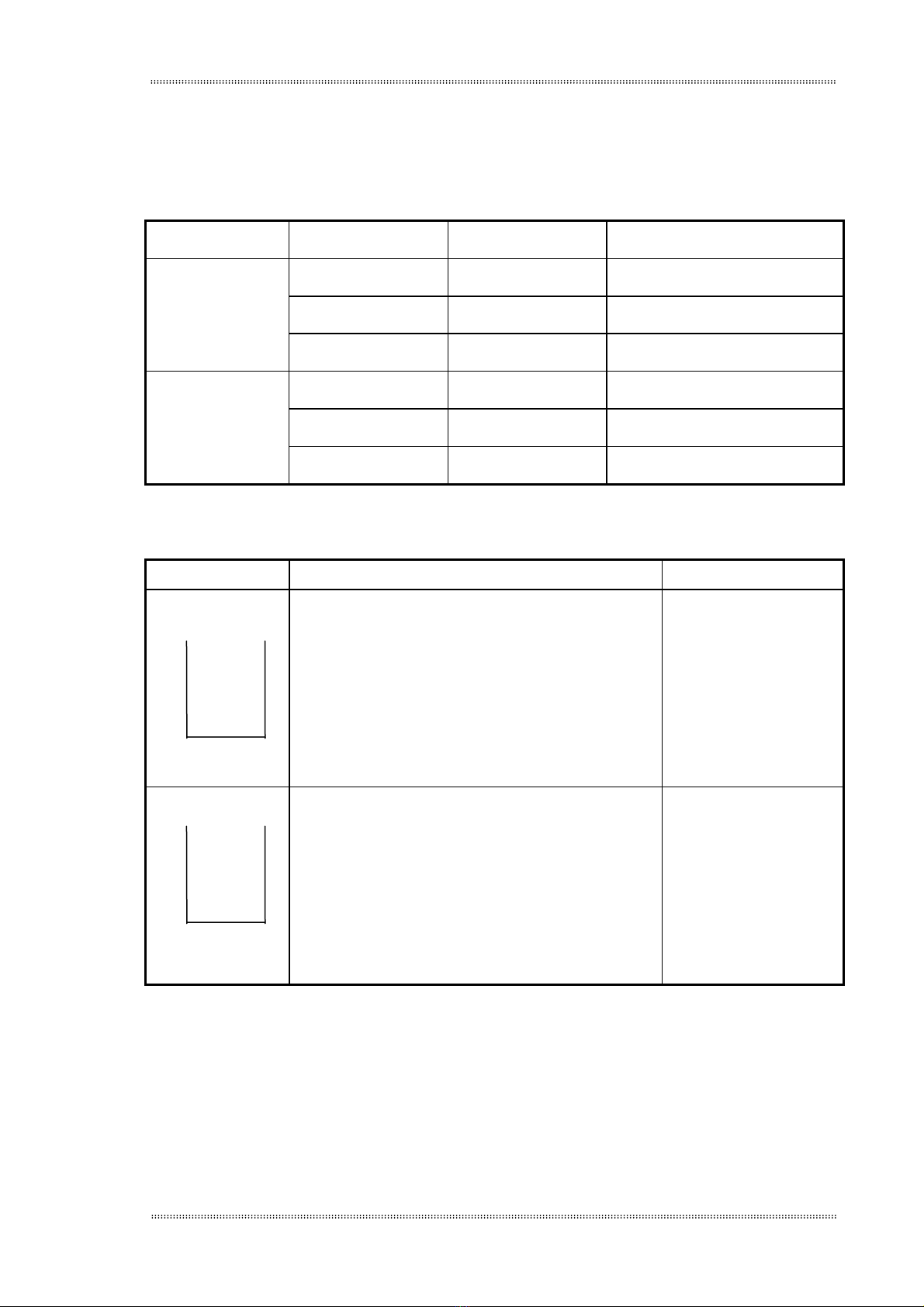

Ñoä phaân giaûi caùc loaïi Timer cuûa S7 – 200, CPU 224

Leänh Ñoä phaân giaûi Giaù trò cöïc ñaïi CPU 224

1 ms 32,767 s T32 vaø T96

10 ms 327,67 s T33 ÷ T36, T97 ÷ T100

TON

100 ms 3276,7 s T32 ÷ T96, T101 ÷ T127

1 ms 32,767 s T0 vaø T64

10 ms 327,67 s T1 ÷ T4, T65 ÷ T68

TONR

100 ms 3276,7 s T5 ÷ T31, T69 ÷ T95

Cuù phaùp khai baùo söû duïng Timer nhö sau:

LAD Moâ taû Toaùn haïng

TON—Txx

— IN

— PT

Khai baùo Timer soá hieäu xx kieåu TON ñeå

taïo thôøi gian treã tính töø khi ñaàu vaøo IN

ñöôïc kích. Neáu nhö giaù trò ñeám töùc thôøi

lôùn hôn hoaëc baèng giaù trò ñaët tröôùc PT thì

T-bit coù giaù trò logic baèng 1. coù theå reset

Timer kieåu TON baèng leänh R hoaëc baèng

giaù trò logic 0 taïi ñaàu vaøo IN.

Txx (

word

)

CPU224:32÷63

96÷127

PT: VW, T,

(

word

) C, IW,

QW,MW,SMW,

AC,AIW,haèngsoá

TONR—Txx

— IN

— PT

Khai baùo Timer soá hieäu xx kieåu TONR

ñeå taïo thôøi gian treã tính töø khi ñaàu vaøo

IN ñöôïc kích. Neáu nhö giaù trò ñeám töùc

thôøi lôùn hôn hoaëc baèng giaù trò ñaët tröôùc

PT thì T-bit coù giaù trò logic baèng 1. Chæ

coù theå reset Timer kieåu TON baèng leänh

R cho T-bit.

Txx (

word

)

CPU224: 0 ÷31

64 ÷95

PT: VW, T,

(

word

) C, IW,

QW,MW,SMW,

AC,AIW,haèngsoá

Khi söû duïng Timer kieåu TONR, giaù trò ñeám töùc thôøi ñöôïc löu laïi vaø

khoâng bò thay ñoåi trong khoaûng thôøi gian khi tín hieäu ñaàu vaøo coù logic 0.

Giaù trò cuûa T-bit khoâng ñöôïc nhôù maø hoaøn toaøn phuï thuoäc vaøo keát quaû so

saùnh giöõa giaù trò ñeám töùc thôøi vaø giaù trò ñaët tröôùc.

B¸o c¸o tèt nghiÖp NguyÔn Duy Hoµng

Tr−êng §H N«ng nghiÖp I - 55 - T§H K46 - Khoa C¬ §iÖn

Khi reset moät boä Timer, T-word vaø T-bit cuûa noù ñoàng thôøi ñöôïc xoùa

vaø coù giaù trò baèng 0, nhö vaäy giaù trò ñeám töùc thôøi ñöôïc ñaët veà 0 vaø tin hieäu

ñaàu ra cuõng coù traïng thaùi logic baèng 0.

3.2.8. Caùc leänh ñieàu khieån Counter

Counter laø boä ñeám thöïc hieän chöùc naêng ñeám söôøn xung trong S7 –

200. Caùc boä ñeám cuûa S7 – 200 ñöôïc chia laøm hai loaïi: boä ñeám tieán (CTU)

vaø boä ñeám tieán/luøi (CTUD).

Boä ñeám tieán CTU ñeám soá söôøn leân cuûa tín hieäu logic ñaàu vaøo, töùc laø

ñeám soá laàn thay ñoåi traïng thaùi logic töø 0 leân 1 cuûa tín hieäu. Soá xung ñeám

ñöôïc, ñöôïc ghi vaøo thanh ghi 2 byte cuûa boä ñeám, goïi laø thanh ghi C-word.

Noäi dung cuûa thanh ghi C-word, goïi laø giaù trò ñeám töùc thôøi cuûa boä

ñeám, luoân ñöôïc so saùnh vôùi giaù trò ñaët tröôùc cuûa boä ñeám, ñöôïc kyù hieäu laø

PV. Khi giaù trò ñeám töùc thôøi baèng hoaëc lôùn hôn giaù trò ñaët tröôùc naøy thì boä

ñeám baùo ra ngoaøi baèng caùch ñaët giaù trò logic 1 vaøo moät bit ñaëc bieät cuûa noù,

goïi laø C-bit. Tröôøng hôïp giaù trò ñeám töùc thôøi nhoû hôn giaù trò ñaët tröôùc C-bit

coù giaù trò logic laø 0.

Khaùc vôùi caùc boä Timer, caùc boä ñeám CTU vaø CTUD ñeàu coù chaân noái

vôùi tín hieäu ñieàu khieån xoùa ñeå thöïc hieän vieäc ñaët laïi cheá ñoä khôûi phaùt ban

ñaàu (reset) cho boä ñeám, ñöôïc kyù hieäu baèng chöõ caùi R trong LAD, hay ñöôïc

qui ñònh laø traïng thaùi logic cuûa bit ñaàu tieân cuûa ngaên xeáp trong STL. Boä

ñeám ñöôïc reset khi tín hieäu xoaù naøy coù möùc logic laø 1 hoaëc khi leänh R

(reset) ñöôïc thöïc hieän vôùi C-bit. Khi boä ñeám ñöôïc reset, caû C-word vaø C-bit

ñeàu nhaän giaù trò 0.

Boä ñeám tieán/luøi CTUD ñeám tieán khi gaêp söôøn leân cuûa xung vaøo

coång ñeám tieán, kyù hieäu laø CU hoaëc bit thöù 3 cuûa ngaên xeáp trong STL, vaø

ñeám luøi khi gaëp söôøn leân cuûa xung vaøo coång ñeám luøi, kyù hieäu laø CD trong

LAD hoaëc bit thöù 2 cuûa ngaên xeáp trong STL.

Boä ñeám tieán CTU coù mieàn giaù trò ñeám töùc thôøi töø 0 ñeán 32.767. Boä

ñeám tieán/luøi CTUD coù mieàn giaù trò ñeám töùc thôøi töø –32.768 ñeán 32.767.

![Tài liệu thực hành Công nghệ đúc nâng cao [chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250506/vimitsuki/135x160/1953715870.jpg)

![Cơ sở gang thép tốt nhất: [Năm hiện tại] Cập nhật mới nhất](https://cdn.tailieu.vn/images/document/thumbnail/2014/20141002/vuloi11a1/135x160/1716647_2510.jpg)

![Công nghệ đúc áp lực: [Thêm từ khóa hoặc cụm từ liên quan để tối ưu SEO]](https://cdn.tailieu.vn/images/document/thumbnail/2014/20140926/xuantin179/135x160/1715252_366.jpg)

![Bài giảng Ứng dụng tin học trong Kỹ thuật phương tiện thủy [chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251216/anhquangvu03@gmail.com/135x160/12021765937860.jpg)

![Bài tập tối ưu trong gia công cắt gọt [kèm lời giải chi tiết]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251129/dinhd8055/135x160/26351764558606.jpg)