2009

dce

Thiết kế mạch số dùng HDL

Chương 1: Phương pháp luận thiết kế vi

mạch số

Computer Engineering 2009

©2009, Pham Quoc Cuong 2

Advanced Digital Design with the Verilog HDL –

chapter 1

Nội dung chính

•Phương pháp luận thiết kế

•Tham số công nghệ vi mạch

Computer Engineering 2009

©2009, Pham Quoc Cuong 3

Advanced Digital Design with the Verilog HDL –

chapter 1

Nội dung chính

•Phương pháp luận thiết kế

•Tham số công nghệ vi mạch

Computer Engineering 2009

©2009, Pham Quoc Cuong 4

Advanced Digital Design with the Verilog HDL –

chapter 1

Các xu hướng thiết kế

•Thiết kế cổ điển (classical design methods)

Dựa trên giản đồ (schematic)

Paper & pencil

•Thiết kế bằng ngôn ngữ (computer-based

languages methods)

Nhanh chóng

Mạch tích hợp hàng triệu cổng

Được sử dụng rộng rãi thiết kế các mạch

phức tạp và kích thước lớn

Computer Engineering 2009

©2009, Pham Quoc Cuong 5

Advanced Digital Design with the Verilog HDL –

chapter 1

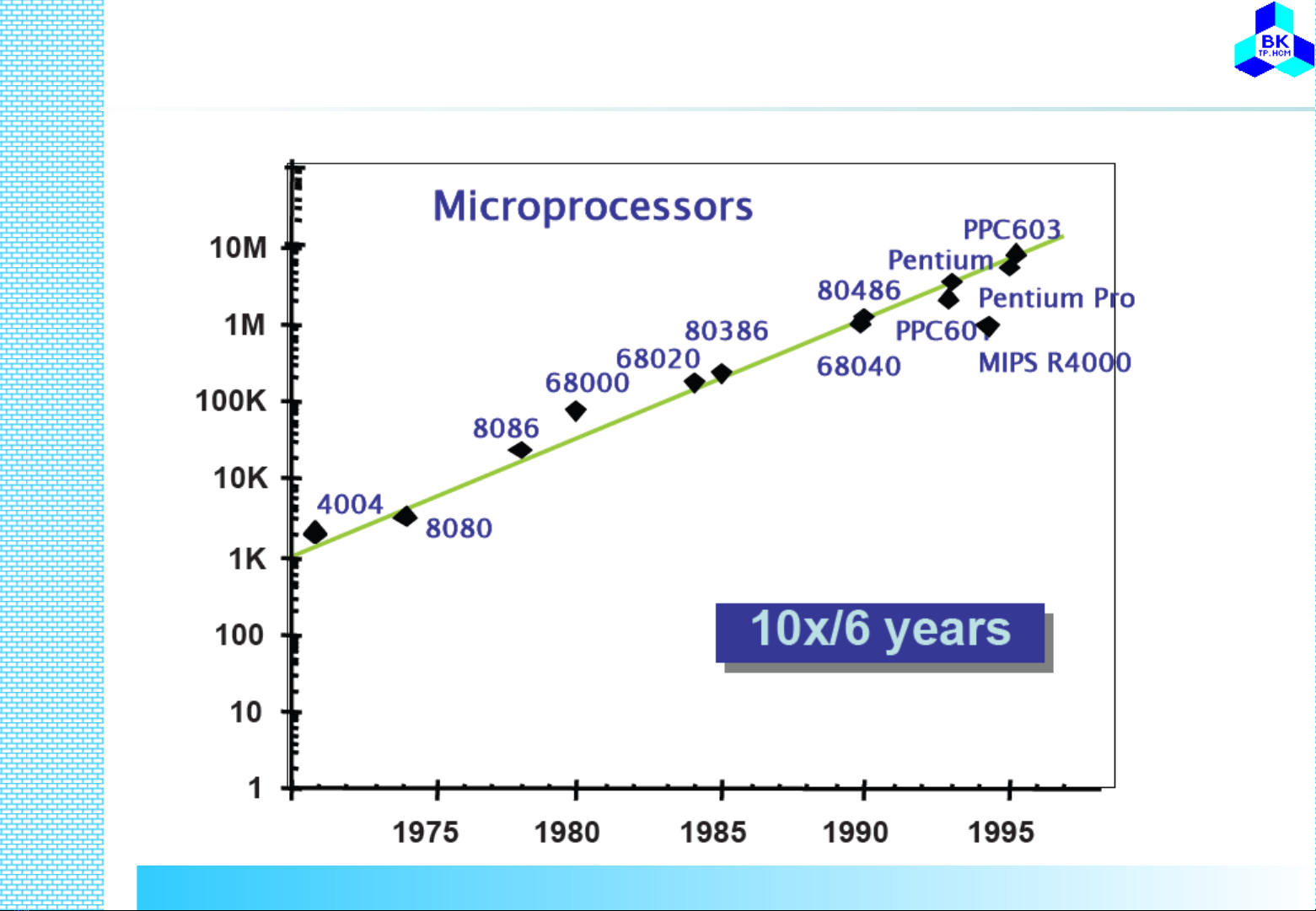

Định luật Moore