1

P&I Ch3: Methodes 1

CH. 3. CÁC PHƯƠNG PHÁP

TRAO ĐỔI THÔNG TIN

•Polling - Thăm dò

•Interrupt - ngắt &

•DMA - truy nhập trực tiếp mem - IO

P&I Ch3: Methodes 2

3.1. Phương pháp thăm dò (polling)

• K/n Polling: Dùng phần mềmđể kiểm tra các cờtrạng

thái @ IO Ports => quyếtđịnh trao đổi sốliệu hay

không.

• Nhanh, đơn giản, thường dùng trong các hệnhỏhoặc

đơn nhiệm - ít thiết bịIO,

• Tốt cho việc thửnghiệm,

• Có thể đa nhiệm cho các đốitượng có hằng sốthời gian

>>, các thiết bịngoại vi tần suất truy nhập thấp, tốcđộ

chậm. Ví dụcác kênh đo nhiệtđộ,

• Không phù hợp với ‘đa nhiệm’, đặc biệt trong máy tính

2

P&I Ch3: Methodes 3

Ví dụvềPP polling

• Cổng Comm (RS232) của máy tính PC:

– Thanh ghi Line Status Register có các bit:

• b0 – Char received, đã thu xong 1 char,

• b1 – Overrun Error, char bịxóa đè

• b2 – Parity Error

• b3 – Framing Error

• B4 – Break Interrupt

• B5 – TxHR Empty, thanh ghi phát rỗng, gửi tiếp

• B6 – Char transmitted

– Polling: thu - kiểm tra b0, phát kiểm tra – b5

P&I Ch3: Methodes 4

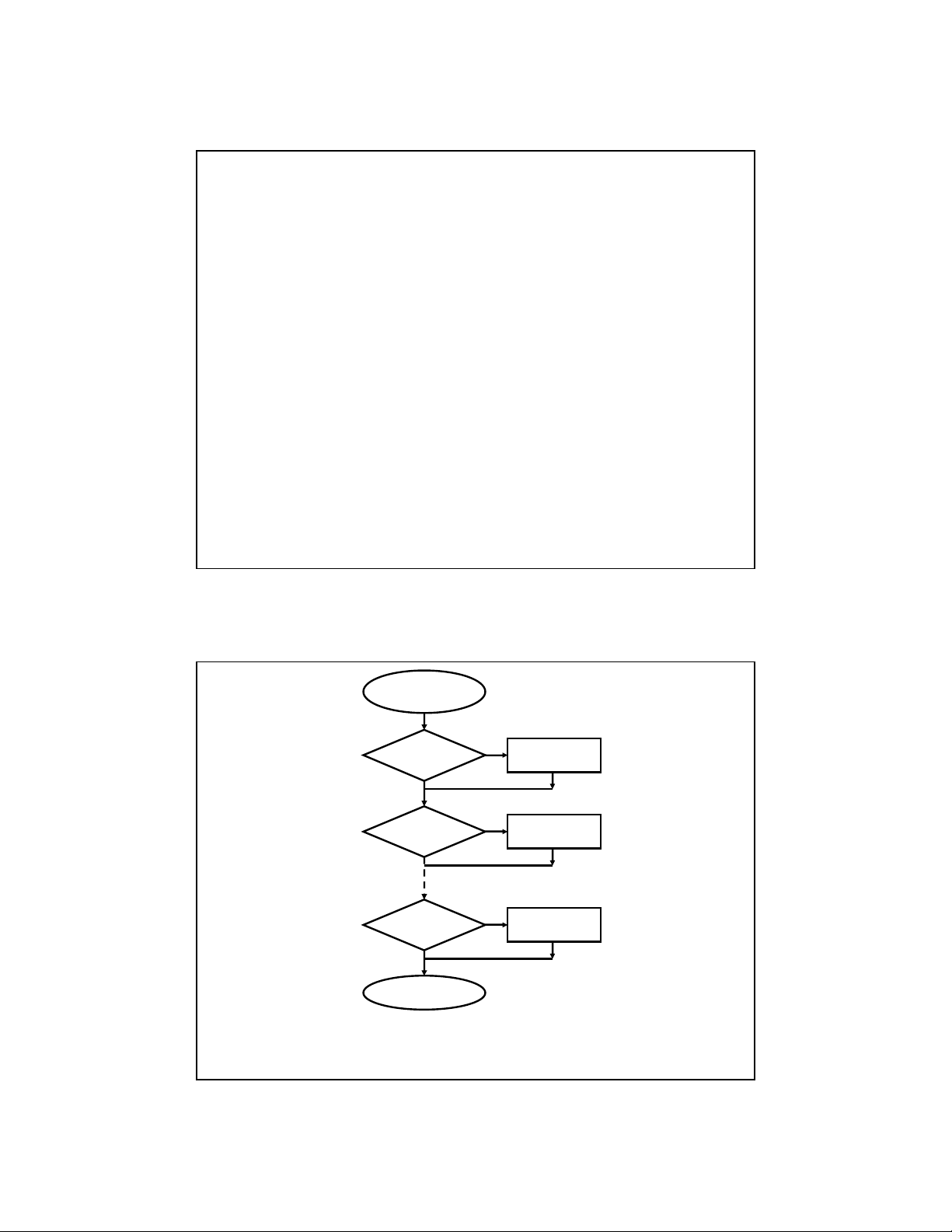

Mộtlưu đồ

thăm dò:

Polling

Device #1 Y

Request ?

N

Device #2 Y

Request ?

N

Device #n Y

Request ?

N

Device #1

Service Routine

Device #2

Service Routine

Device #n

Service Routine

Quit

Hình 3.1. Lưu đồ phương pháp

IO interface polling

3

P&I Ch3: Methodes 5

3.2. Phương pháp ngắt (Interrupt)

•Khái niệm,

•Phân loại và

•Case studies

P&I Ch3: Methodes 6

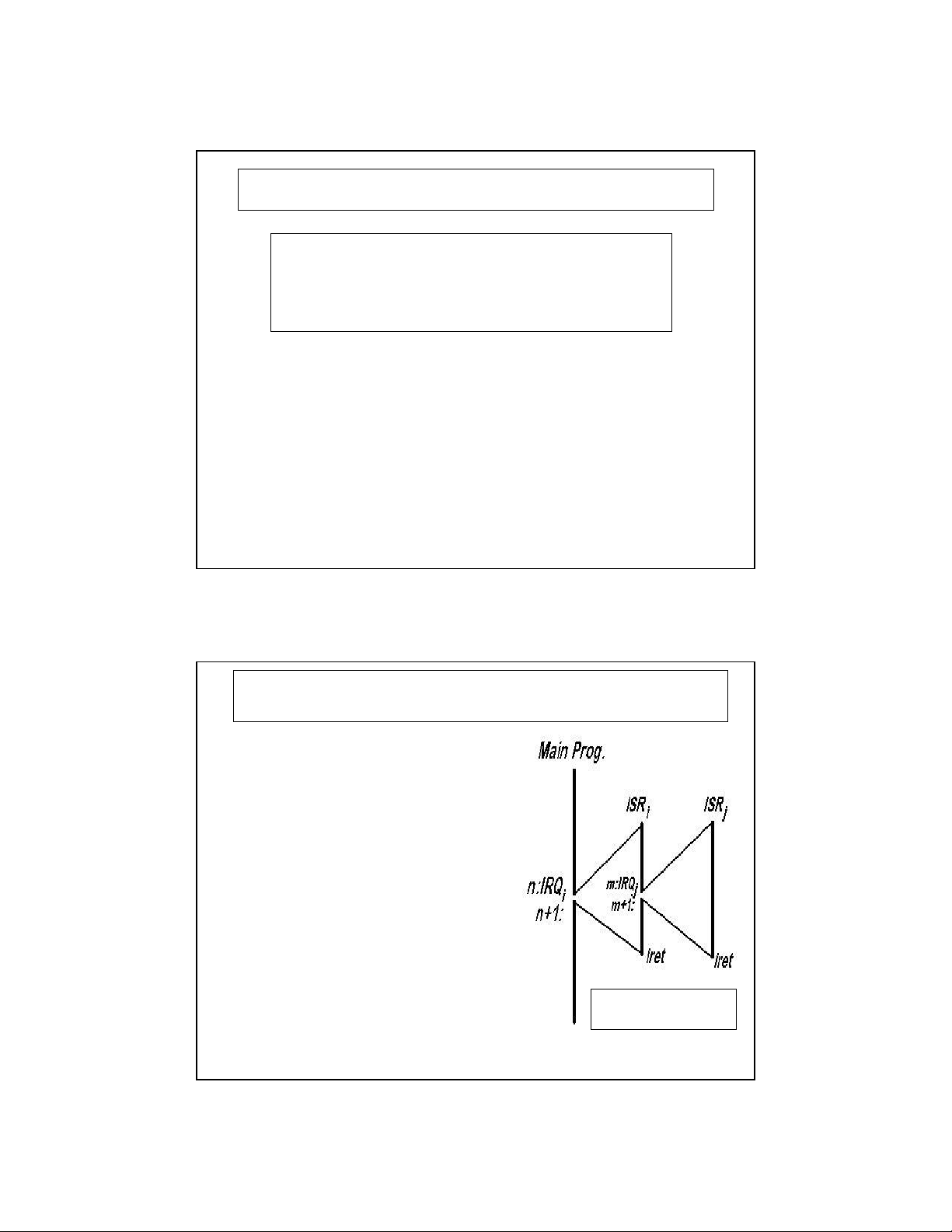

• Là sựdừng thực hiện CTC để thực hiện

ctc, thường là do TBNV yêu cầu thông

qua port.

• Khi CPU đang thực hiện CTC, đến dòng

lệnh thứn, ngẫu nhiên, ngoại vi thứi xin

phục vụbằng cách phát ra tín hiệu IRQ(i)

(Interrupt Request) đến CPU. Nói chung,

CPU sẽngừng xửlý CTC và cất ngữcảnh

(flags và địa chỉcủa lệnh tiếp theo) vào

Stack Mem, rồi tìm địa chỉcủa ctc phục

vụngắttương ứng (Interrupt Service

Routine - ISR) để thực hiện.

• Sau khi thực hiện xong ISR, gặp lệnh iret

(reti...), CPU khôi phục lại ngữcảnh (từ

Stack Mem) của CTC và tiếp tục thực

hiện.

3.2. Phương pháp ngắt (Interrupt):

3.2.1. Khái niệm

H×nh 3.2. K/n

ng¾t

4

P&I Ch3: Methodes 7

•Đặcđiểm:

– Là phương pháp vào/ra kết hợp tín hiệu và phần mềm,

để thực hiệnđa nhiệm.

–Đốitượng bịngắt: CTC bịdừng xửlý để thực hiện ctc.

– Là chế độ hoạtđộng riêng cho các Vi xửlý/ máy tính

ON-LINE,

– Nguồn ngắt: chủyếu từngoại vi thông qua IO ports,

CPU (exceptions, internal),

– Xảy ra ngẫu nhiên,

– Nhiều IOs

• => Tranh chấp => Phải giải quyếtưu tiên ngắt.

3.2. Phương pháp ngắt (Interrupt):

3.2.1. Khái niệm:

P&I Ch3: Methodes 8

•Ưu tiên ngắt - Interrupt Priority:

- T/bị ưu tiên cao có thểdừng ISR của t/bị ưu tiên thấp

- Hệlớn, nhiều IOs thường dùng PIC (Intel PIC8259A)

- Chỉsố ưu tiên do nhà sx qui định cho các t/bịngoại vi, cố

định, mức 0 là cao nhất.

Theo hình 3.2: Level (j) > Level(i),

i>j.

•Ưu tiên phân định do các tín hiệu ngắt trong CPU (Intel 8085:

INTR, 5.5, 6.5, 7.5 và TRAP),

• Z80 CPU & others: ưu tiên theo kiểu Daisy Chain

3.2. Interrupt: 3.2.1. Khái niệm

5

P&I Ch3: Methodes 9

a. Software Interrupt:

• Là việc gọi 1 ctc (Subroutine) được xây dựng riêng mà ctc

này còn có thể được gọi bởi thiết bịngoại vi.

• Các lệnh gọinhư INT n; (Intel x86) hay SWI n; (Moto).

• Tuy nhiên, việc thực hiện lệnh ngắt mềm giống như gọi thủ

tục, và đôi khi được hiểu là TRAP,

• Ngắt mềm không phải là ngắt

3.2. Interrupt: 3.2.2. Phân loại:

(Hardware, software, internal, exception, NMI...)

P&I Ch3: Methodes 10

• Do Ports phát tín hiệu NMI/ IRQ đến CPU.

• Chia thành 2 loại: Maskable & Non Maskable

Maskable Interrupt: là các ngắt thông thường, có thểcấm

(disable) bởi lệnh CLI hay cho phép (enable) bởi lệnh STI

(Intel vs Moto!).

Các ngắt sẽbịcấm (tại CPU) - IF disabled: sau khi CPU

reset, trướcđóđã có IRQ khác, sau khi th/h lệnh CLI.

Non Maskable Interrupt, NMI là ngắt có mứcưu tiên cao

nhất, thường cho các việc: mấtđiện, sai sốliệu (DRAM

parity)... PC hiện nay, thường không dùng NMI.

3.2. Interrupt: 3.2.2. Phân loại: b. Hardware:

![Giáo trình Trang bị điện nước (TC) - Trường Cao đẳng Công nghiệp Thanh Hóa [Ngành Điện nước]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260511/hoatrami2026/135x160/14221778681890.jpg)