Giới thiệu tài liệu

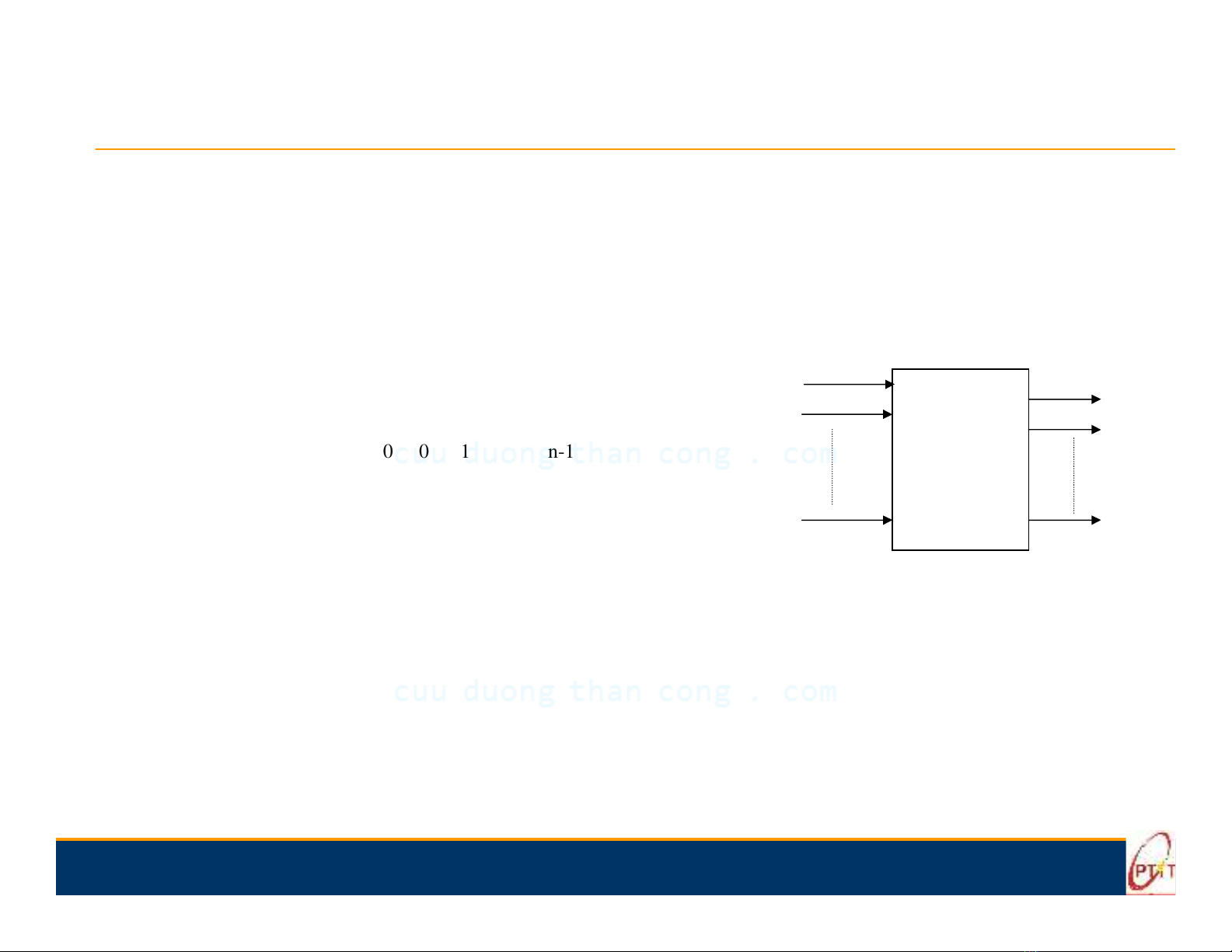

Tài liệu này giới thiệu về mạch logic tổ hợp, một khái niệm cơ bản trong điện tử số. Nó bao gồm các đặc điểm cơ bản và phương pháp biểu diễn chức năng logic của chúng, đặt nền tảng cho việc phân tích và thiết kế các hệ thống số.

Đối tượng sử dụng

Tài liệu này dành cho sinh viên và nhà nghiên cứu trong các lĩnh vực kỹ thuật điện, điện tử và khoa học máy tính, đặc biệt là những người đang nghiên cứu về điện tử số và thiết kế mạch.

Nội dung tóm tắt

Chương này cung cấp cái nhìn tổng quan toàn diện về mạch logic tổ hợp, bắt đầu với các đặc điểm cơ bản của chúng, như đầu ra chỉ phụ thuộc vào đầu vào hiện tại và cấu trúc từ các cổng logic. Tài liệu trình bày chi tiết các phương pháp khác nhau để biểu diễn chức năng logic, bao gồm đại số Boole, bảng trạng thái, bản đồ Karnaugh và biểu đồ thời gian. Sau đó, tài liệu đi sâu vào các phương pháp phân tích và thiết kế cho các mạch này, minh họa quy trình thiết kế bằng các ví dụ thực tế như công tắc đèn hai chiều. Các thành phần tổ hợp chính được giải thích cặn kẽ, bao gồm các loại mạch mã hóa (ví dụ: BCD, ưu tiên) và mạch giải mã (ví dụ: 7 đoạn, nhị phân). Hơn nữa, tài liệu đề cập đến các mạch xử lý dữ liệu như bộ hợp kênh và bộ phân kênh, nhấn mạnh vai trò của chúng như các khối xây dựng đa năng. Các mạch số học và so sánh thiết yếu, như mạch cộng toàn phần, mạch cộng nhị phân song song và các bộ so sánh khác nhau (bằng, lớn hơn), cũng được thảo luận. Cuối cùng, chương giới thiệu các cơ chế phát hiện lỗi như tạo và kiểm tra bit chẵn lẻ, và kết thúc bằng việc giải thích Đơn vị Số học và Logic (ALU), một thành phần cốt lõi của máy tính, trình bày chi tiết các chức năng logic và số học của nó.