Giới thiệu tài liệu

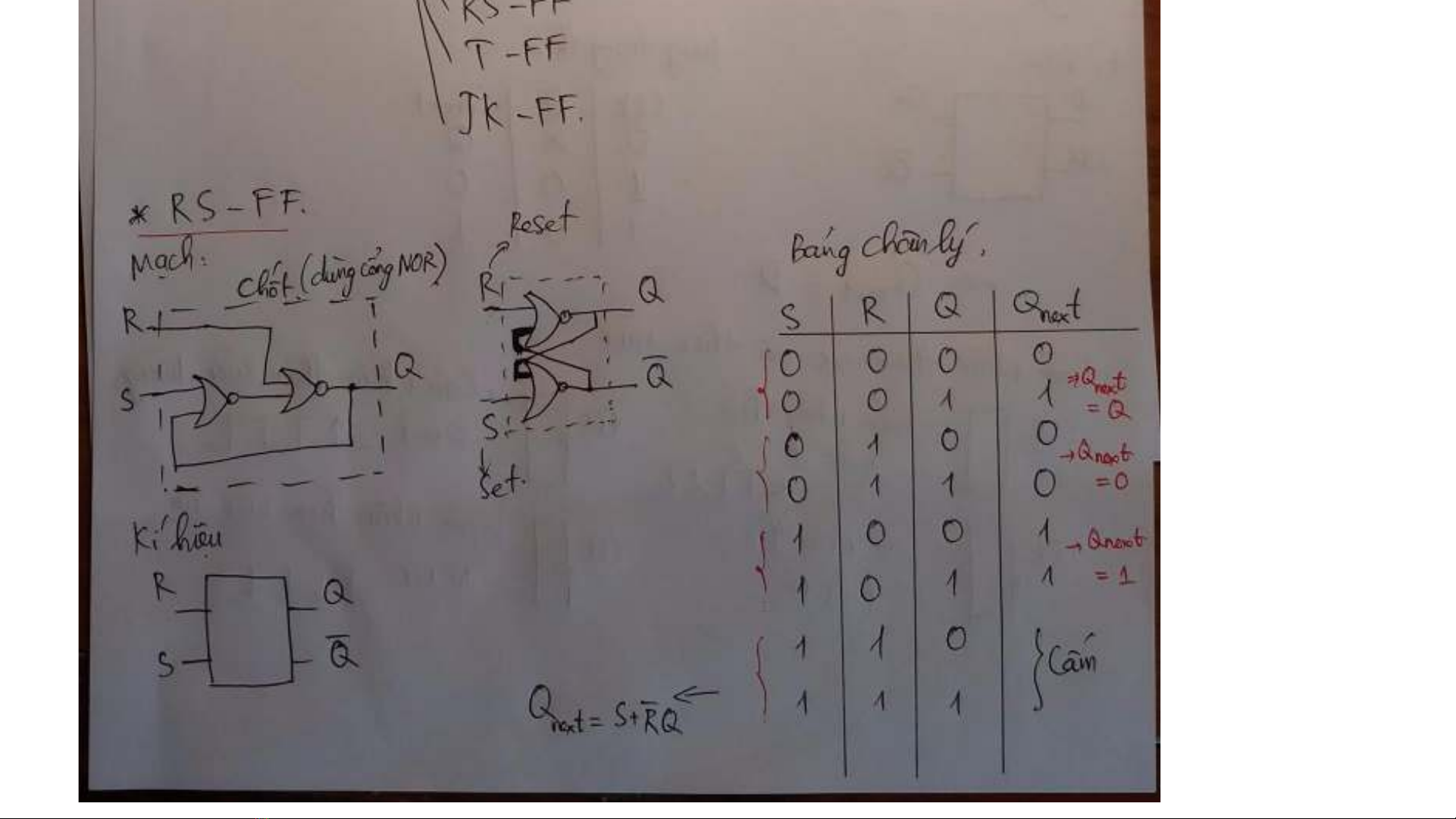

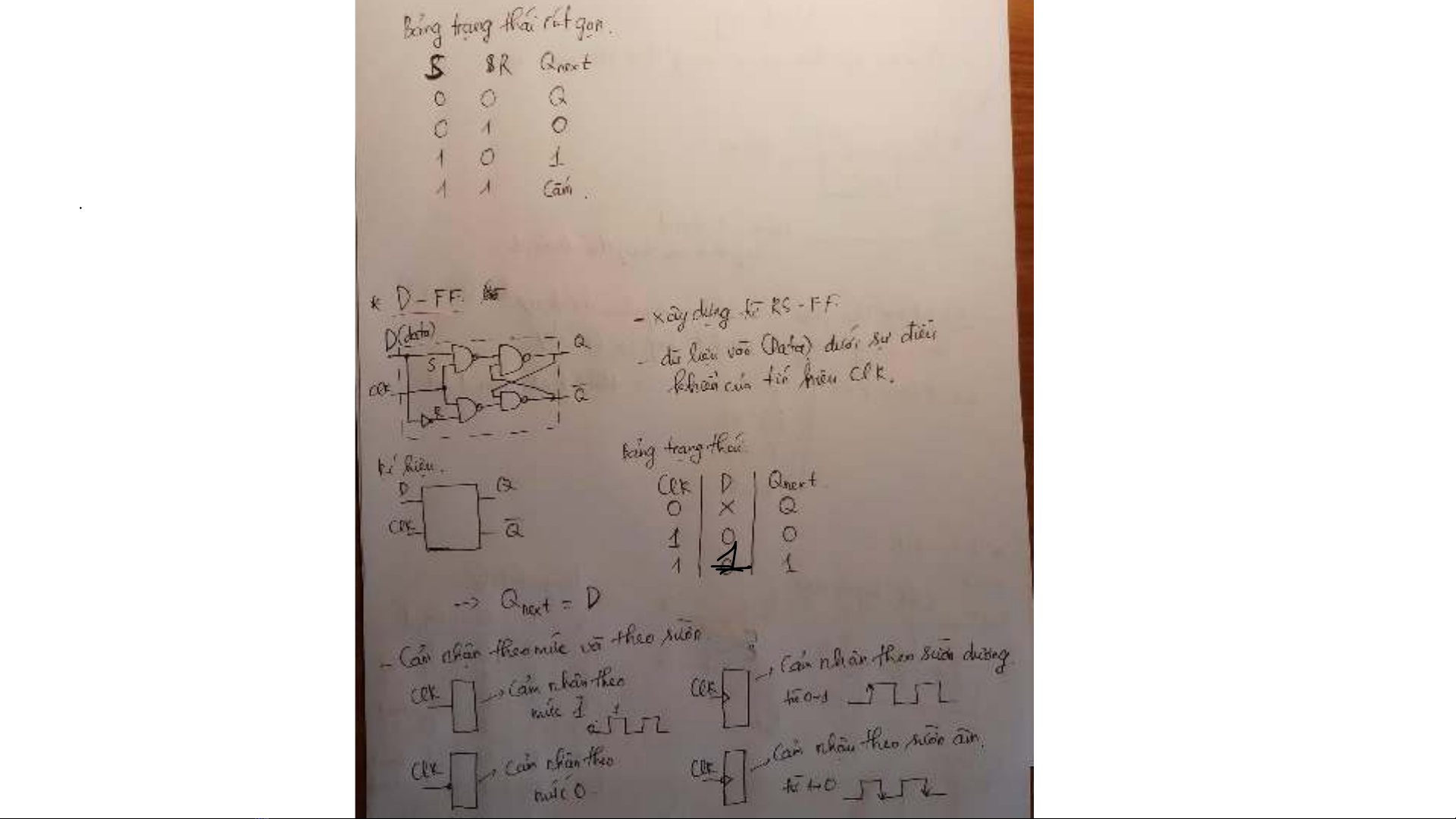

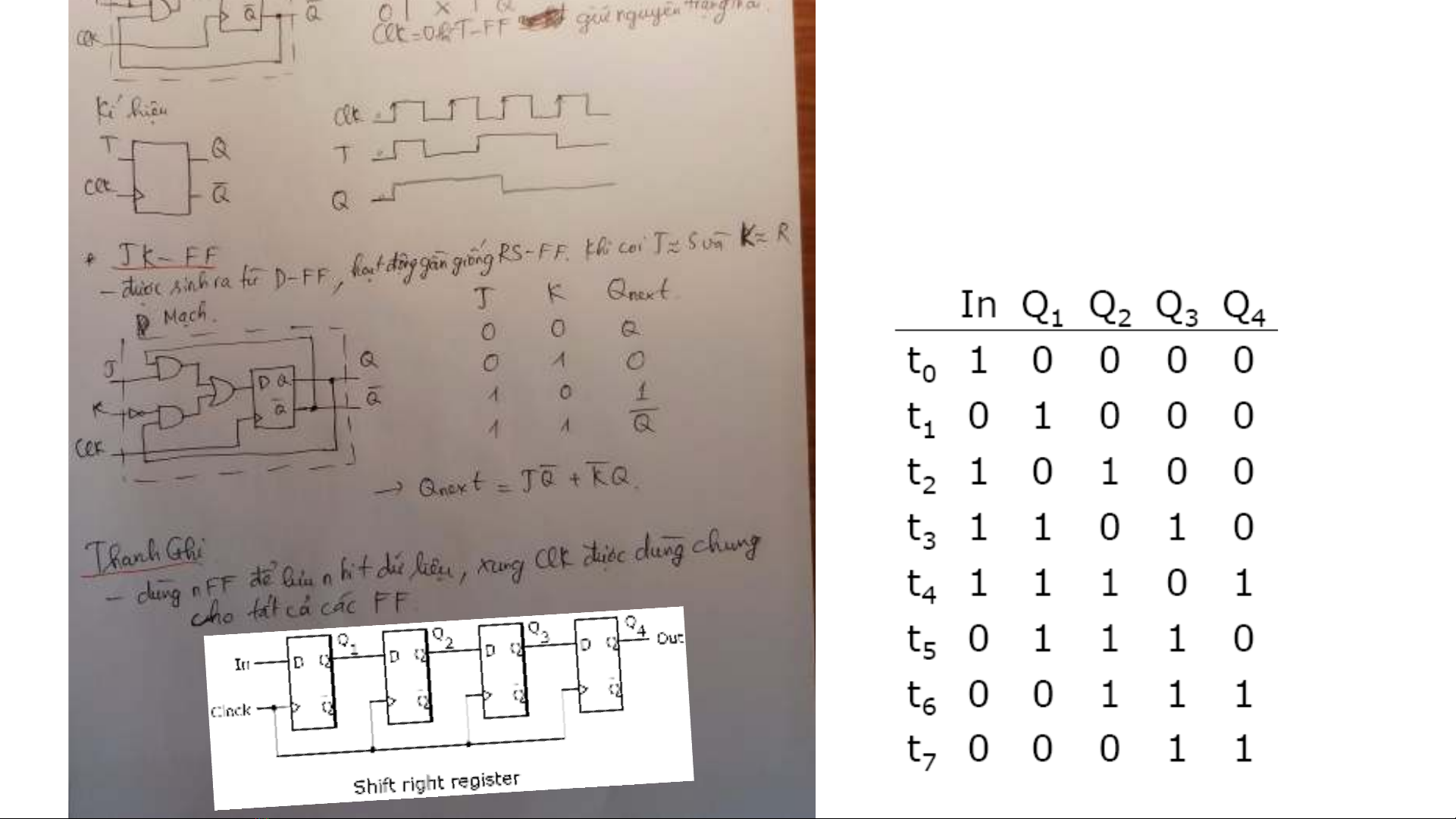

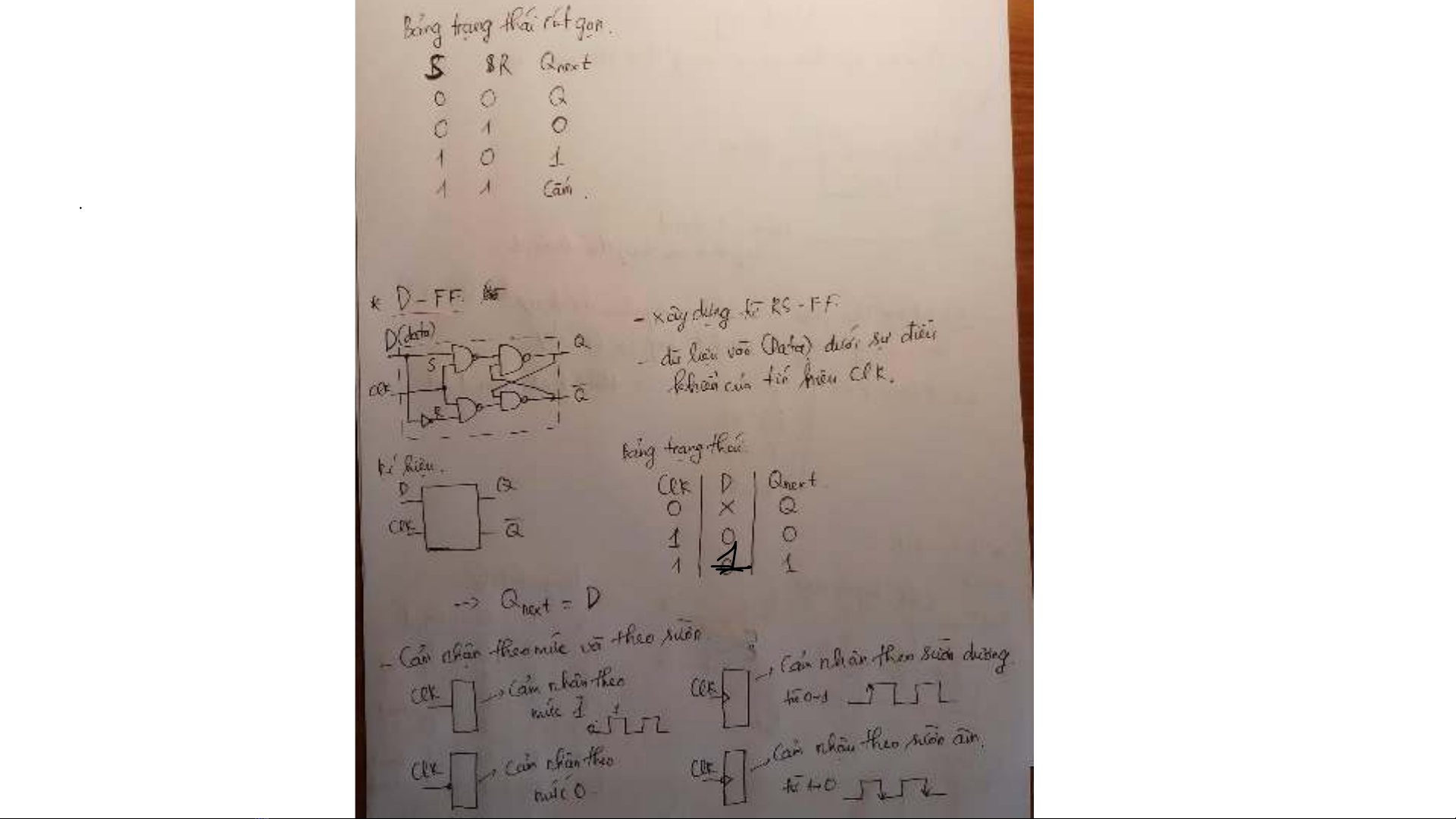

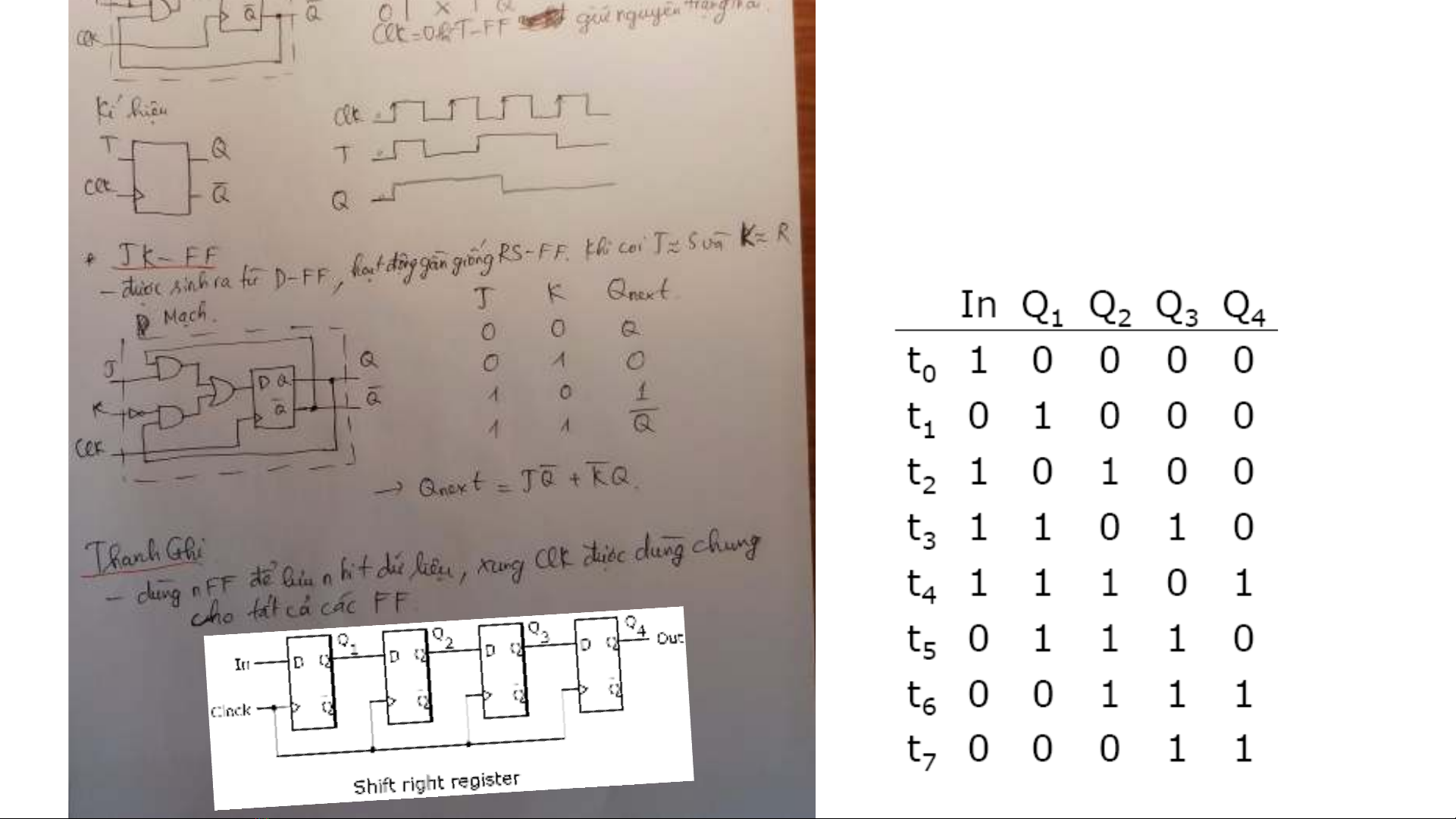

Tài liệu 'Điện tử số: Chương 7 và 8 - Duy Tuân' chứa nội dung về Flip-Flop, thanh ghi và bộ đếm; mạch tuần tự; các bước làm bài toán thiết kế mạch. Tài liệu này giúp học viên hiểu về các công thức, biểu đồ và sử dụng của chúng trong thiết kế mạch điện tử.

Đối tượng sử dụng

Sinh viên học chuyên môn Điện tử số và những người có quan tâm đến thiết kế mạch.

Nội dung tóm tắt

Tài liệu 'Điện tử số: Chương 7 và 8 - Duy Tuân' bao gồm các nội dung chi tiết về Flip-Flop, thanh ghi và bộ đếm. Nó cũng đề cập đến mạch tuần tự và cách làm bài toán thiết kế mạch điện tử. Tài liệu cung cấp công thức, biểu đồ, và ví dụ cho các công cụ và phương pháp áp dụng trong quá trình thiết kế mạch. Một số chủ đề quan trọng bao gồm cách sử dụng T-FF trong ứng dụng thực tế và cách tăng bộ đếm. Tài liệu này cho phép người đọc có thể hiểu về các khái niệm cơ bản trong điện tử số và cách áp dụng chúng trong quá trình thiết kế mạch.