Các thông số của Op amp

Nguyn Quốc Cng – 3I

Giới thiệu

Giới thiệu

Điện áp lệch không đầu vào

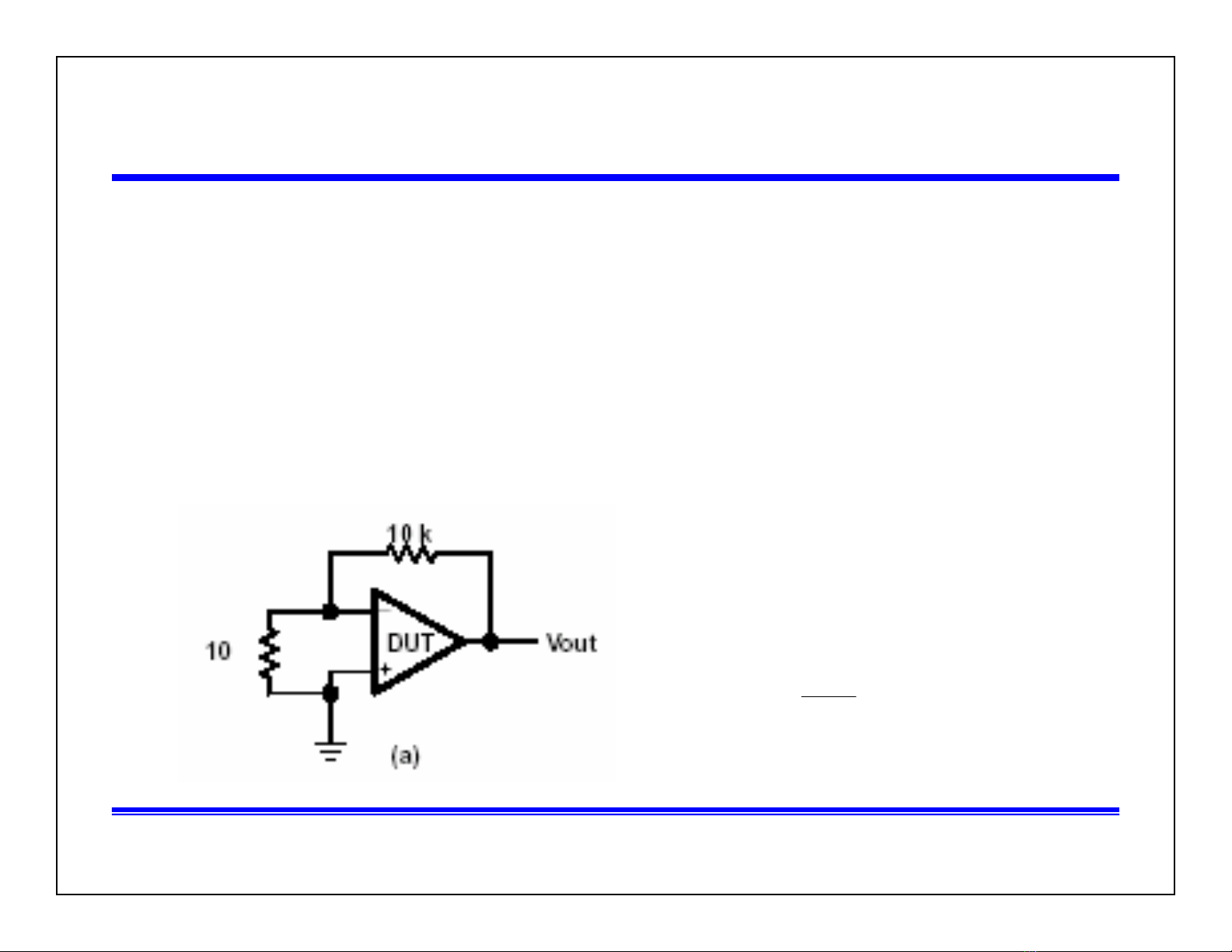

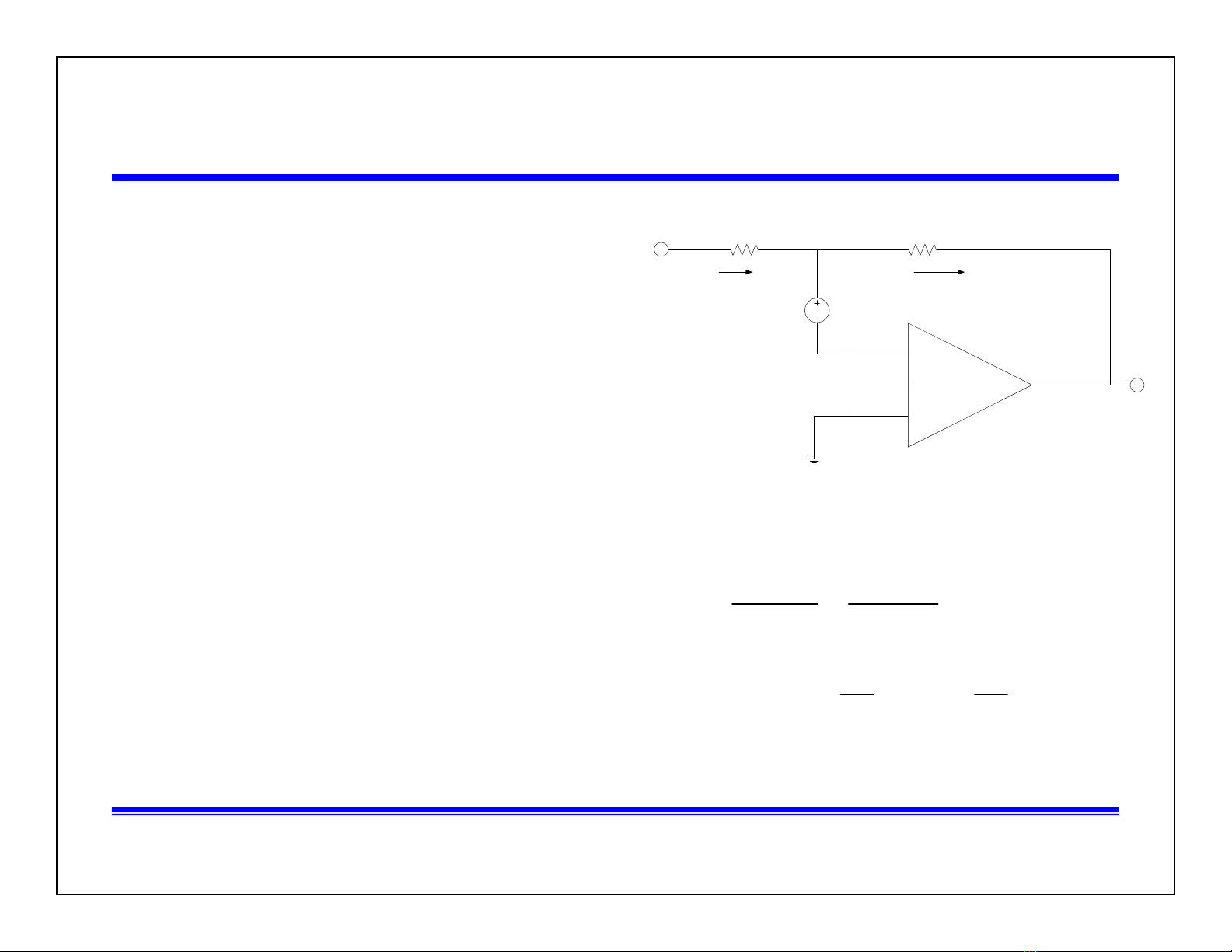

• Điện áp lệch không (input offset voltage): do sự không cân bằng

của các mạch điện tử trong op amp, khi điện áp đầu vào bằng

không thì điện áp đầu ra khác không.

• Điện áp offset là điện áp cần đặt vào đầu vào để cho đầu ra bằng 0.

Ký hiệu V

IO

.

• Thng các op amp đầu vào bipolar có các thông số điện áp offset

đầu vào tốt hơn các op amp đầu vào JFET hoặc CMOS

a

e

Ảnh hởng của VIO

ea a

!

"

#$%

"&

#

#

$& $