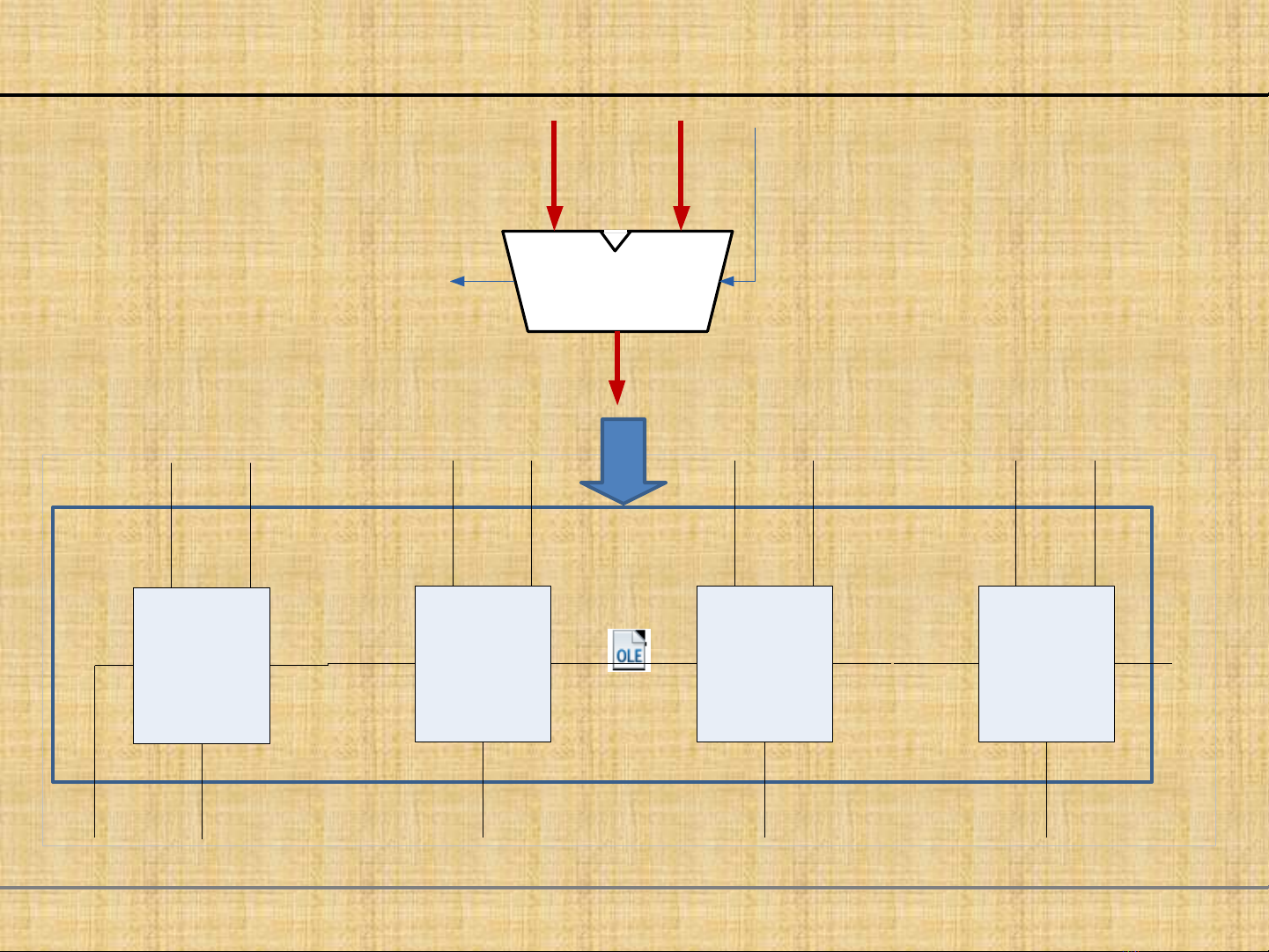

ADDER4 = 4 Full_adder

Behavioral

Dataflow

configuration behav of adder4 is

for structure -- one of architecture

for all: full_adder

use entity work.full_adder(behavioral);

end for;

end for;

end configuration;

-- select architecture

for u0: full_adder use entity work.full_adder(behavioral);

for u1: full_adder use entity work.full_adder(behavioral);

for u2: full_adder use entity work.full_adder(dataflow);

for u3: full_adder use entity work.full_adder(dataflow);

?

5/15

Chương II: Ngôn ngữ VHDL quangkien82@gmail.com

Configuration