CHÖÔNG 1

CAÙC THIEÁT BÒ LOGIC LAÄP TRÌNH ÑÖÔÏC

(Programmable Logic Device)

Boä nhôù baùn daãn

Boä nhôù baûng Boä nhôù haøm

RAM ROM PLD

tónh ñoäng MROM PLA PAL LCA EPLD PEEL GAL

PROM PPLA

EPROM EPLPAL

EEPROM EEPPAL

RAM= Random Access Memory (boä nhôù truy caäp ngaãu nhieân)

ROM= Read Only Memory

M= Mask Programmed (ñöôïc laäp trình baèng che maët naï)

P = Programmable (laäp trình ñöôïc, khaû laäp trình)

EP = Erasable and Programmable

EEP = Electrically Erasable and Programmable (xoùa vaø laäp trình baèng ñieän)

PLD = Programmable Logic Device

PLA = Programmable Logic Array (maûng logic laäp trình ñöôïc)

PAL = Programmable Array Logic (logic maûng laäp trình ñöôïc)

LCA = Logic Cell Array (Maûng teá baøo logic)

ROM (Read-Only Memory)

1. GIÔÙI THIEÄU:

ROM laø moät maïch toå hôïp coù m ngoõ vaøo vaø n ngoõ ra (hình 1.2). Caùc ngoõ

vaøo ñöôïc goïi laø caùc ngoõ vaøo ñòa chæ (address inputs) vaø thöôøng ñöôïc ñaët teân laø

A0, A1 ,..., Am-1. Caùc ngoõ ra ñöôïc goïi laø caùc ngoõ ra döõ lieäu (data outputs) vaø

thöôøng ñöôïc ñaët teân laø D0, D1 ,..., Dn-1.

address data

inputs outputs

(m ñöôøng) (n ñöôøng)

Hình 1.2 Caáu truùc cô baûn cuûa ROM 2m x n

Kích thöôùc cuûa ROM laø 2m x n (bit)

Noäi dung cuûa ROM chöùa baûng chaân trò cuûa moät haøm logic toå hôïp n ngoõ

vaøo, m ngoõ ra: coù m+n coät vaø 2m haøng. Boû qua caùc trì hoaõn thôøi gian, caùc ngoõ

ra döõ lieäu cuûa ROM ôû moïi luùc laø caùc bit ra cuûa haøng trong baûng chaân trò ñöôïc

choïn bôûi caùc ngoõ vaøo ñòa chæ.

Ví duï: Baûng chaân trò cho haøm toå hôïp coù 3 ngoõ vaøo vaø 4 ngoõ ra

Inputs Outputs

A2 A1 A0 D3 D2 D1 D0

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

1 1 1 0

1 1 0 1

1 0 1 1

0 1 1 1

0 0 0 1

0 0 1 0

0 1 0 0

1 0 0 0

Baûng 1.1 Baûng chaân trò cuûa haøm logic toå hôïp 3 ngoõ vaøo, 4 ngoõ ra

2m x n ROM

A0 D

0

A1 D

1

A2 D

2

. .

. .

Am-2 Dn-2

Am-1 Dn-1

2. DUØNG ROM THÖÏC HIEÄN HAØM LOGIC:

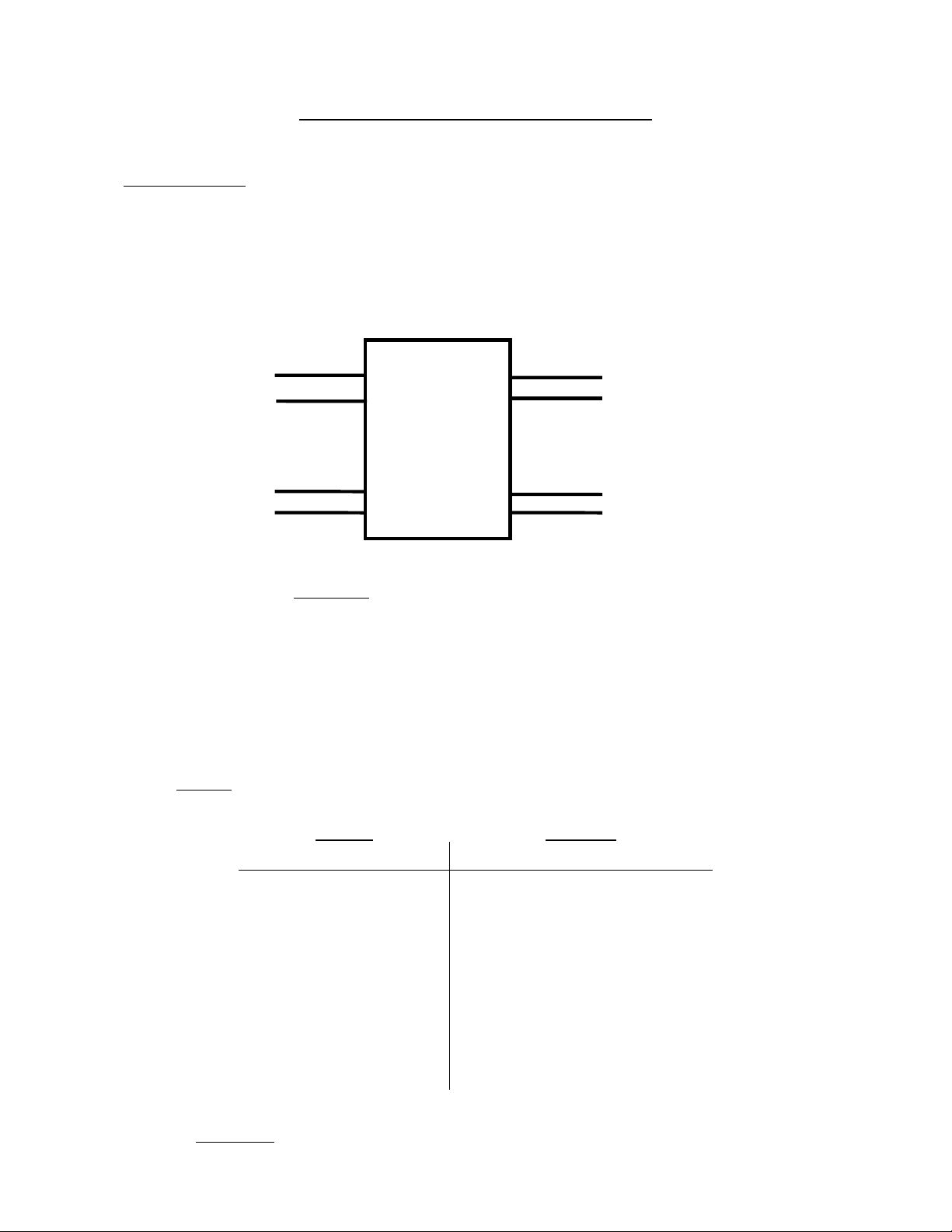

Baûng 1.1 laø baûng chaân trò cuûa boä giaûi maõ 2 sang 4 vôùi ñieàu khieån cöïc tính

ngoõ ra, haøm naøy coù theå xaây döïng baèng caùc coång nhö ôû hình 1.3.

Hình 1.3 Boä giaûi maõ 2 sang 4 vôùi ñieàu khieån cöïc tính giaù trò ra

Nhö vaäy ta coù 2 caùch ñeå xaây döïng boä giaûi maõ : vôùi caùc coång rôøi, hoaëc vôùi

ROM 8x4 maø chöùa baûng chaân trò nhö ôû hình 1.4.

Hình 1.4 Keát noái ñeå xaây döïng boä giaûi maõ 2 sang 4 duøng ROM 8x4

Chuù yù:

• Vaán ñeà hoaùn vò caùc coät bit trong baûng chaân trò cuûa haøm caàn ghi ROM.

• Khi duøng ROM ñeå chöùa moät baûng chaân trò cho tröôùc, caùc tín hieäu xuaát

vaø nhaäp ñoïc töø phaûi sang traùi trong baûng chaân trò thöôøng ñöôïc gaùn vaøo

caùc ngoõ vaøo ñòa chæ vaø ngoõ ra döõ lieäu cuûa ROM vôùi caùc nhoùm theo thöù töï

taêng daàn.

• Khi thieát keá duøng ROM ta caàn xaùc ñònh kích thöôùc vaø baûng chaân trò cuûa

ROM

Y0

Y1

Y2

Y3

I0

I1

POL

8x4 ROM

A0 D0

A1 D1

A2 D2

D3

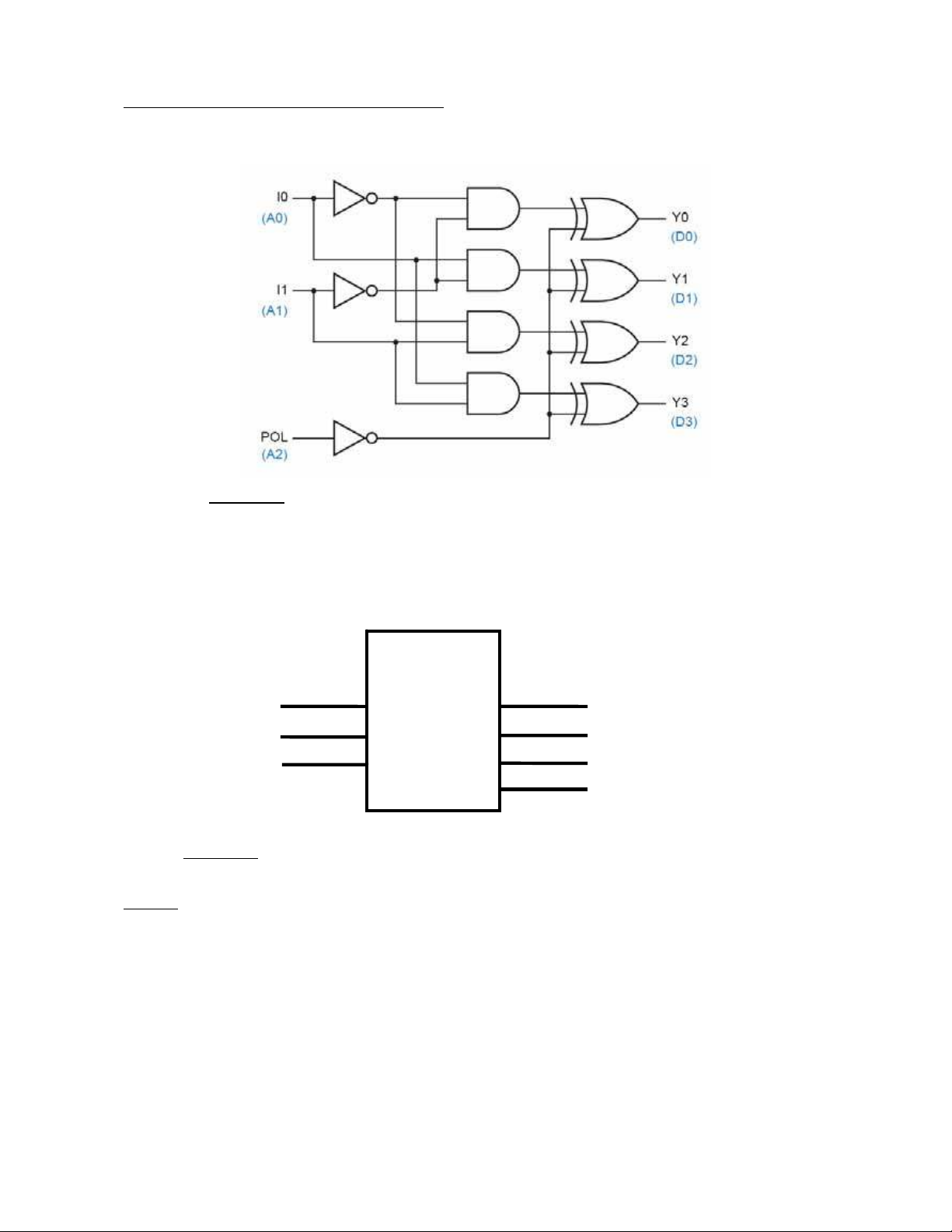

Thí duï :

Duøng ROM ñeå thöïc hieän haøm nhaân nhò phaân khoâng daáu cho 2 soá 4 bit

vôùi nhau.

Söû duïng ROM 2

8x 8 (256 x 8) vôùi keát noái nhö ôû hình 1.5.

Hình 1.5 Keát noái thöïc hieän nhaân nhò phaân khoâng daáu duøng ROM 256x8

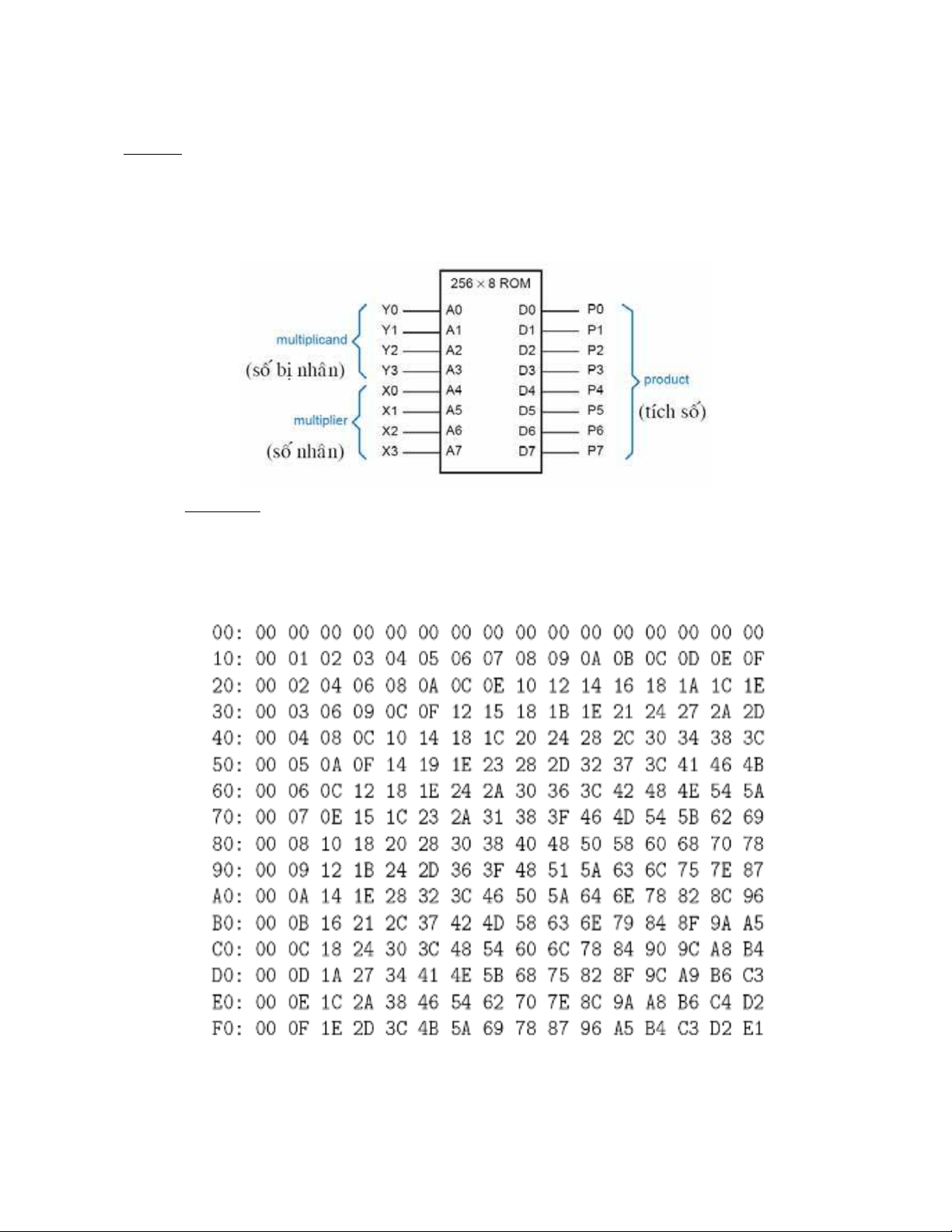

Noäi dung ghi cho ROM (daïng file vaên baûn hex) nhö sau:

Ñòa chæ: Tích soá cuûa 1x2

3. CAÁU TRUÙC NOÄI CUÛA ROM:

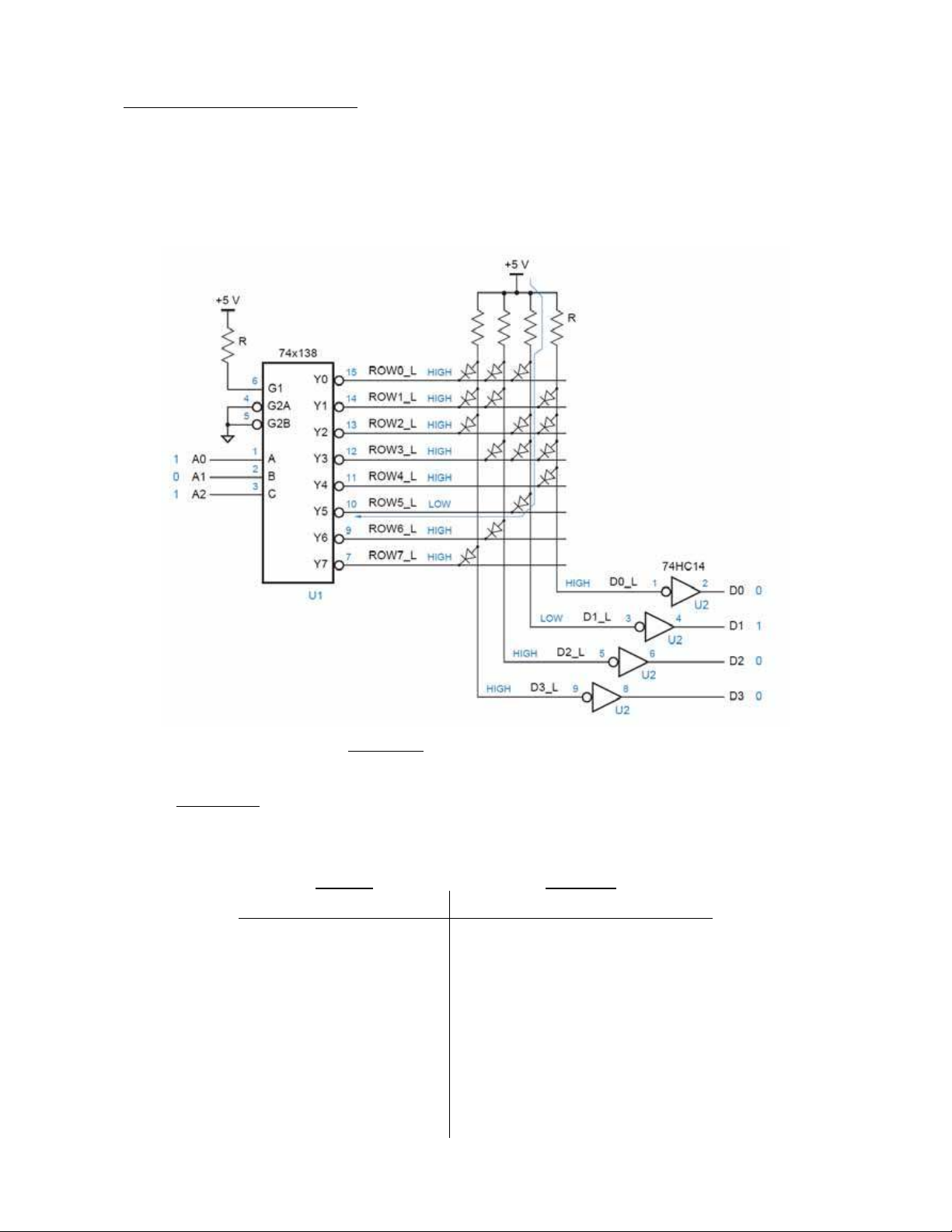

Hình 1.6 laø 1 sô ñoà ROM 8 x 4 töï taïo duøng boä giaûi maõ TTL vaø caùc diode.

Moãi ñöôøng ra boä giaûi maõ ñöôïc goïi laø ñöôøng töø (word line) bôûi vì noù choïn

moät haøng hoaëc moät töø cuûa baûng chöùa trong ROM.

Moãi ñöôøng thaúng ñöùng ñöôïc goïi laø ñöôøng bit (bit line) bôûi vì noù töông

öùng vôùi 1 bit ra cuûa ROM.

Hình 1.6 ROM 8 x 4 ñôn giaûn

Nhaän xeùt: Coù diode thì töông öùng ngoõ ra ôû → möùc 0; coøn khoâng coù diode

thì ngoõ ra töông öùng ôû möùc 1.

Inputs Outputs

A2 A1 A0 D3 D2 D1 D0

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

1 1 1 0

1 1 0 1

1 0 1 1

0 1 1 1

0 0 0 1

0 0 1 0

0 1 0 0

1 0 0 0