Đề cương Vi Xử Lý

1. Đặc điểm cấu trúc của BVXL(công suất, độ dài từ, khả năng đánh địa chỉ, tốc độ). Cho Bộ VXL có tần số làm việc 750Mhz, theo

kiến trúc NeuManm, bên trong được thiết kế 4 ALU và để thực hiện 1 lệnh VXL cần 5 vi lệnh với hệ số thời gian truy cập bộ nhớ là

100 ns. Xác định tốc độ thực hiện lệnh của bộ VXL.

Trả lời:

1.1 Những đặc điểm cấu trúc của bộ VXL:

+ Công suất của bộ VXL: là khả năng xử lý dữ liệu

Đ.điểm:

• Độ dài từ của bộ VXL(data word length), tính bằng số byte.

• Dung lượng nhớ VL có thể đánh địa chỉ (addressing capacity).

• Tốc độ xử lý lệnh của Bộ VXL (instruction execute speed)

* Công suất máy tính (tốc độ x.lý thông tin, khả năng lưu trữ thông tin, khả năng kết nối nhiều loại thiết bị ngoại vi, …) phụ thuộc vào công

suất của bộ VXL trong CPU.

* Độ dài từ:

Mỗi bộ VXL có thể xử lý dữ liệu với độ dài từ cố định. Phụ thuộc vào từng thế hệ VXL và mức độ phát triển của công nghệ VXL, độ dài từ có

thế là 4 bit, 8 bit, 16 bit, 32 bit, 64 bit. Tập lệnh của bộ VXL thường có các lệnh thực hiện theo từ và theo byte. Nếu 1 từ là 2 byte thì cũng phân

biệt byte cao và byte thấp. Byte thấp chiếm các bit từ 0 đến 7, Byte cao chiếm các bit từ 8 đến 15. Độ rộng từ có độ dài bao nhiêu bit thì cũng

có bấy nhiêu bit đối với các thanh ghi, ALU và bus dữ liệu bên trong bộ VXL. Bus dữ liệu bên ngoài cũng thường có chừng đó độ dài nhưng

cũng có thể chỉ 1 byte trong khi độ dài xử lý bên trong của bộ VXL là 6 bit. Độ dài từ càng lớn càng tạo ra nhiều khả năng tính toán của bộ

VXL, khoảng biểu diễn số rộng hơn, tốc độ tính toán nhanh hơn.

* Khả năng đánh địa chỉ:

Các từ dữ liệu và lệnh máy cắt trong BN tại các ngăn nhớ khác nhau. Mỗi ngăn nhớ phải có địa chỉ nhận biết. Dải đánh địa chỉ càng lớn thì

dung lượng BN càng nhiều. Để đánh địa chỉ, bộ VXL thường có thanh ghi địa chỉ. Độ rộng của thanh ghi địa chỉ quyết định giải địa chỉ của

vùng nhớ vật lý mà bộ VXL thỏa mãn. VD: độ rộng của thanh ghi là 6 bit có thể đánh được địa chỉ khoảng nhớ vật lý là 2

16

= 2

6

. 2

10

= 64 KB

= 65536 từ 8 bit.

Với số mũ ở hệ cơ số 2 ta có thể đánh giá ngay được độ rộng của thanh ghi địa chỉ hay bus địa chỉ. VD: để đánh được địa chỉ đến 32Gb, cần

phải có 35 đường dây địa chỉ (A0-A34). Khả năng đánh địa chỉ càng lớn thì càng cho phép tạo ra 1 hệ thống máy tính có cấu hình mạnh với

nhiều loại thiết bị ngoại vi, bộ nhớ chính có dung lượng lớn (đến vài trăm MB) và khả năng xử lý nhanh.

* Tốc độ thực hiện lệnh:

Tốc độ thực hiện lệnh của bộ VXL có thể đo bằng tốc độ thực hiện các lệnh dấu phẩy động FLOPS hoặc tính bằng triệu lệnh/giây (MIPS).

Công thức tính MIPS theo kiến trúc NeuMan là: MIPS = (f*N)/(M+T)

Trong đó:

f : tần số làm việc của Bộ VXL

N: số lượng các đơn vị xử lý số học và logic (ALU) không phụ thuộc vào nhau bên trong bộ VXL

M: số lượng vi lệnh trung bình của 1 lệnh trong bộ VXL

T : hệ số tg truy cập BN (chu trình chờ đợi trong khi truy cập BN)

Theo CT này, tốc độ thực hiện lệnh của bộ VXL có thể thay đổi nhờ 4 yếu tố. Để nâng cao tốc độ VXL kiên trúc song song , đường ống, đồng

xử lý, BN dự trữ. Và bus rộng đã được áp dụng cho cac chip VXL công nghệ cao hiện nay.

MIPS phụ thuộc vào tần số nhịp đồng hồ của bộ VXL. Tần số nhịp càng lớn thì tốc độ thực hiện lệnh càng cao. Các bộ VXL khi s/x thường có

kí hiệu chữ cái hay số cụ thể để phân biệt tần số nhịp đồng hồ. Tần số nhịp đồng hồ của bộ VXL phụ thuộc vào công nghệ chế tạo bộ VXL.

Phần lớn các bộ VXL được chế tạo theo 2 công nghệ bán dẫn: NMOS và CMOS

1.2 Tốc độ thực hiện lệnh của bộ VXL:

f = 750MHz

N=4

M=5

T=100

MIPS=(f*N)/(M+T)=(750*4)/(5+100)=...

Câu 2: Hãy nêu các đặc tính nâng cao tốc độ của bộ VXL là gì? Định nghĩa kiến trúc siêu hướng? Khuôn dạng dữ liệu?

Trả lời :

* Những đặc tính nâng cao tốc độ của bộ VXL:

1. Xử lý song song và kiến trúc siêu hướng

2. Đồng xử lý

3. Kĩ thuật nhớ dự trữ

4. Kĩ thuật đường ống

5. Bus rộng

+ Xử lý song song : là 2 quá trình, tính toán cùng xảy ra đồng thời. Trong kiến trúc máy tính, sự kết hợp 2 bộ VXL trong khối xử lý trung tâm

(CPU) tạo ra khả năng xử lý song song trong cùng 1 tg.

Kiến trúc này có thể tạo ra tốc độ xử lý dữ liệu lên gấp đôi so với kiến trúc chỉ dùng 1 bộ VXL. Cũng có thể thực hiện song song ngay bên

trong cấu trúc của bộ VXL, bằng cách thiết kế sao cho quá trình xử lý D.liệu bên trong chip VXL chia thành các phiên khác nhau và thực hiện

song song nhờ sự phân chia khối logic điều khiển(CU) bên trong thành phần riêng.

+ Đồng xử lý : là bộ VXL riêng biệt kết nối với bộ VXL thông qua bus hệ thống. Bộ đồng xử lý chỉ thực hiện 1 số chức năng đặc biệt, ví dụ

như các phép toán đòi hỏi sự chính xác sử dụng dấu phẩy động. Tốc độ xử lý của bộ đồng xử lý những phép tính này sẽ nhanh hơn rất nhiều so

với bộ xử lý chính. Các bộ VXL công nghệ cao hiện nay đã cấy vào bên trong khối xử lý dấu phẩy động FPU càng làm tăng tốc độ tính toán

các phép tính nhanh và chính xác hơn nhiều.

+ Bộ nhớ lưu trữ (cache memory): BN cache là BN có tốc độ cao, nó có thể nằm ngay bên trong bộ VXL với dung lượng hạn chế hoặc nằm kế

ngay bên cạnh bộ VXL và kết nối trực tiếp với chip xử lý với dung lượng đủ lớn, trong khi đó BN chính kết nối với bộ VXL thông qua bus hệ

thống. Sự trao đổi dữ liệu giữa BN chính và bộ VXL bị hạn chế về tốc độ, vì vậy để tăng tốc độ xử lý, phải tổ chức làm sao khi thực hiện

chương trình, bộ VXL trước hết tìm kiếm lệnh ở BN dự trữ trước, nếu không có lệnh chứa trong BN dự trữ thì mới phải tìm tới BN chính. Điều

này có nghĩa là nếu đa số lệnh không có trong BN dự trữ thì tốc độ xử lý chậm hơn gấp đôi so với truy cập thẳng vào BN chính. Vì vậy phải tổ

chức làm sao đa số các lệnh của chương trình nằm hẳn trong BN dự trữ, ví dụ các lệnh có tần suất xuất hiện trong chương trình cao thì có thể

cất trong BN dự trữ. Dung lượng BN dự trữ phải đủ lớn để đảm bảo lưu trữ những chương trình ứng dụng lớn. Ngày nay, dung lượng BN dự

trữ bên trong các chip VXL chưa cao (32Kb :16Kb Dcache, 16Kb Icache). Với BN dự trữ bên ngoài có thể đạt tới dung lượng 2-4 MB.

+ Ký thuật đường ống : Mô phỏng dây chuyền lắp ráp máy móc, hệ thống đường dẫn, trong 1 số VXL hiện nay có chức năng thực hiện các

lệnh máy liên tục thành 1 dây chuyền với 5 công đoạn : nhập D.Liệu của lệnh từ BN, giải mã lệnh, thực hiện các lệnh, ghi kết quả thực hiện

lệnh vào BN. Khi lệnh thứ 1 bắt đầu bước vào thực hiện, ở giai đoạn 2 thì mã lệnh của lệnh tiếp theo được đọc từ BN ra để thực hiện bước 1

(giải mã lệnh). Cứ như vậy, các lệnh được thực hiện theo 1 dây chuyền liên tục như là dòng nước đi trong đường ống. Tốc độ xử lệnh vì thế

được tăng lên rất cao.

+ Bus rộng : Kĩ thuật bus rộng áp dụng cho cả bên trong lẫn bên ngoài bộ VXL. Bên trong bộ VXL, thanh ghi tổng (A) có độ dài gấp đôi bus,

như vậy tốc độ tính toán sẽ nhanh hơn, bởi không phải thực hiện các phép truy cập với BN để lưu trữ các kết quả trug gian của các phép tính.

* Kiến trúc siêu hướng :

Kiến trúc của bộ VXL có các khối chức năng xử lý song song bên trong gọi là kiến trúc siêu hướng, nghĩa là cùng 1 lúc nhiều hướng xử lý khác

nhau bên trong VXL. Kiến trúc siêu hướng là sự phát triển tiếp theo của kiến trúc RISC, nó không những nâng cao tốc độ xử lý mà còn nâng

cao độ tin cậy của CPU, bởi vì khi có sự cố ở 1 chip VXL thì chip VXL còn lại vẫn đảm nhiệm chức năng được bình thường.

* Khuôn dạng d.liệu :

Khuôn dạng d.liệu của các loại VXL được phân biệt theo các số có dấu, không dấu, các kí tự mã ASCII, mã BCD (hệ 2 - 10) :

- không dấu và có dấu :

B – Byte (8 byte), H – nửa từ (16 bit), W từ (32 bit), D – từ kép (64 bit) (sự phân loại này cho các bộ VXL 32 bit)

Bit dấu là bit cao nhất (MSB)

- các kí tự mã ASCII : mỗi kí tự được mã hóa bằng 8 bit.

- Dữ liệu ở mã BCD : dữ liệu được biểu diễn bằng các nhóm số 4 bit. Mỗi nhóm số 4 bit có giá trị không vượt quá 10 (1010). Phân biệt dữ liệu

ở mã BCD đóng gói và không đóng gói. Trong BCD đóng gói, tất cả 64 bit được chia ra 8 nhóm (8 digit) và cả 8 digit được dùng để mã hóa.

Hai BCD digit trong 1 byte. Trong BCD không đóng gói, chỉ dùng 4 bit thấp trong từng byte để làm digit mã BCD, 4 bit cao của từng byte

không dùng tới và đều ghi giá trị 0.

Các dấu phẩy động phân ra số chính xác đơn 32 bit và chính xác kép 64 bit theo chuẩn IEEE 754-1985. Cũng có thể mở rộng độ chính xác đến

80 bit ở 1 số bộ VXl. Số dấu phẩy động có bit lớn nhất (MSB) dùng làm dấu, dấu = 0, đó là số dương. Dấu = 1 là dấu âm.

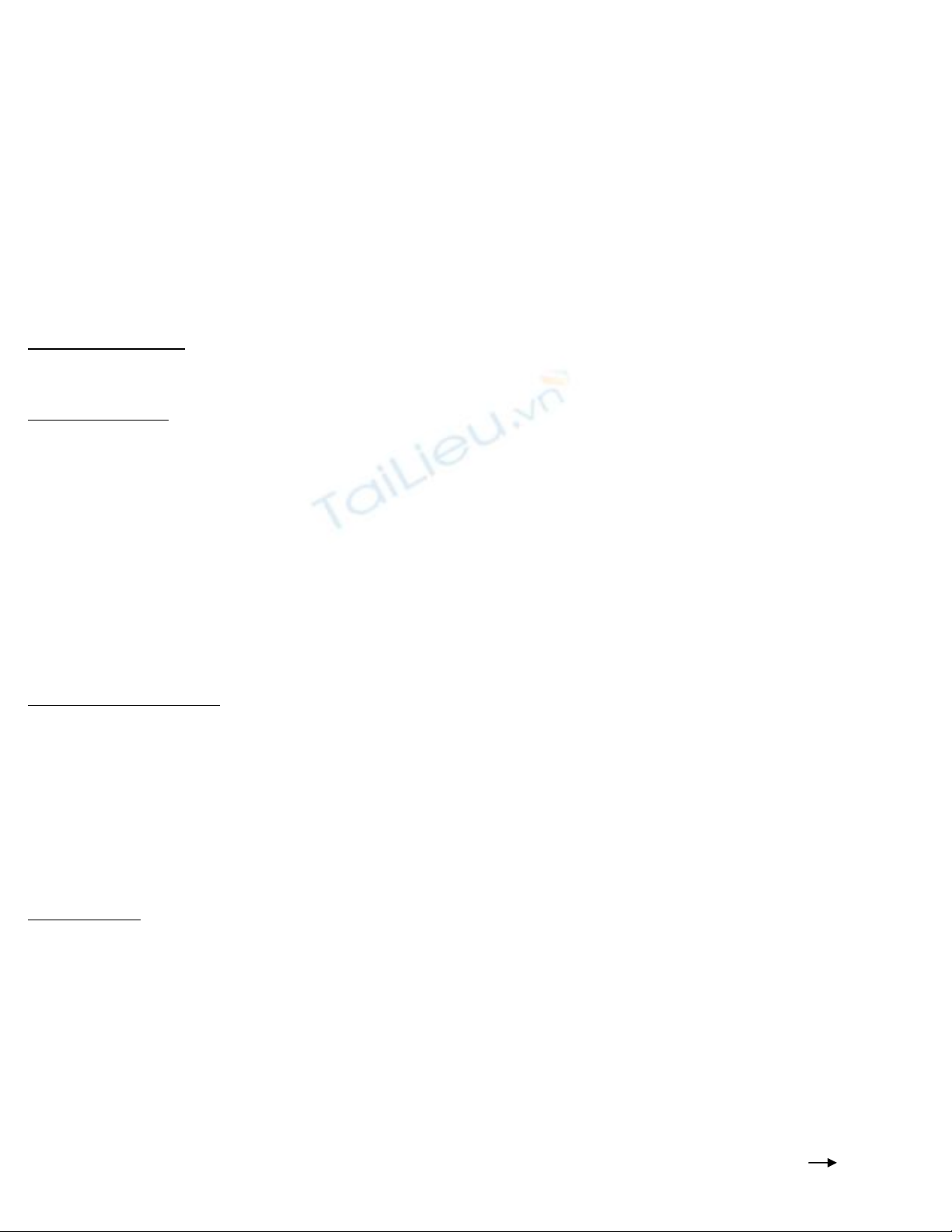

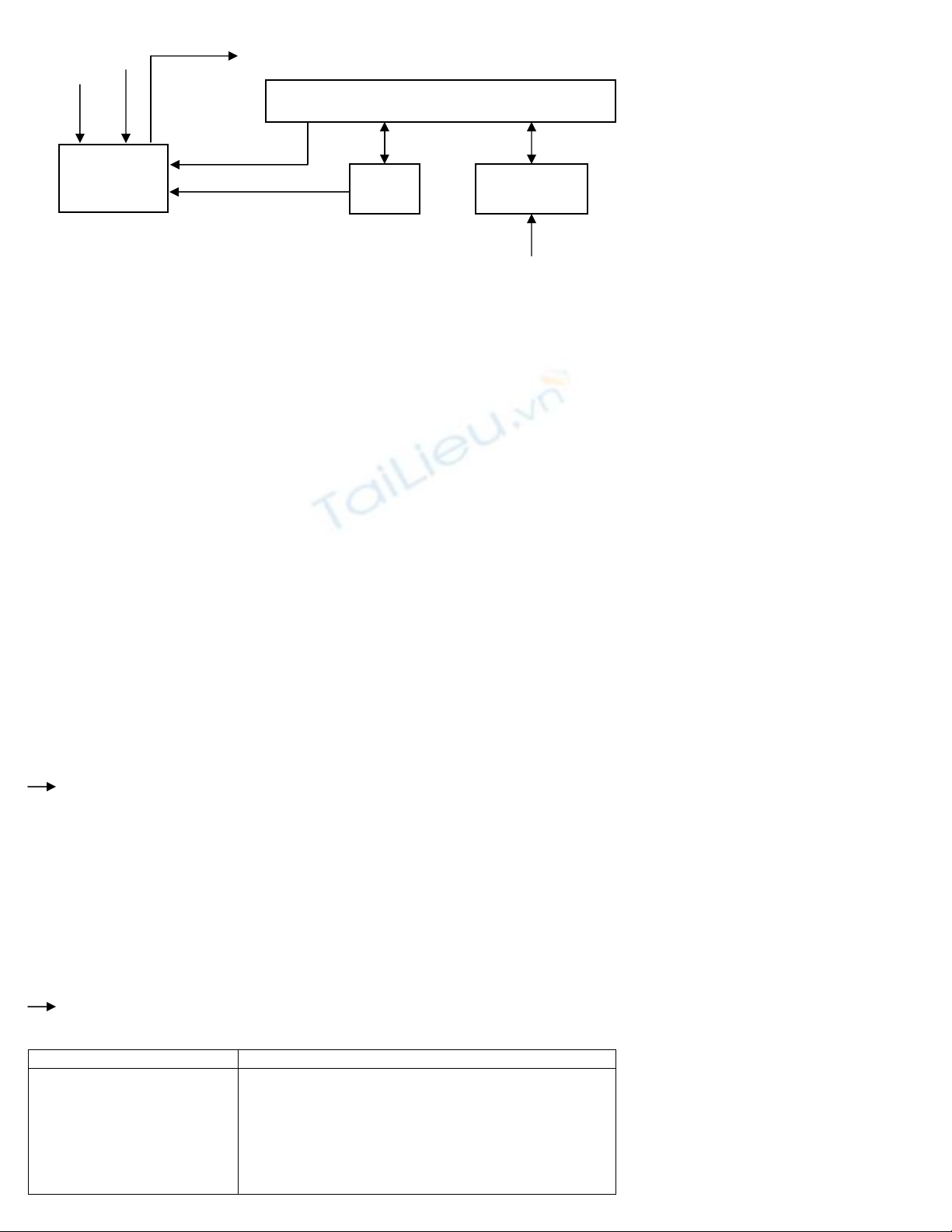

Câu 3 : 1. Sơ đồ cấu trúc bên trong của BVXL 8, 16 bit.

< hình vẽ >

2. Giải thích chức năng từng bộ phận (ALU, các thanh ghi, CU):

a. Đơn vị số học – logic (ALU)

- chứa khối logic thực hiện xử lý d.liệu

- Thực hiện các phép tính số học và logic : and, sub, mul, div, and, or, not,...

Shift left, Shift right, decr, incr,…

- Có hai cổng vào (in) để nhận d.liệu vào ALU và cổng ra (out) để lấy kết quả xử lý d.liệu của ALU ra ngoài.

- các thanh ghi temp1 và temp2 làm nhiệm vụ nhận d.liệu từ các nơi khác nhau bên trong BVXL thông qua bus d.liệu bên trong và lưu trữ trung

gian dữ liệu trong quá trình xử lý d.liệu trong ALU.

Tương tự, cổng ra kết nối với bus d.liệu bên trong do đó kết quả phép toán có thế đc ra tới các nơi khác nhau, d.liệu thường được đưa tới nơi bộ

cộng.

- các lệnh máy đc ALU xử lý có thể là 1 hay 2 toán hạng.

- Lệnh máy đc đọc từ BN vào BVXL đc giải mã nhờ bộ giải mã lệnh để tạo ra chuỗi các tín hiệu đi tới ALU đ.khiển quá trình x.lý d.liệu trong

ALU.

b. Các thanh ghi : đc chia thành nhóm theo mục đích s.dụng

- Nhóm thanh ghi dùng chung:

+ Thanh ghi A (bộ cộng), B, C, D, E, H, L : 8 bit

+ để xử lý 16 bit, có các lệnh thực hiện với các cặp thanh ghi BC, CE, HL

- Các thanh ghi khác : thanh ghi trạng thái (SR), con trỏ ngăn xếp (SP), thanh đếm lệnh (PC), thanh ghi lệnh (instruction register),…

* Thanh ghi tổng A (accumulator):

- tham gia phần lớn các phép tinh

- độ dài của thanh tổng có thể tính bằng độ dài từ hoặc gấp đôi độ dài từ của BVXL.

- những lệnh I/O với ngoại vi là nhóm lệnh trao đổi byte d.liệu giữa thanh ghi tổng A với các thanh ghi của điều khiển ngoại vi.

- Lệnh nhập d.liệu IN PORT là lệnh đọc d.liệu từ cổng của ngoại vi vào thanh ghi A và OUT PORT là đọc nội dung thanh ghi A ra port ngoại

vi.

* Thanh đếm chương trình PC (program counter)

- 1 chương trình đc BVXL thực hiện phải chứa trong BN chính. PC chứa đ.chỉ của lệnh trong BN và chỉ ra cho BVXL biết lệnh tiếp theo nằm ở

ngăn nhớ nào để lấy ra thực hiện.

- trong các BVXL công nghệ cao có cơ chế quản lý BN ảo. Cơ chế đánh địa chỉ ảo có sự biến đổi đ.chỉ ảo thành đ.chỉ VL nội dung của

đ.chỉ lệnh sẽ phức tạp.

* Thanh ghi trạng thái SR (status register)

- dùng để ghi kết quả của các lệnh k.tra, s.sánh và 1 số lệnh tính toán với các thanh ghi

- thanh ghi trạng thái còn đgl thanh ghi cờ, s/dụng các bit cờ có thể thực hiện rẽ nhánh chương trình = các lệnh nháy và rẽ nhánh có đ.kiện

* Con trỏ ngăn xếp SP (stack pointer)

- Ngăn xếp là BN có cơ chế truy cập theo kiểu LIFO, luôn đc truy cập ở đỉnh TOP. Nó làm nhiệm vụ lưu trữ những thông tin phải dùng đi dùng

lại nhiều lần.

- Các lệnh tác động đến ngăn xếp: call, ret, int, …

- Các lệnh chuyên dùng để cất giữ n.dung và phục hồi các thanh ghi của ngăn xếp là push và pop, các lệnh này làm thay đổi đỉnh của ngăn xếp.

- Con trỏ ngăn xếp SP chứa đ.chỉ của đỉnh ngăn xếp và n.dung của SP sẽ thay đổi mỗi khi thực hiện các lệnh vừa nêu trên

- khi khởi động hệ thống máy tính, con trỏ ngăn xếp luôn đc khởi tạo về địa chỉ đỉnh của ngăn xếp.

* Thanh ghi đ.chỉ BN và logic (memory address register and logic)

- có độ dài 16 bit, các đầu ra của nó đc điều khiển nối ra bus đ/c của h.thống máy tính để thực hiện chọn ngăn nhớ or để chọn cổng ngoại vi nào

đó.

- Trong chu kì đọc lệnh, 1 lệnh máy đc đọc từ BN, lúc này ndung thanh ghi đ/c ngăn nhớ và n.dung của thanh đếm lệnh PC là như nhau, nghĩa

là thanh ghi đ.chỉ BN trỏ tới từ lệnh đang đc đọc từ BN.

- Thanh ghi đchỉ BN không thể tự động tăng hay giảm ndung mà nó nhận đchỉ lệnh từ PC, từ SP và thanh ghi chỉ số.

- Phụ thuộc vào các loại VXL, nó có thể có đ.dài khác nhau: 16, 32, 64 bit

* Thanh ghi lệnh IR (instruction register)

- chứa lệnh đang thực hiện

- như là bộ đệm duy trì ndung mã lệnh và đầu ra của IR đưa tới bộ giải mã lệnh để tạo ra chuỗi các tín hiệu điều khiển thực hiện lệnh.

c. Control Unit (đơn vị điều khiển)

- có liên hệ thông tin với t.cả các đ.vị trong BVXL bởi nó đ.khiển toàn bộ h.độg xử lý thông tin bên trong BVXL.

- kqua giải mã lệnh đc đưa đến khối logic điều khiển CL (control logic) tạo ra chuỗi các tín hiệu để đ.khiển quá trình ghi đọc với các thanh ghi

bên trong, tính toán trong ALU

- từ CL, các xung tín hiệu đ.khiển đi ra bus điều khiển của h.thống tác động đến BN hoặc đơn vị I/O để thực hiện trao đổi d.liệu

- CL nhận tín hiệu đ.khiển từ bên ngoài, như tín hiệu ngắt (INT, NMI), HOLD, RESET,… để xử lý bên trog trc khi đưa ra các tín hiệu trả lời

như: chấp nhận ngắt INTA, dừng HALT,…

- CL quyết định thứ tự làm việc của từng đvị trong bộ VXL và sự trao đổi thông tin với thế giới bên ngoài chip VXL.

- CL là trung tâm đ.khiển của BVXL

3. Các vi mạch hỗ trợ cho BVXL

Mỗi loại VXL có những mạch hỗ trợ phù hợp đi theo:

- các bộ VXL công nghệ cao hiện nay (kể từ 80386) đã có những vi mạch VLSI hỗ trợ gộp nhiều chức năng đ.khiển khác nhau đc đưa vào để

có thể thành 1 CPU của 1 máy vi tính.

- Các máy tính thế hệ pentium 586/ 150 – 233 MHz với bảng mẹ PSI/ ISA có các vi mạch VLSI hỗ trợ như: 82437VX, 82438VX, … để tạo

nhịp đồng hồ, điều khiển I/O…

- Các máy vi tính hiện nay đều có khả năng thiết lập ban đầu cho các vi mạch hỗ trợ (chipset), đó là các chế độ chipset features setup,

bios features setup,…

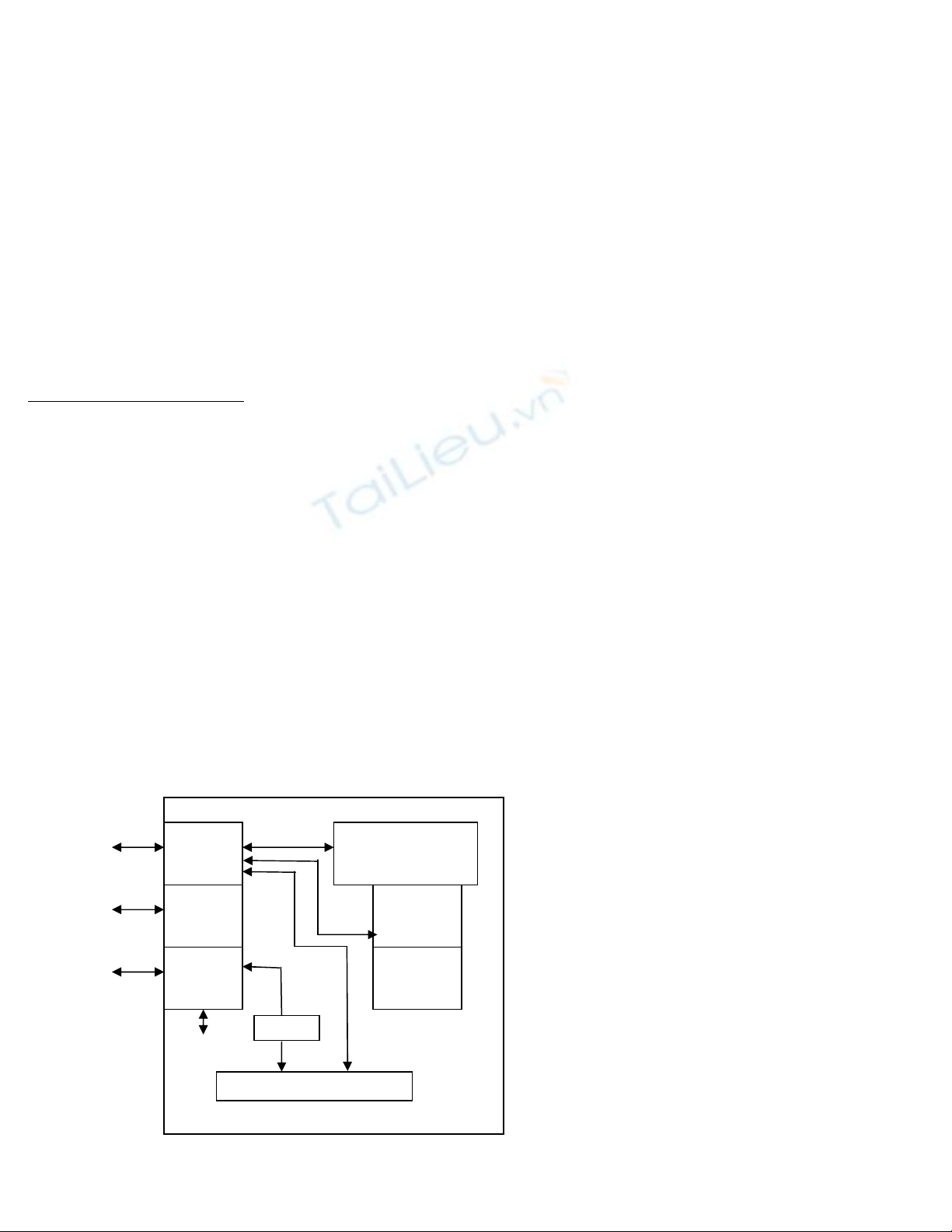

Câu 4: Sơ đồ khối đơn vị giao tiếp bus (BIU) của các bộ VXL công nghệ cao. Giải thích chức năng từng bộ phận: BIU, PUIQ, SFU,

cache, IU, MMU.

Trả lời:

S 32k

Y

S Data bus

T

32 + i

E

M Address Bus

B

S Control Bus

Data

interface

Address

interface

Control

interface

Prefetch Unit And

Instruction Queue

Instruction

Cache

(Icache)

Data Cache

(Dcache

)

MMU

Internal Bus 32n

* Chức năng của từng bộ phận:

1. BIU:

2. PUIQ (khối tiền đọc lệnh và hàng lệnh)

- chứa các mạch logic để đọc trc các lệnh từ Icache và đặt vào hàng xếp các lệnh theo nguyên tắc vào trc ra sau FIFO

- các lệnh này đc chuyển tới khối giải mã lệnh DU (decoding unit)

- phần lớn các họ VXL ngày nay cho phép 1 số lệnh đồng thời đc giải mã (xử lý song song )

3. SFU (special function unit): khối chức năng đặc biệt, có thể là:

- khối đồ họa

- khối xử lý tín hiệu

- khối xử lý ảnh

- bộ XL ma trận và vector

4. Cache: là BN tốc độ nhanh nằm giữa BVXL và BN chính

- Sự tồn tại BN dự trữ với k.thước đủ lớn làm tăng hiệu suất của BVXL vì nó cho phép BVXL truy nhập thông tin nhanh hơn nhiều so với truy

cập vào BN chính

- BN dự trữ kép (dual cache memory) phân ra BN dự trữ các lệnh (Icache), BN dự trữ lưu trữ d.liệu (Dcache). Cả 2 cache đều kết nối với bus

bên trong. Chúng nhận thông tin từ BN chính thông qua bus D.liệu và BIU.

- Icache kết nối trực tiếp với PUIQ, nó chuyển 1 hay 1 số lệnh vào PUIQ trong 1 c.kì

- Thông qua bus D.liệu bên trong BN dự trữ D.liệu (Dcache) và bus D.liệu điều hành (ODB) giao tiếp với các đơn vị chức năng khác (IU, SFU,

FPU)

* Trong nhiều loại VXL còn có thêm BN dự trữ thứ cấp (secondary cache memory)

- cache bên trong chip VXL là cache sơ cấp (primary cache)

- cache thứ cấp nằm bên ngoài chip và giữa cache sơ cấp và BN chính bên trong cấu trúc BN. Nó có tốc độ truy cập nhanh hơn truy cập BN

chính (vì nó nằm bên ngoài BVXL nên nó có thể có dung lượng lớn hơn cache sơ cấp).

- dung lượng của cache thứ cấp có thể lên đến vài MB (pentium III cho phép mở rộng tới 4 MB)

5. IU (integer unit): đơn vị nguyên

- Có đặc tính cấu trúc phục vụ cho xử lý song song nó có các đơn vị thao tác thực hiện các phép số học nguyên cộng/trừ, nhân/chia, có tập

các thanh ghi 32 bit hoặc 64 bit.

- Các BVXL CISC thường có 8 16 thanh ghi.

- Các VXL RISC có tới 32 thanh ghi, đôi khi có hơn 100 thanh ghi.

- Dòng d.liệu đi theo 2 đường để tới các đvị thao tác các phép tính số học. Đvị giải mã phân chia lệnh DID nhận các chỉ thị đã đc giải mã của

CU và gửi chúng tới các đvị x.lý các phép tính thích ứng.

- Các phép tính với số nguyên chuyển tới các đvị x.lý các số nguyên của IU, các phép tính dấu phẩy động chuyển tới đvị x.lý dấu phẩy động

FDU, …

- D.liệu từ Dcache thông qua bus dữ liệu thao tác ODB chuyển tới các đvị x.lý

- Đvị dịch ống cho phép thực hiện các lệnh dịch nhiều bit nhanh trong 1 c.kì đơn.

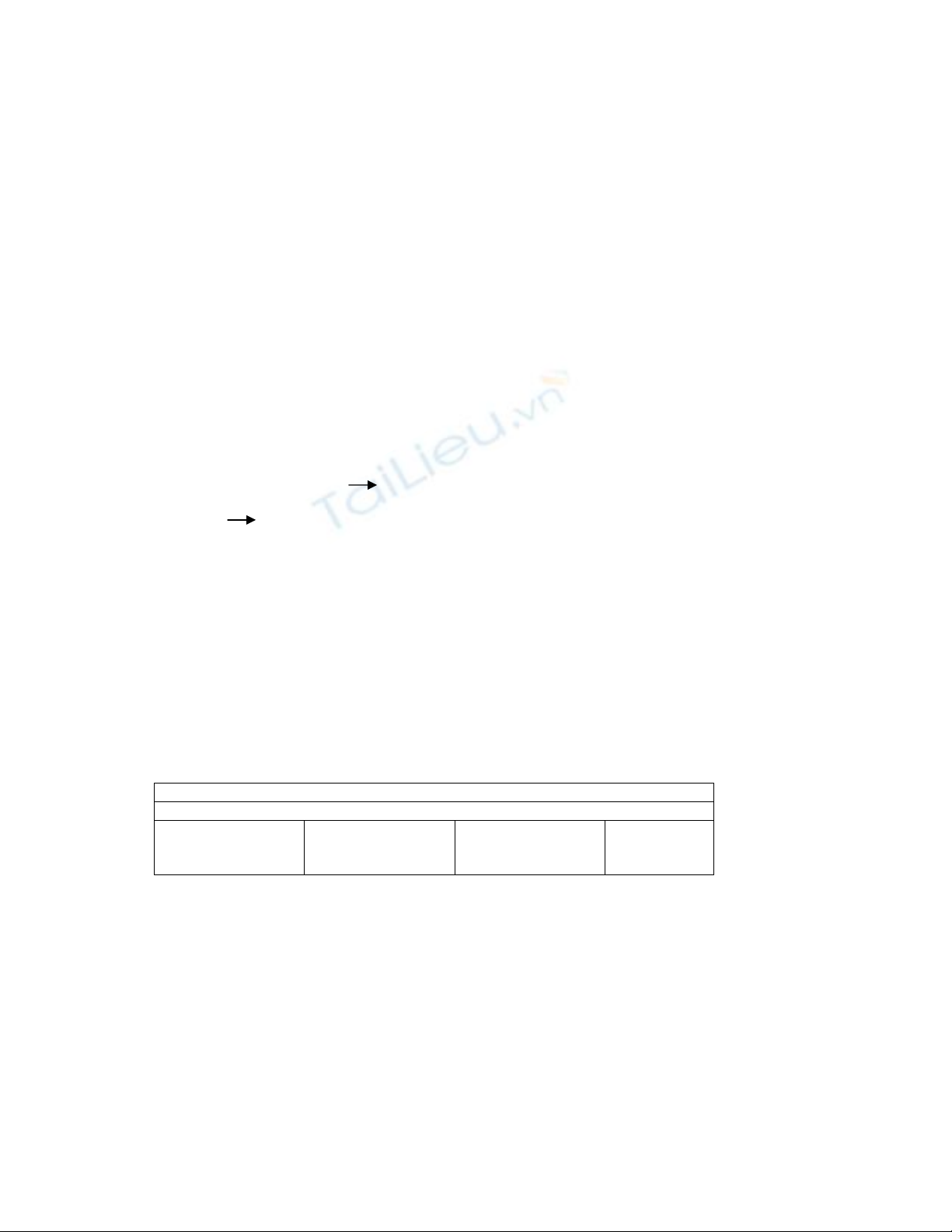

Câu 5: Giải thích phương pháp x.lý lệnh theo kiến trúc siêu hướng (superscalar). Với xu hướng phát triển công nghệ RISC, CU được

hoàn toàn cứng hóa hay thường đc lập trình.

Trả lời:

Kiến trúc siêu hướng (superscalar) thể hiện trong đặc tính thực hiện các lệnh song song . Khối tiền đọc lệnh gửi ra i lệnh cùng 1 thời điểm tới

khối giải mã. Khối điều khiển lần lượt tạo ra các chỉ thị cho 1 số ống thực hiện. Số lượng lệnh không nhất thiết phải = số ống, tuy nhiên số i

lệnh = số ống sẽ là hiệu quả nhất, vì như vậy là i lệnh cùng thực hiện song song .

Decoding Unit

Control Unit

Pipelined

Operation

Unit 1

Pipelined

Operation

Unit 2

…

…

…

Pipelined

Operation

Unit i

Đơn vị điều khiển CU của BVXL có thể hoàn toàn cứng hoặc đc lập trình. Trong hầu hết các BVXL, công nghệ CISC (Intel X86 và Motorola)

CU thường đc lập trình. Với xu hướng phát triển công nghệ RISC, CU đc hoàn toàn cứng hóa nhằm tăng tốc độ thực hiện hâu hết các lệnh

trong 1 chu kì đơn.

Câu 6: Chức năng của đơn vị quản lý BN MMU.

Trả lời:

MMU của bộ VXL có các chức năng:

- Chuyển đổi địa chỉ ảo (virtual address) hay địa chỉ logic thành địa chỉ vật lý (physical), tức là đ.chỉ thực. Địa chỉ vật lý đc chuyển tới Cache,

hoặc thông qua BIU và Bus đ.chỉ tới BN bên ngoài BVXL để chọn vùng nhớ.

- Đảm bảo cơ chế phân trang trong tổ chức BN ảo

- Đảm bảo cơ chế phân đoạn (segment) cho BN

- Bảo vệ BN cho cả hai cơ chế phân trang và phân đoạn

- Quản lý bộ đệm biến đổi truy cập nhanh TLB và quản lý BN dự trữ chuyển đổi ATC. Phục vụ quá trình chuyển đổi các trang nhớ ảo thành

trang nhớ vật lý.

Đ.vị phân trang, TLB (hoặc ATC) đều có trong Mmu của hầu hết các BVXL hiện đại. Trong Intel X86 có đvị phân đoạn. Trong trường hợp

không có TLB, MMU chứa phần logic giám sát truy nhận đến các bảng và thư mục tương ứng trong BN chính.

To Instruction Cache

To Prefetch Unit

To BIU

From IU

Câu 7: Bộ nhớ Cache : Cấu trúc Cache, Thuật toán thay thế (phương pháp thay thế dòng của tập trong Cache)

Trả lời:

1. Cấu trúc Cache:

Cache ghi nhớ một tập hợp A

i

các đ.chỉ của BN chính và các từ d.liệu M(A

i

). Dữ liệu trao đổi giữa Cache và BN chính đc nhóm theo các khối,

hay khối các dòng. Mỗi một khối lệnh như vậy là 1 phân khối của 1 trang nào đó của BN chính. Do đó đ.chỉ chứa trong Cache là đ.chỉ khối.

Các dòng cất giữ trong Cache không có đ.chỉ riêng biệt, mà chúng đc tham chiếu tới nhờ đ.chỉ của chúng lưu trong BN chính. Vị trí chính xác

của các dòng trong Cache đc x.định bằng phương pháp s.xếp đ.chỉ giữa BN chính và Cache. Nội dung của mảng Cache là những bản sao của

tập các khối nhỏ không liên tiếp nhau kèm theo đ.chỉ của BN chính.

2. Thuật toán thay thế (phương pháp thay thế dòng của tập trong Cache)

B1: CPU yêu cầu lệnh/d.liệu lưu trữ trong địa chỉ “a”

B2: Khi đó nội dung từ đ.chỉ “a” không có bên trong BN Cache, CPU phải mang nó về trực tiếp từ BN RAM.

B3: Bộ phận đ.khiển Cache tải 1 hàng (thông thường 64 byte) bắt đầu từ đ.chỉ “a” và bên trong BN Cache. Điều đó nhiều hơn d.liệu CPU đã

yêu cầu, do đó nếu chương trình tiếp tục chạy tuần tự (có nghĩa là yêu cầu đ.chỉ a + 1), lệnh/d.liệu tiếp theo CPU sẽ yêu cầu đã đc tải trong BN

Cache.

B4: Mạch điện gọi là PreFetch tải nhiều v.trí d.liệu hơn sau dòng sau, có nghĩa là bắt đầu những nội dung tải từ địa chỉ a + 64 vào BN Cache.

Nếu chương trình thường chạy tuần tự thì CPU không bao h cần lấy d.liệu trực tiếp từ BN RAM về, nhũng lệnh và d.liệu CPU yêu cầu sẽ

thường nằm trong BN Cache trc khi CPU hỏi tới chúng.

Nếu chương trình thường chạy tuần tự thì CPU không bao giờ cần lấy dữ liệu trực tiếp từ bộ nhớ RAM về (ngoại trừ việc tải lệnh đầu tiên),

những lệnh và dữ liệu CPU yêu cầu sẽ thường nằm trong bộ nhớ Cache trước khi CPU hỏi tới chúng.

Tuy nhiên những chương trình lại không chạy như vậy, chúng sẽ thường nhảy từ vị trí bộ nhớ này tới vị trí bộ nhớ khác. Thách thức lớn nhất

của Bộ phận điều khiển Cache chính là cố gắng phỏng đoán CPU sẽ nhảy tới địa chỉ nào, để tải nội dung của địa chỉ đó vào bên trong bộ nhớ

Cache trước khi CPU yêu cầu nó để tránh trường hợp CPU phải đi tới bộ nhớ RAM của hệ thống, vì điều đó làm chậm hiệu suất làm việc của

toàn bộ hệ thống. Nhiệm vụ này được gọi là Dự đoán rẽ nhánh và những CPU mới đều có đặc điểm này. Những CPU hiện đại có tỉ lệ “hit” ít

nhất là 80%, có nghĩa là ít nhất 80% thời gian CPU không cần truy cập trực tiếp tới bộ nhớ RAM của hệ thống và thay thế vào truy cập tới bộ

nhớ Cache .

Cho dòng X = 275 trong BN chính với số lượng các tập trong Cache là k = 128. Xác định dòng X của BN chính đc xếp vào tập bao

nhiêu của BN Cache.

Dòng 275 sẽ đc xếp như sau : 275/128 = 2 + 19/128, nghĩa là dòng 275 của BN chính đc xếp vào tập 19 trong Cache.

Câu 8: Các kiểu của BVXL song song và h.suất của XL song song . Hãy so sánh cấu trúc máy tính chia sẻ BN và phân tán BN.

Trả lời:

* Các kiểu của BVXL song song :

• Phân loại Flynn:

- Chuỗi lệnh là chuỗi d.liệu SISD

- Chuỗi lệnh là nhiều chuỗi d.liệu SIMD

- Nhiều chuỗi lệnh 1 chuỗi d.liệu MISM

- Nhiều chuỗi lệnh nhiều chuỗi d.liệu MISM

• Phân loại theo cấu trúc:

- Truyền thông theo các biến số dùng chung

Các hệ kết nối chặt chẽ hay các BVXL gọi là VXL đối xứng SMP.

- Hệ thống VXL chia sẻ BN: Cứ 1 VXL có 1 BN I/O dùng riêng của nó

* So sánh cấu trúc máy tính chia sẻ BN và phân tán BN :

Máy tính chia sẻ Bộ nhớ Máy tính phân tán Bộ nhớ

- Hệ thống máy tính với tổ

chức, mà trong đó các đvị nhớ

kết nối trên mạng N làm thành

1 BN chính tổng thể đảm bảo

chia sẻ cho tất cả các đvị x.lý,

gọi là máy tính có BN chia sẻ.

- Hệ thống máy tính mà trong đó mỗi đ.vị x.lý kết nối với

1 đvị nhớ tạo thành 1 khối xử lý riêng (với tài nguyên

riêng) và kết nối với nhau trên mạng kết nối N để trao đổi

tài nguyên, thì gọi là máy tính có BN phân phối tài

nguyên.

Translation

Lookaside

Buffer (TLB)

Internal Bus

Paging

Unit Segmentation

Unit