BỘ CÔNG NGHIỆP

TRƯỜNG ĐẠI HỌC CÔNG NGHIỆP TP HCM

KHOA CÔNG NGHỆ ĐIỆN TỬ

#"

Đồ Án Tốt nghiệp

Đề Tài:

LẬP TRÌNH C CHO HỌ VI ĐIỀU KHIỂN 8051

Đồ Án Tốt Nghiệp

SVTH:Lê Văn Long & Đặng Đức Trung CDDT6K Trang

2

PHẦN I

TỔNG QUAN về ĐỀ TÀI

I. ĐẶT VẤN ĐỀ:

Ngày nay, những ứng dụng của Vi điều khiển đã đi sâu vào đời sống sinh hoạt và

sản xuất của con người. Thực tế hiện nay là hầu hết các thiết bị điện dân dụng hiện nay

đều có sự góp mặt của Vi Điều Khiển và vi xử lí . Ứng dụng vi điều khiển trong thiết kế

hệ thống làm giảm chi phí thiết kế và hạ giá thành sản phẩm đồng thời nâng cao tính ổn

định của thiết bị và hệ thống.Trên thị trường có rất nhiều họ vi điều khiển: họ 8051 của

Intel, 68HC11 của Motorola, Z80 của hãng Zilog, PIC của hãng Microchip, H8 của

Hitachi,vv…

Việc phát triển ứng dụng các hệ vi xử lý đòi hỏi những hiểu biết cả về phần cứng

cũng như phần mềm, nhưng cũng chính vì vậy mà các hệ vi xử lý được sử dụng để giải

quyết những bài toán rất khác nhau. Tính đa dạng của các ứng dụng phụ thuộc vào việc

lựa chọn các hệ vi xử lý cụ thể cũng như vào kỹ thuật lập trình.

Ngày nay các bộ vi xử lý có mặt trong rất nhiều thiết bị điện tử hiện đại: từ đầu

đĩa CD, máy thu hình, máy ghi hình, dàn âm thanh HiFi, bộ điều khiển lò sưởi cho đến

các thiết bị điều khiển dùng trong công nghiệp. Lĩnh vực ứng dụng của các hệ vi xử lý

cũng rất rộng lớn: từ nguyên cứu khoa học, truyền dữ liệu, đến công nghiệp, năng lượng,

giao thông và y tế…

Tùy theo kinh nghiệm và mức độ thông thạo mà chúng ta có thể sử dụng các ngôn

ngữ khác ngoài hợp ngữ như: C, C++, Visual basic để có những chương trình chất lượng

cao hơn.

II. NỘI DUNG CỦA ĐỀ TÀI:

9 Sơ lược về vi điều khiển AT89C51.

9 Khảo sát vi điều khiển AT89C2051 của hãng ATMEL.

• Gồm sơ đồ chân linh kiện.

• Sơ đồ khối của AT89C2051.

• Các nội dụng ứng dụng của AT89C2051.

9 Giới thiệu phần mềm Keil Software µViSion 2

9 Ứng dụng ngôn ngữ C và Assembly điều khiển lập trình led.

• Ứng dụng cho led đơn, led 7 đoạn, led ma trận…

9 Kết luận và hướng phát triển của đề tài.

Đồ Án Tốt Nghiệp

SVTH:Lê Văn Long & Đặng Đức Trung CDDT6K Trang

3

PHẦN II

NỘI DUNG ĐỀ TÀI

CHƯƠNG 1: GIỚI THIỆU BỘ VI ĐIỀU KHIỂN 89C2051 và 89C51

I.GIỚI THIỆU BỘ VI ĐIỀU KHIỂN 89C2051

I.1 CÁC ĐẶC ĐIỂM

9 Tương thích với các sản phẩm của họ MSC-51.

9 2K byte bộ nhớ Flash lập trình được.

9 Khả năng :1000 chu kì ghi/xóa.

9 Tầm điện áp hoạt động từ 2,7 V đến 6V

9 Tầm tần số hoạt động từ 0 Hz đến 21 MHz

9 2 mức khóa bộ nhớ chương trình (program memory).

9 RAM bên trong (internal RAM) có dung lượng 128 x 8 bit.

9 15 đường I/O lập trình được.

9 2 bộ định thời /đếm 16 bit.

9 6 nguồn (nguyên nhân ) ngắt.

9 Kênh nối tiếp UART lập trình được.

9 Các ngõ ra kích LED trực tiếp.

9 Mạch so sánh tương tự trên chip (on-chip analog comparator).

9 Các chế độ nghỉ công suất thấp và chế độ giảm công suất.

I.2 MÔ TẢ

Chip AT89C2051 là chip vi điều khiển CMOS 8 bit điện áp thấp, hiệu suất cao có 2K

byte bộ nhớ Flash chỉ đọc, xóa được và lập trình được PEROM (Flash programmable and

erasable readonly memory). Linh kiện này được sản xuất bằng cách sử dụng công nghệ bộ nhớ

không thay đổi mật độ cao của Atmel và tương thích với tập tệp của MCS-51 chuẩn công

nghiệp. Bằng cách kết hợp một CPU 8-bit đa năng và linh hoạt với Flash trên chip đơn tinh thể ,

Atmel AT89C2051 là chip vi điều khiển mạnh cung cấp giải pháp linh động cao và mang lại

hiệu quả về giá thành cho nhiều ứng dụng điều khiển nhúng (embedded control application).

AT89C2051 cung cấp các đặc tính chuẩn sau đây : bộ nhớ Flash 2K byte , 128 byte

RAM , 15 đường I/O, 2 bộ định thời/đếm 16-bit , kiến trúc ngắt hai mức 5 vector, port nối tiếp

hoàn toàn song công , mạch so sánh tương tự chính xác, mạch dao động và tạo xung clock trên

chip . Ngoài ra AT89C2051 được thiết kế có mạch logic tĩnh cho hoạt động giảm đến tần số 0

Hz và hỗ trợ 2 chế độ tiết kiệm công suất lựa chọn được bằng phần mềm.

Chế dộ nghĩ ( idle mode ) sẽ dùng CPU nhưng vẫn cho phép RAM, các bộ định

thời/đếm, port nối tiếp và hệ thống ngắt tiếp tục hoạt động. Chế độ giảm công suất duy trì nội

dung của RAM nhưng làm dừng mạch dao động, không cho phép mọi chức năng khác của chip

hoạt động cho đến lần reset cứng kế tiếp (nghĩa là ta thiết lập lại trạng thái ban đầu [reset] cho

chiop bằng mạch điện bên ngoài).

Đồ Án Tốt Nghiệp

SVTH:Lê Văn Long & Đặng Đức Trung CDDT6K Trang

4

I.3 CẤU HÌNH CHÂN

Hình 1.1

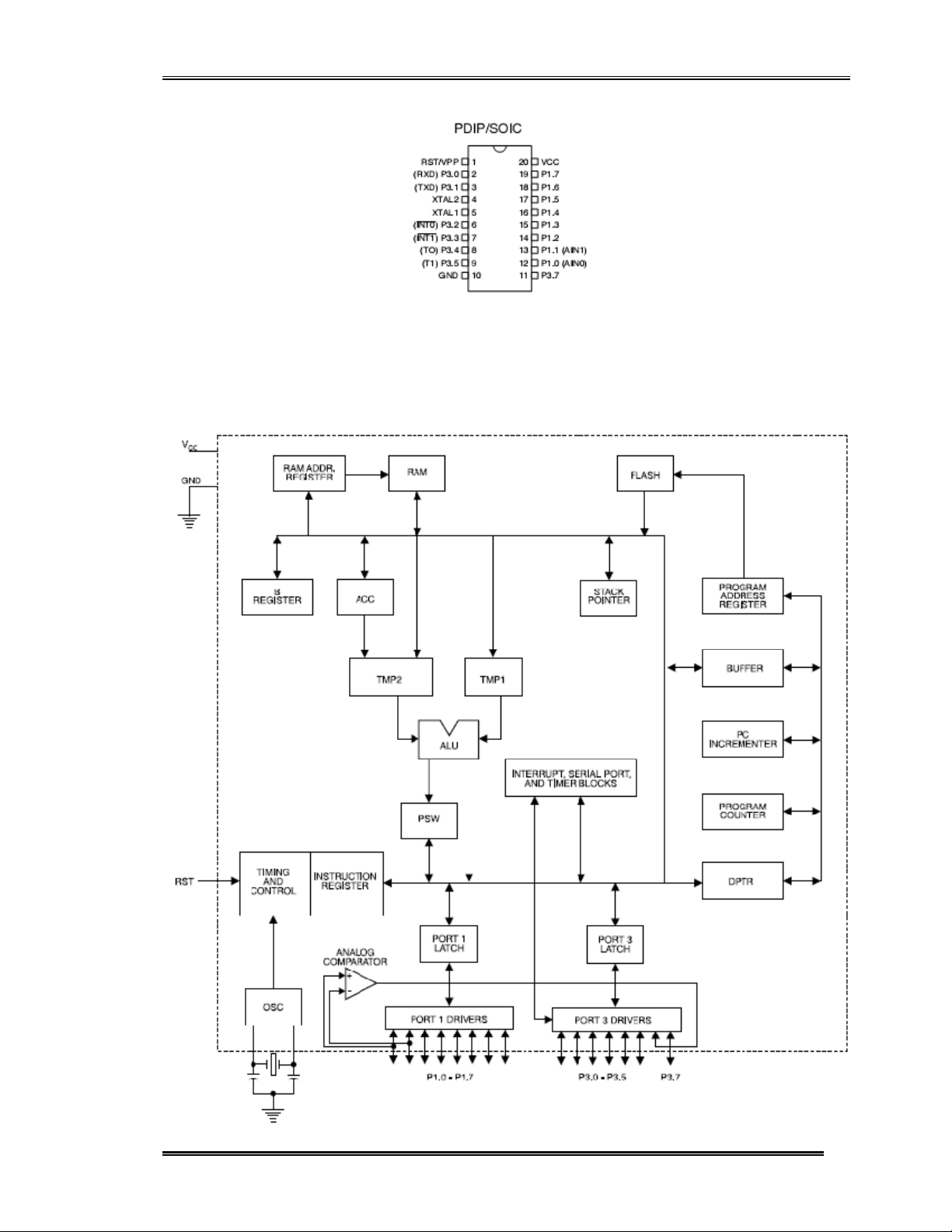

I.4 SƠ ĐỒ KHỐI

Đồ Án Tốt Nghiệp

SVTH:Lê Văn Long & Đặng Đức Trung CDDT6K Trang

5

Hình 1.2

9 RAM ADDR. REGISTER: thanh ghi địa chỉ RAM .

9 RAM: vùng nhớ truy cập ngẫu nhiên (RAM).

9 FLASH: vùng nhớ FLASH.

9 B REGISTER:thanh ghi B.

9 ACC: thanh chứa.

9 STACK POINTER: con trỏ vùng nhớ xếp chồng.

9 PROGRAM ADDRESS REGISTER: thanh ghi địa chỉ chương trình.

9 TMP1: thanh ghi tạm 1

9 TMP2: thanh ghi tạm 2

9 ALU: đơn vị số học/logic.

9 BUFFER: bộ đệm.

9 PC INCREMENTER: bộ tăng thanh ghi đếm chương trình PC.

9 INTERRUPT, SERIAL PORT AND TIMER BLOCKS: các khối ngắt, port nối tiếp

và định thời.

9 PROGRAM COUNTER: bộ đếm chương trình PC.

9 PSW: từ trạng thái chương trình .

9 TIMING AND CONTROL:mạch logic điều khiển và định thời.

9 INSTRUCTION REGISTERED: thanh ghi lệnh.

9 DPTR: con trỏ dữ liệu .

9 PORT1 LATCH: bộ chốt port 1.

9 PORT3 LATCH: bộ chốt port 3.

9 ANALOG COMPARTOR:bộ so sánh tương tự .

9 OSC:mạch dao động.

9 PORT 1 DRIVERS: các mạch kích port 1.

9 PORT 3 DRIVERS: các mạch kích port 3.

I.5 MÔ TẢ CHÂN

VCC

Chân cấp điện áp Vcc cho chip.

GND

Chân nối đất.

Port 1

Port 1 là port I/O (port nhập/xuất: input/output port) hai chiều 8-bit. Các chân của port từ

P1.2 đến P1.7 cung cấp các mạch kéo lên bên trong (internal pull-ups). Các chân P1.0 và P1.1

yêu cầu các mạch kéo lên bên ngoài . P1.0 và P1.1 cũng còn được sử dụng làm ngõ vào dương

(AIN0) và ngõ vào âm (ÁIN), theo thứ tự, của mạch so sánh tương tự chính xác trên chip (on –

chip precision analog comparator).

Các mạch đệm ngõ ra (output buffer) của port 1 có thể hút dòng 20mA và kích trực tiếp

các bộ hiện thị LED. Khi các logic 1 được ghi đến các chân của port 1, các chân này có thể được

sử dụng làm các ngõ vào. Khi các chân từ P1.2 đến P1.7 được sử dụng làm các ngõ vào và được

kéo xuống mức thấp từ bên ngoài, chúng sẽ cung cấp dòng (IIL) do các mạch kéo lên bên trong.

Port 1 cũng nhận dữ liệu chương trình hay dữ kiệu mã (code data) trong thời gian lập trình

và kiểm tra bộ nhớ Flash.

Port 3

Các chân của port 3 từ P3.0 đến P3.5, P3.7 là chân I/O hai chiều với các mạch kéo lên bên

trong. P3.6 được nối dây cứng làm ngõ vào nối đến ngõ ra của mạch so sánh trên chip và không

thể truy cập như một chân I/O có mục đích tổng quát. Các mạch đệm ngõ ra của port 3 có thể hút

dòng 20mA.Khi các logíc được ghi đến các chân của port 3, các chân này được kéo lên mức cao

bởi các mạch kéo lên bên trong và có thể được sử dụng làm các ngõ vào. Khi là các ngõ vào, các

chân nào của port 3 được kéo xuống mức thấp bởi mạch bên ngoài sẽ cung cấp dòng (IIL) do các

![Hệ thống điều khiển nhà thông minh: Luận văn tốt nghiệp [Chuẩn SEO]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260423/hoacattuong2026/135x160/35121777429487.jpg)