1

M CH ĐI N C NG LOGICẠ Ệ Ổ

2

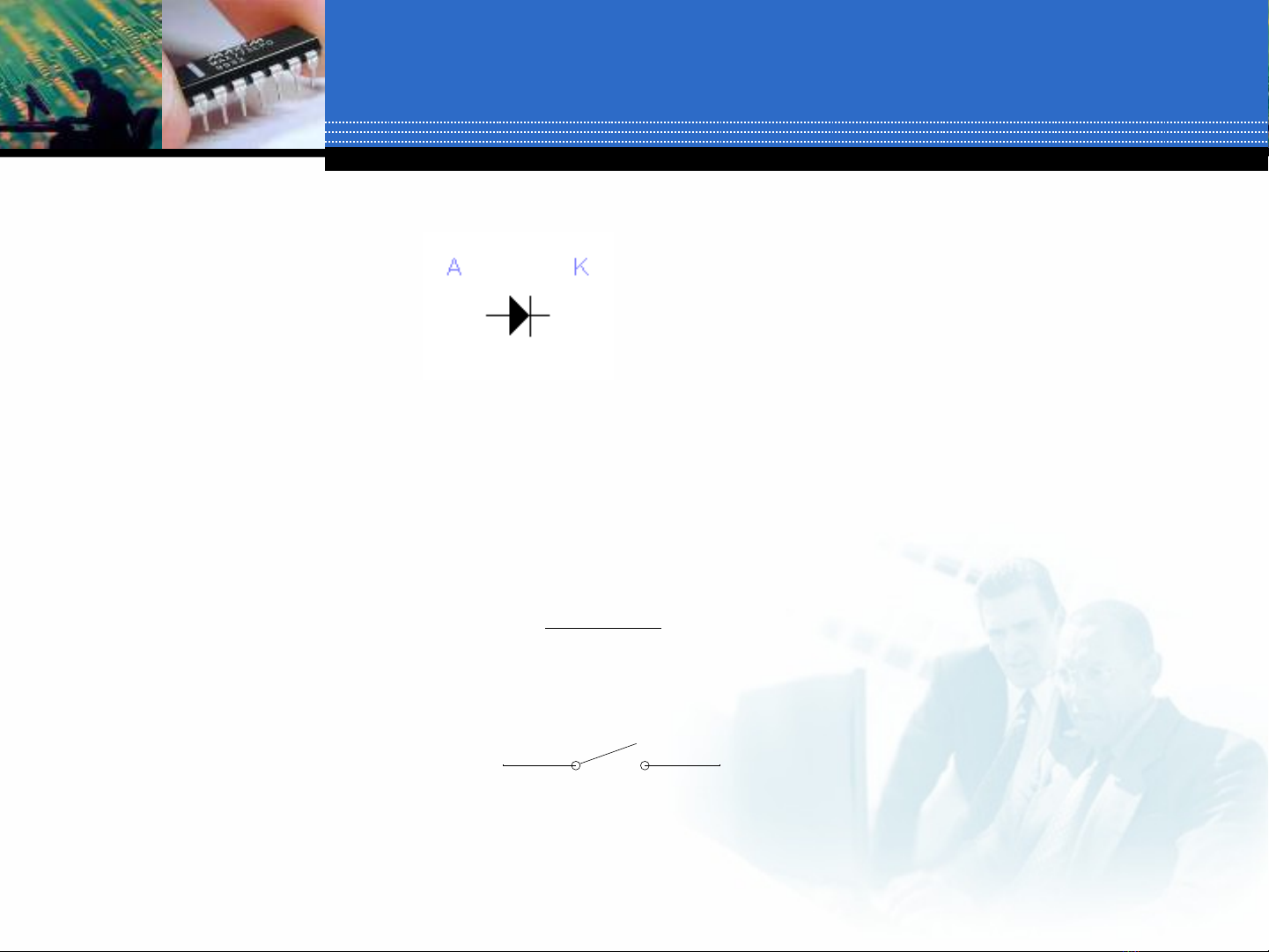

DIODE

Diode:

Kí hi u:ệ

Ch c năng: cho dòng đi n đi qua theo 1 chi u t A đ n ứ ệ ề ừ ế

K

Ho t đ ng:ạ ộ

N u UếA > UK thì IAK > 0, Diode làm vi c ch đ Thôngệ ở ế ộ

N u UếA ≤ UK thì IAK = 0, Diode làm vi c ch đ T tệ ở ế ộ ắ

AK

AK

3

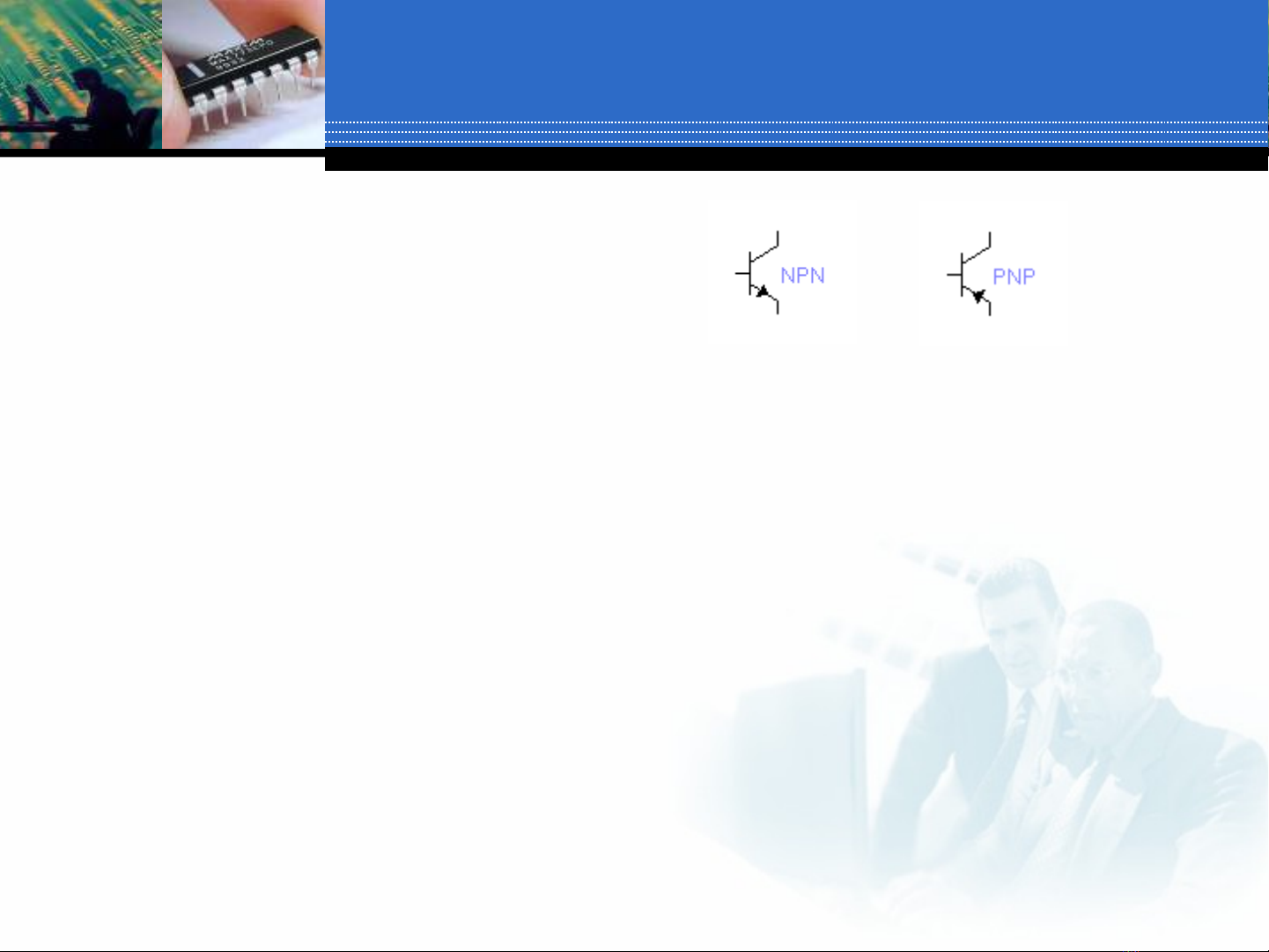

Transistor l ng c c:ưỡ ự

Có 2 lo i: NPN và PNPạ

Transistor có 3 c c:ự

B: Base – c c g cự ố

C: Collector – c c gópự

E: Emitter – c c phátự

Ch c năng: Dùng đ khu ch đ i (thông) dòng Iứ ể ế ạ C b ng ằ

vi c đi u khi n dòng Iệ ề ể B

Ho t đ ng:ạ ộ

IB = 0, Transistor làm vi c ch đ không khu ch đ i (t t), Iệ ở ế ộ ế ạ ắ C = 0

IB > 0, Transistor làm vi c ch đ khu ch đ i (thông), Iệ ở ế ộ ế ạ C = β.IB,

trong đó β là h s khu ch đ i.ệ ố ế ạ

BJT

4

Transistor tr ng (MOSFET kênh c m ng)ườ ả ứ

N: UGS = 0 ⇒ ID = 0 ⇒ T t t hay khóa m (R = ắ ở ∞)

UGS ≥ 0 ⇒ có ID ⇒ T thông hay khóa đóng (R = 1K)

P: Ng c l i kênh Nượ ạ

FET

5

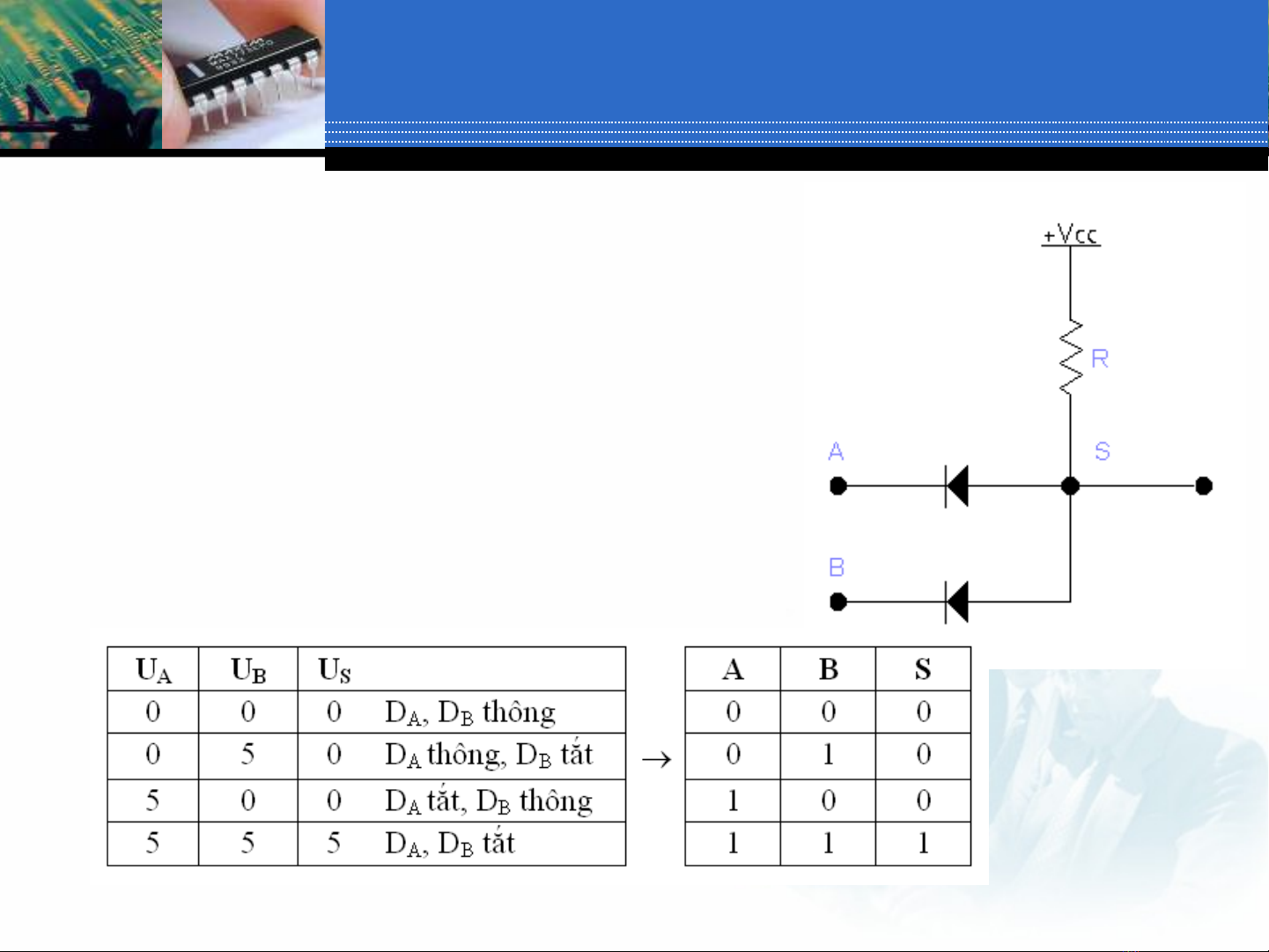

Ph n t AND 2 đ u vào dùng ầ ử ầ

Diode

Xét m ch hình bên.ạ ở

Gi s l y TTL làm chu n cho ả ử ấ ẩ

ho t đ ng c a m ch.ạ ộ ủ ạ

L n l t đ t đi n áp 0V và 5V vào ầ ượ ặ ệ

2 đ u vào A và B, sau đó đo đi n ầ ệ

áp t i đ u ra S, ta có:ạ ầ

S = A.B

![Mạch Điện Điện Trở: [Thêm Mô Tả Chi Tiết Hấp Dẫn Tại Đây]](https://cdn.tailieu.vn/images/document/thumbnail/2013/20130917/butmaulam/135x160/1561226_146.jpg)

![Giáo trình Vô tuyến điện viên hàng hải GMDSS hạng tổng quát: Phần 1 [Chuẩn Nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260504/vispacex_27/135x160/45101777969769.jpg)

![Giáo trình Thực tập điện tử cơ bản: Phần 1 [Full]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260504/vispacex_27/135x160/66001778032993.jpg)