NGÂN HÀNG CÂU HỎI

HỌC PHẦN ĐIỀU KHIỂN LOGIC KHẢ TRÌNH

Câu 1: (4 điểm)

Trình bày hệ logic tổ hợp? Lấy ví dụ minh họa?

Đáp án:

Mạch logic tổ hợp là mạch mà trạng thái đầu ra của mạch chỉ phụ thuộc vào tổ hợp các

trạng thái đầu vào chứ không phụ thuộc vào trình tự tác động của các đầu vào. Theo

quan điểm điều khiển thì mạch tổ hợp là mạch hở, hệ không có phản hồi, nghĩa là

trạng thái đóng mở của các phần tử trong mạch hoàn toàn không bị ảnh hưởng của

trạng thái tín hiệu đầu ra.

Việc phân tích mạch được tiến hành theo các bước sau:

-Thống kê số biến vào và ra, trên cơ sở đó lập bảng mô tả trạng thái của hệ

thống.

- Viết các hàm logic mô tả quan hệ giữa tín hiệu ra theo tín hiệu vào.

Câu 2: (4 điểm)

Nêu và so sánh các phương pháp biểu diễn hàm logic?

Đáp án:

- Phương pháp biểu diễn thành bảng

- Phương pháp hình học

- Phương pháp biểu thức đại số (phương pháp giải tích)

- Phương pháp biểu diễn hàm logic bằng bảng Karnaugh (Các nô)

Nhận xét: so sánh trên các phương diện: độ phức tạp hay đơn giản, cồng kềnh…..

Câu 3: (4 điểm)

Hãy phân tích phương pháp biểu diễn hàm logic bằng phương pháp biểu diễn thành

bảng? Lấy ví dụ?

Câu 4: (4 điểm)

Hãy phân tích phương pháp biểu diễn hàm logic bằng phương pháp hình học ? Lấy ví

dụ?

Câu 5: (4 điểm)

- Hãy phân tích phương pháp biểu diễn hàm logic bằng phương pháp biểu thức đại

số (phương pháp giải tích) ?

Câu 6: (4 điểm)

- Hãy phân tích phương pháp biểu diễn hàm logic bằng bằng bảng Karnaugh (Các

nô)? Lấy ví dụ?

Câu 7: (4 điểm)

Nêu các tính chất cơ bản của hàm logic? Lấy ví dụ minh hoạ?

Đáp án:

Các tính chất của đại số logic được thể hiện ở 4 luật cơ bản là: luật hoán vị, luật kết

hợp, luật phân phối và luật nghịch đảo (định lý De Morgan).

Các luật và một số hệ thức cơ bản là:

1. Định luật giao hoán đối với cộng và nhân logic

a + b = b + a

a . b = b . a

2. Định luật kết hợp đối với cộng và nhân logic

a + ( b + c ) = ( a + b ) + c

a . ( b . c ) = ( a . b ) . c

3. Định luật phân phối

a . ( b + c ) = a . b + a . c

a + b . c = ( a + b ) . ( a + c )

4. Định luật nghịch đảo ( De - Morgan )

= .

= +

Ví dụ SV tự lấy

Câu 8: (4 điểm)

Nêu và so sánh các phương pháp tối giản hàm logic?

Đáp án:

Các phương pháp tối giản và so sánh các phương pháp:

- Phương pháp tối thiểu hoá hàm logic bằng biến đổi đại số

- Phương pháp tối thiểu hoá hàm logic theo thuật toán

+ Tối thiểu hoá hàm logic bằng phương pháp Quine Mc. Cluskey

+ Phương pháp dùng bảng Karnaugh

Câu 9 * : (4 điểm)

Trình bày phương pháp tối thiểu hoá hàm logic bằng biến đổi đại số? Lấy ví dụ?

Câu 10 * : (4 điểm)

Phân tích phương pháp tối thiểu hoá hàm logic theo thuật toán? Lấy ví dụ?

Câu 11: (4 điểm)

Trình bày hệ logic trình tự? Lấy ví dụ?

Khái niệm:

Mạch trình tự hay mạch dãy (sequential circuits) là mạch mà trong đó trạng thái của

đầu ra (tín hiệu ra) không những phụ thuộc tín hiệu vào mà còn phụ thuộc cả vào trình

tự tác động của tín hiệu vào, nghĩa là có nhớ các trạng thái. Như vậy, về mặt thiết bị

thì ở mạch trình tự không chỉ có các phần tử đóng mở mà còn có cả các phần tử nhớ.

Sơ đồ cấu trúc cơ bản của mạch trình tự như hình 3.1. Điểm đặc biệt ở đây là

mạch có “phản hồi” thể hiện qua các biến nội bộ (Y1, Y2 và y1, y2).

Câu 12: (4 điểm)

Trình bày các bước tổng hợp hệ logic trình tự? Lấy ví dụd?

Các bướcd:

Câu 13: (4 điểm)

Trình bày phương pháp biểu diễn hàm logic bằng biểu thức đại số? So sánh với

phương pháp biểu diễn hàm logic bằng bảng trạng thái?

Đáp án:

Phương pháp biểu diễn hàm logic bằng biểu thức đại số gồm 2 cách:

Cách viết hàm dưới dạng tổng chuẩn đầy đủ

- Chỉ quan tâm đến tổ hợp biến mà hàm có giá trị bằng 1. Số lần hàm bằng 1 sẽ

chính là số tích của các tổ hợp biến, mỗi tích được gọi là một mintec, ký hiệu là mi.

- Trong mỗi tích, các biến có giá trị bằng 1 được giữ nguyên, còn các biến có

giá trị bằng 0 thì được lấy giá trị nghịch đảo.

- Hàm tổng chuẩn đầy đủ là tổng các tích đó.

Cách viết hàm dưới dạng tích chuẩn đầy đủ

- Chỉ quan tâm đến tổ hợp biến mà hàm có giá trị bằng 0. Số lần hàm bằng 0 sẽ

chính là số tổng của các tổ hợp biến, mỗi tổng được gọi là một Maxtec, ký hiệu là Mi.

- Trong mỗi tổng, các biến có giá trị bằng 0 được giữ nguyên, còn các biến có

giá trị bằng 1 thì được lấy giá trị nghịch đảo.

- Hàm tích chuẩn đầy đủ là tích các tổng đó.

Câu 14: (4 điểm)

Trình bày cấu trúc bên trong của PLC?

Đáp ánd:

Cấu trúc bên trong của PLCd:

- Bộ nhớ chương trình RAM, ROM

- Một bộ vi xử lý trung tâm CPU, có vai trò xử lý các thuật toán

- Các modul vào/ra tín hiệu

Câu 15: (4 điểm)

Hãy nêu trình tự tối giản hàm lôgic bằng thuật toán Karnaugh?

Đáp ánd:

Bước 1: Biểu diễn hàm đã cho thành bảng Karnaugh.

Bước 2: Xác định các tích cực tiểu hoặc tổng cực tiểu.

Bước 3: Tìm các liên kết phủ tối thiểu các ô “1” (nếu biểu diễn tối thiểu theo

hàm tổng) hoặc các ô “0” (nếu biểu diễn theo hàm tích), sau đó viết hàm kết quả theo

tổng hoặc tích.

Câu 16: (4 điểm)

Hãy trình bày khái niệm hệ điều khiển logic tổ hợp? cho ví dụd?

Đáp ánd:

Mạch logic tổ hợp là mạch mà trạng thái đầu ra của mạch chỉ phụ thuộc vào tổ hợp các

trạng thái đầu vào chứ không phụ thuộc vào trình tự tác động của các đầu vào. Theo

quan điểm điều khiển thì mạch tổ hợp là mạch hở, hệ không có phản hồi, nghĩa là

trạng thái đóng mở của các phần tử trong mạch hoàn toàn không bị ảnh hưởng của

trạng thái tín hiệu đầu ra.

Nguyên tắc chung khi tổng hợp mạch logic tổ hợp là:

+) Từ các yêu cầu công nghệ ta đưa ra được các hàm logic thoả mãn các yêu cầu

đã cho.

+) Thực hiện tổi thiểu hoá các hàm logic đã thiết lập được, tìm ra các hàm tối

giản.

+) Thực hiện mạch logic tổ hợp bằng việc sử dụng các rơle, công tắc tơ (tổng

hợp mạch rơ le), hoặc bằng các phần tử logic AND, OR, NAND, NOR đã chuẩn hoá

đầu vào và đầu ra.

Câu 17: (4 điểm)

Nguyên tắc chung khi tổng hợp mạch logic tổ hợp?

Trình bày các nguyên tắc chung khi tổng hợp mạch logic tổ hợp là:

+) Từ các yêu cầu công nghệ ta đưa ra được các hàm logic thoả mãn các yêu cầu

đã cho.

+) Thực hiện tổi thiểu hoá các hàm logic đã thiết lập được, tìm ra các hàm tối

giản.

+) Thực hiện mạch logic tổ hợp bằng việc sử dụng các rơle, công tắc tơ (tổng

hợp mạch rơ le), hoặc bằng các phần tử logic AND, OR, NAND, NOR đã chuẩn hoá

đầu vào và đầu ra.

Câu 18: (4 điểm)

So sánh hệ điều khiển logic tổ hợp và hệ điều khiển logic trình tự?

Đáp ánd:

- So sánh về cấu trúc, sơ đồ mô phỏng, hệ kín hay hởd?

- So sánh về các phương pháp biểu diễn

- Ưu nhược điểm của từng hệ

Câu 19: (4 điểm)

Trình bày nguyên lý làm việc của PLC?

Đáp ánd:

- Đầu tiên các tín hiệu từ các thiết bị ngoại vi (sensor, contact, …) được đưa vào CPU

thông qua module đầu vào. Sau khi nhận được tín hiệu đầu vào thì CPU sẽ xử lý và

đưa các tín hiệu điều khiển qua module đầu ra xuất ra các thiết bị được điều khiển bên

ngoài theo 1 chương trình đã được lập trình sẵn.

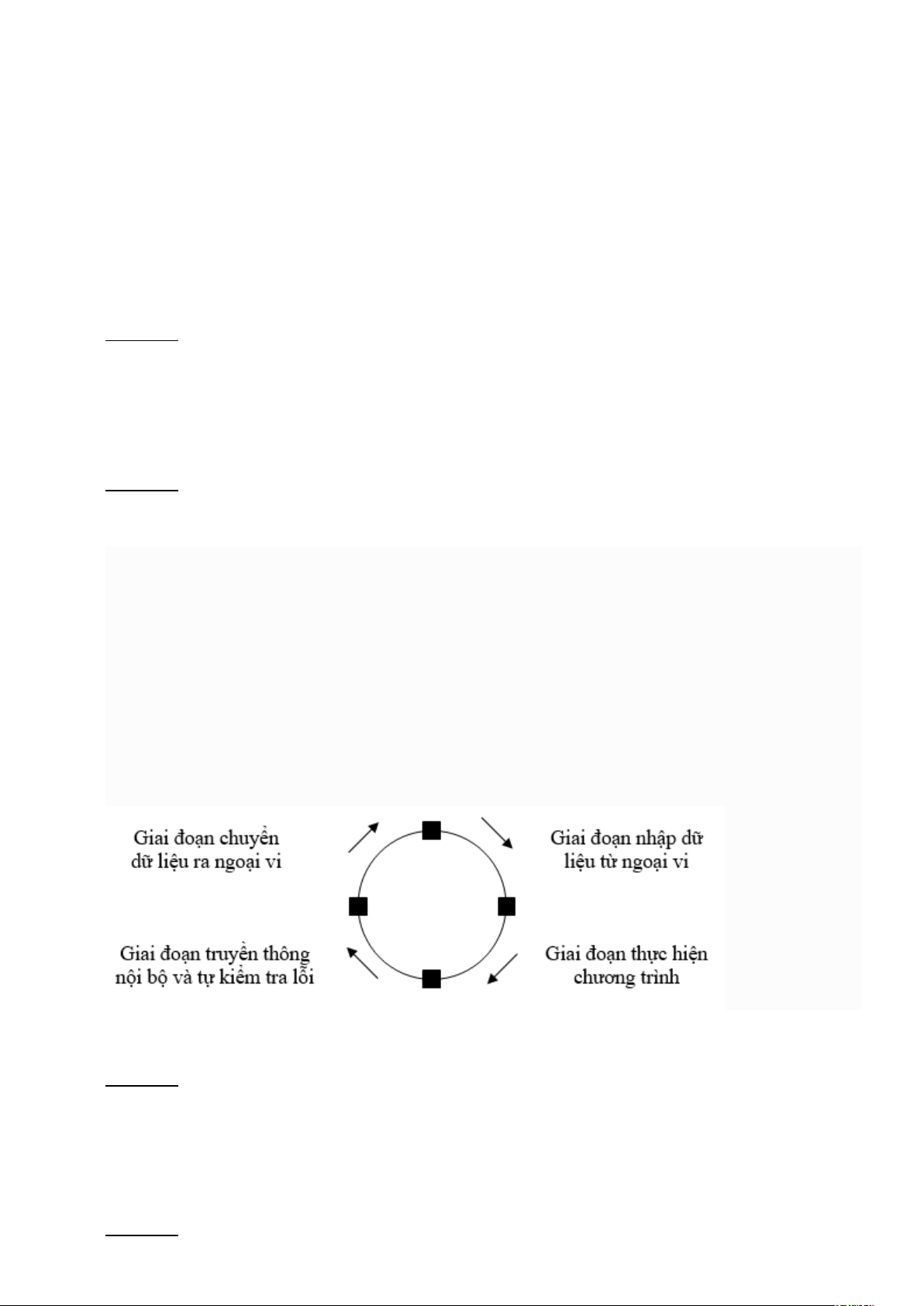

- Một chu kỳ bao gồm đọc tín hiệu đầu vào, thực hiện chương trình, truyền thông nội,

tự kiểm tra lỗi, gửi cập nhật tín hiệu đầu ra được gọi là 1 chu kỳ quét hay 1 vòng quét

(Scan Cycle).

Thường thì việc thực hiện một vòng quét xảy ra trong thời gian rất ngắn (từ 1ms-

100ms). Thời gian thực hiện vòng quét này phụ thuộc vào tốc độ xử lý lệnh củadPLC,

độ dài ngắn của chương trình, tốc độ giao tiếp giữadPLC*và thiết bị ngoại vi.

Câu 20: (4 điểm)

Hãy nêu cấu trúc chương trình của s7-200?

Đáp ánd:

- Chương trình chính (main program)

- Các chương trình con

- Các chương trình xử lý ngắt (nếu có)

Câu 21: (4 điểm)

Trình bày phương pháp biểu diễn hệ điều khiển logic trình tự bằng bảng chuyển trạng

thái?

Đáp ánd:

Phương pháp này mô tả quá trình chuyển đổi trạng thái dưới hình thức bảng

Các cột của bảng ghi các biến vào và biến ra.

Các tín hiệu vào là các tín hiệu điều khiển (, , , … ), có thể là tín hiệu điều

khiển của người vận hành, tín hiệu của thiết bị chương trình hoặc các tín hiệu phát ra

từ các thiết bị công nghệ.

Các tín hiệu ra (Y1, Y2, …) là tín hiệu kết quả của quá trình điều khiển và ghi ở

cột đầu ra.

Các hàng của bảng ghi các trạng thái trong của mạch (S1, S2, S3, …). Số hàng của

bảng chỉ rõ số trạng thái trong cần có của hệ.

Các ô giao nhau của cột biến vào và các hàng trạng thái sẽ ghi trạng thái của mạch.

Nếu trạng thái mạch trùng với tên hàng thì đó là trạng thái “ổn định”, nếu trạng thái

mạch không trùng với tên hàng thì đó là trạng thái “không ổn định”.

Các ô giao nhau của cột tín hiệu ra và các hàng trạng thái sẽ ghi giá trị tín hiệu ra

tương ứng.

Câu 22: (4 điểm)

Trình bày phương pháp biểu diễn hệ điều khiển logic trình tự bằng đồ hình Mealy?

Đáp ánd:

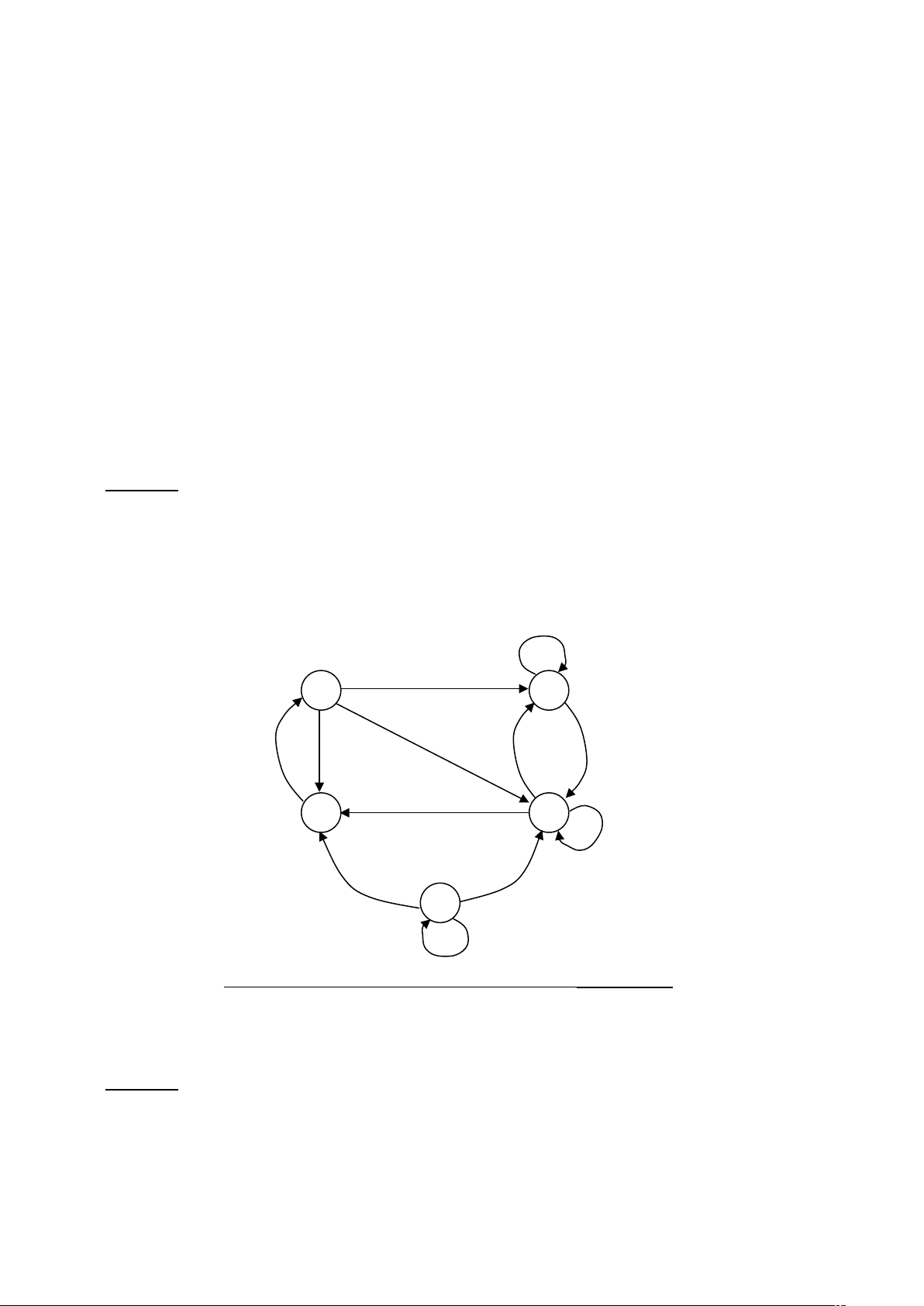

Đồ hình Mealy gồm các đỉnh biểu diễn các trạng thái trong của mạch và các cung định

hướng, trên các cung ghi biến tác động và kết quả hàm khi chịu sự tác động của biến

đó. Đồ hình Mealy chính là chuyển bảng trạng thái thành dạng đồ hoạ.

Lấy ví dụ:

Câu 23: (4 điểm)

Trình bày phương pháp biểu diễn hệ điều khiển logic trình tự bằng đồ hình Moore?

Đáp ánd:

Bước 1: Từ các ô ứng với cặp trạng thái và kết quả ở hình 3.9, ta gán một trạng thái

tương đương Q cho đồ hình Moore.

Bước 2: Thành lập bảng chuyển đổi trạng thái cho đồ hình Moore.

Bước 3: Dựa vào bảng trạng thái (hình 3.11), ta vẽ được đồ hình Moore

1 2

3 4

5

(++

)/1

/

0

/

0

/

0

/

0

/

1

/

0

/

0

/

1

/

0

(+)/

1

/

0

. Đồ hình Mealy ứng với bảng trạng thái hình 3.9

![Thí nghiệm PLC: [Hướng dẫn chi tiết/ Thực hành/ Cơ bản và nâng cao]](https://cdn.tailieu.vn/images/document/thumbnail/2017/20170821/kloiroong10/135x160/391503277956.jpg)

![Giáo trình Xử lý sự cố Diesel tàu thủy (Nghề Khai thác máy tàu thủy, Trình độ Trung cấp) - Trường Cao đẳng Nông nghiệp Thanh Hóa [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260508/songngu_011/135x160/23801778744471.jpg)