Tài li u tham kh o cho môn Vi x lýệ ả ử Các h vi x lý th h m iệ ử ế ệ ớ

M C L CỤ Ụ

L I NÓI Đ UỜ Ầ ......................................................................................................................1

CH NG1. H VI ĐI U KHI N 8051ƯƠ Ọ Ề Ể ............................................................................4

1.1. GI I THI U C U TRÚC PH N C NG H MCS-51 (89C51):Ớ Ệ Ấ Ầ Ứ Ọ ..........................4

1.1.1. Gi i thi u h MCS -51ớ ệ ọ ......................................................................................4

1.1.2. KH O SÁT S Đ CHÂN 89C51, CH C NĂNG T NG CHÂNẢ Ơ Ồ Ứ Ừ ...............5

1.1.2.1 S đ chân 89C51ơ ồ .......................................................................................5

1.1.2.2. Ch c năng các chân c a 89C51ứ ủ ..................................................................6

1.1.3. C U TRÚC BÊN TRONG VI ĐI U KHI NẤ Ề Ể ...................................................8

1.1.3.1. T ch c b nhổ ứ ộ ớ...........................................................................................8

1.1.3.2. Các thanh ghi có ch c năng đ c bi t:ứ ặ ệ .......................................................11

1.1.3.3. B nh ngoài (External memory):ộ ớ .............................................................14

1.1.4. HO T Đ NG TIMER C A 89C51Ạ Ộ Ủ ................................................................16

1.1.4.1. Gi i thi uớ ệ ..................................................................................................16

1.1.4.2. Thanh ghi đi u khi n Timer TCON:ề ể ........................................................17

1.1.4.3. Thanh ghi mode timer (TMOD):................................................................18

1.1.4.4. Các mode và c trànờ..................................................................................18

1.1.4.5. Các ngu n xung clock (CLOCK SOURCES):ồ..........................................20

1.1.4.6. S b t đ u, d ng và đi u khi n các timer:ự ắ ầ ừ ề ể .............................................21

1.1.4.7. S kh i đ ng và truy xu t các thanh ghi timer:ự ở ộ ấ .......................................22

1.1.5. C NG N I TI PỔ Ố Ế .............................................................................................22

1.1.5.1. Gi i thi u:ớ ệ .................................................................................................22

1.1.5.2. Thanh ghi port n i ti p:ố ế ............................................................................23

1.1.5.3. Các ch đ ho t đ ngế ộ ạ ộ ..............................................................................24

1.1.6. T CH C NG T C A MCS51Ổ Ứ Ắ Ủ .....................................................................26

1.1.6.1. u tiên ng t:Ư ắ .............................................................................................27

1.1.6.2. H i vòng tu n t :ỏ ầ ự ......................................................................................27

1.1.7. TÓM T T T P L NH C A 89C51Ắ Ậ Ệ Ủ ................................................................28

1.1.7.1. Các ch đ đ nh v đ a ch (addressing mode):ế ộ ị ị ị ỉ .........................................28

1.1.7.2. Tóm t t t p l nh c a h MCS - 51:ắ ậ ệ ủ ọ ........................................................28

1.2 VI ĐI U KHI N AT89C55Ề Ể .....................................................................................31

1.2.1 Đ c tr ngặ ư .....................................................................................................31

1.2.2. Ph n mô tầ ả.......................................................................................................32

1.3 VI ĐI U KHI N AT89C54/58Ề Ể ................................................................................48

1.3.1 Mô tả..................................................................................................................48

1.3.2.T ch c b nhổ ứ ộ ớ.................................................................................................49

1.4 VI ĐI U KHI N AT89C2051Ề Ể ................................................................................55

1.4.1 Đ c tr ng c a AT89C2051ặ ươ ủ ............................................................................55

1.4.2 Mô tả..................................................................................................................55

CH NG 2. H VI ĐI U KHI N AVR AT90S8535ƯƠ Ọ Ề Ể ....................................................57

2.1 Các đ c tínhặ..............................................................................................................57

2.2. Ph n mô tầ ả...........................................................................................................59

CH NG 3. CÔNG NGH CHIP PSoCƯƠ Ệ ..........................................................................77

3.1 Chíp PSoC CY8C29x66.......................................................................................77

3.1.1 Ch c năngứ....................................................................................................77

3.1.2 S l c ch c năng c a PSoCơ ượ ứ ủ .....................................................................79

3.2.

Ngôn ng l p trình cho PSoCữ ậ

..............................................................................84

3.3 Gi i thi u nh ng nét c b n v IDEớ ệ ữ ơ ả ề .................................................................85

B môn Công ngh đi u khi n t đ ngộ ệ ề ể ự ộ 1Khoa CNTT - ĐHTN

Tài li u tham kh o cho môn Vi x lýệ ả ử Các h vi x lý th h m iệ ử ế ệ ớ

TÀI LI U THAM KH OỆ Ả ...................................................................................................98

M C L CỤ Ụ .............................................................................................................................1

B môn Công ngh đi u khi n t đ ngộ ệ ề ể ự ộ 2Khoa CNTT - ĐHTN

Tài li u tham kh o cho môn Vi x lýệ ả ử Các h vi x lý th h m iệ ử ế ệ ớ

L I NÓI Đ U Ờ Ầ

Trong s phát tri n c a đ t n c, T đ ng hoá đóng vai trò r t quan tr ng trong sự ể ủ ấ ướ ự ộ ấ ọ ự

phát tri n đó. Các h th ng t đ ng hoá đ c ng d ng trong m i lĩnh v c c a đ i ể ệ ố ự ộ ượ ứ ụ ọ ự ủ ờ s ngố

xã h i cũng nh trong các dây truy n s n xu t. ộ ư ề ả ấ

Đ xây d ng lên các h th ng t đ ng hoá ph i c n r t nhi u ki n th c nh : Phân ể ự ệ ố ự ộ ả ầ ấ ề ế ứ ư

tích h th ng, thi t k đánh giá h th ng, ki n th c v ph n c ng, ki n th c v ph n ệ ố ế ế ệ ố ế ứ ề ầ ứ ế ứ ề ầ

m m…. Vì v y đòi h i các k s t đ ng hoá ph i có m t n n ki n th c v ng vàng. ề ậ ỏ ỹ ư ự ộ ả ộ ề ế ứ ữ

Tài li u này cung c p các ki n th c b xung cho môn vi x lý. N i dung c a tàiệ ấ ế ứ ổ ử ộ ủ

li u g m 3 ch ng: ệ ồ ươ

Ch ng 1: Cung c p ki n th c c b n cho vi đi u khi n h 8051 nh :ươ ấ ế ứ ơ ả ề ể ọ ư

AT89C2051, AT89C51/52, AT89C55WD, SST89C54/58.

Ch ng 2: Mô t nh ng ki n th c chung nh t v h vi đi u khi n AVR:ươ ả ữ ế ứ ấ ề ọ ề ể

AT90S8535 và AT89LS8535.

Ch ng 3: Cung c p m t vi đi u khi n PSoC. Vi đi u khi n này đang đ c sươ ấ ộ ề ể ề ể ượ ử

d ng nhi u trong công nghi p. ụ ề ệ

Tài li u này đ c so n trong m t th i gian ng n nên còn r t nhi u l i. Tác gi r tệ ượ ạ ộ ờ ắ ấ ề ỗ ả ấ

mong đ c s góp ý c a các đ c gi . M i th c m c xin liên h v i tác gi t i B mônượ ự ủ ộ ả ọ ắ ắ ệ ớ ả ạ ộ

Đi u khi n t đ ng - Khoa CNTT - Đ i h c Thái Nguyên. ề ể ự ộ ạ ọ

B môn Công ngh đi u khi n t đ ngộ ệ ề ể ự ộ 3Khoa CNTT - ĐHTN

Tài li u tham kh o cho môn Vi x lýệ ả ử Các h vi x lý th h m iệ ử ế ệ ớ

CH NG1. H VI ĐI U KHI N 8051 ƯƠ Ọ Ề Ể

1.1. GI I THI U C U TRÚC PH N C NG H MCS-51 (89C51): Ớ Ệ Ấ Ầ Ứ Ọ

1.1.1. Gi i thi u h MCS -51 ớ ệ ọ

* MCS-51 là h IC (integrated circuit) vì đi u khi n (Microcontroller) do hãng ọ ề ể

Intel

s n xu t. Các IC tiêu bi u cho h MSC-51 là: 8051, 8031, 89C51, 892051, ả ấ ể ọ

8751,...

Vi c x lý trên Byte và các toán s h c c u trúc d li u đ c th c hi n b ng ệ ử ố ọ ở ấ ữ ệ ượ ự ệ ằ nhi u chề ế

đ truy xu t d li u nhanh trên RAM n i. T p l nh cung c p m t b ng ti n ộ ấ ữ ệ ộ ậ ệ ấ ộ ả ệ d ng c aụ ủ

nh ng l nh s h c 8 Bit g m c l nh c ng, tr , nhân và l nh chia. Nó cung ữ ệ ố ọ ồ ả ệ ộ ừ ệ c p nh ngấ ữ

h tr m r ng trên Chip dùng cho nh ng bi n m t Bit nh là ki u d li u riêng bi tỗ ợ ở ộ ữ ế ộ ư ể ữ ệ ệ

cho phép qu n lý và ki m tr a Bit tr c ti p trong đi u khi n. ả ể ự ế ề ể

* 89C51 là m t vi đi u khi n 8 Bit, ch t o theo công ngh CMOS ch t l ngộ ề ể ế ạ ệ ấ ượ

cao, v i 4 KB EEPROM (Flash Programmable and erasable read only memory). Thi t bớ ế ị

này đ c ch t o b ng cách s d ng b nh không b c h i m t đ cao c a ATMEL ượ ế ạ ằ ử ụ ộ ớ ố ơ ậ ộ ủ và

t ng thích v i chu n công nghi p MCS - 51 v t p l nh và các chân ra. ATMELươ ớ ẩ ệ ề ậ ệ

AT89C51 là m t vi đi u khi n m nh (có công su t l n) mà nó cung c p m t s linhộ ề ể ạ ấ ớ ấ ộ ự

đ ng cao và gi i pháp v giá c đ i v i nhi u ng d ng vì đi u khi n. ộ ả ề ả ố ớ ề ứ ụ ề ể

Các đ c đi m c a 89C51 đ c tóm t t nh sau: ặ ể ủ ượ ắ ư

* 4 KB b nh có th l p trình l i nhanh. *ộ ớ ể ậ ạ

T n s ho t đ ng t : 0Hz đ n 24 MHz. * 2ầ ố ạ ộ ừ ế

b Timer/counter 16 Bit ộ

* 128 Byte RAM n i ộ

* 4 Port xu t/ nh p I/O 8 bít *ấ ậ

Giao ti p n i ti p ế ố ế

* 64 KB vùng nh mã ngoài ớ

* 64 KB vùng nh d li u ngoài ớ ữ ệ

* X lý Boolean (ho t đ ng trên bit đ n) *ử ạ ộ ơ

210 v trí nh có th đ nh v bit. ị ớ ể ị ị

B môn Công ngh đi u khi n t đ ngộ ệ ề ể ự ộ 4Khoa CNTT - ĐHTN

Tài li u tham kh o cho môn Vi x lýệ ả ử Các h vi x lý th h m iệ ử ế ệ ớ

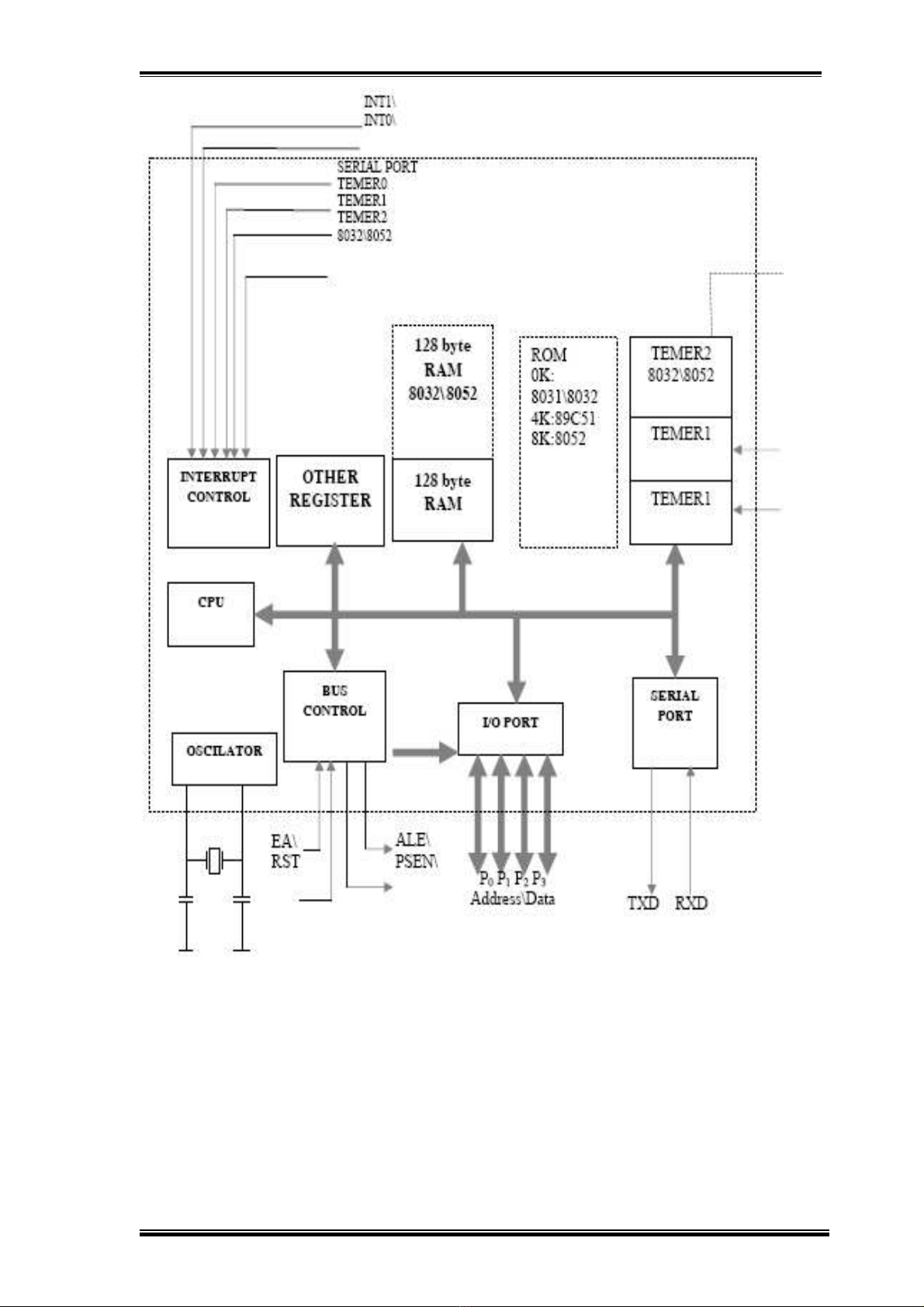

Hình 1.1. S đ kh i MSC-51ơ ồ ố

1.1.2. KH O SÁT S Đ CHÂN 89C51, CH C NĂNG T NG CHÂNẢ Ơ Ồ Ứ Ừ

1.1.2.1 S đ chân 89C51ơ ồ

B môn Công ngh đi u khi n t đ ngộ ệ ề ể ự ộ 5Khoa CNTT - ĐHTN

![Đề cương đề tài nghiên cứu khoa học [chuẩn nhất/mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251117/duong297/135x160/26111763433948.jpg)