Tuyển tập Báo cáo Hội nghị Sinh viên Nghiên cứu Khoa học lần thứ 7 Đại học Đà Nẵng năm 2010

562

THIẾT KẾ VÀ THỰC HIỆN SRAM IP CORE

TRÊN HỆ THỐNG NHÚNG FPGA

DESIGN AND IMPLEMENTATION SRAM IP CORE

ON EMBEDDED FPGA SYSTEM

SVTH: Nguyễn Tiến Chuẩn, Phan Tuấn Vĩ

Lớp 07ĐT2, 07ĐT1, Khoa Điện, Trường Cao đẳng Công Nghệ

GVHD: ThS. Nguyễn Thị Khánh Hồng

Khoa Điện, Trường Cao đẳng Công Nghệ

TÓM TẮT

Mục đích chính của đề tài này là nghiên cứu việc lập trình cho FPGA dựa trên các ngôn

ngữ mô tả phần cứng (HDL), kiểm nghiệm kết quả dựa trên các công cụ mô phỏng (Simulation

Tools),và cuối cùng là cho thi hành trên Kit thực hành FPGA Spartan3 của hãng Xilinx,.Cụ thể ở đề

tài là xây dựng một bộ điều khiển SRAM (SRAM Controller) trên nền FPGA, thực thi việc giao tiếp

giữa SRAM với hệ thống Vi xử lý Microblaze.

ABSTRACT

The main purpose of this subject researchs the program for FPGA based on Hardware

Decription Language (HDL), uses the simulation tools for testing the results, and implement them

on FPGA Spartan 3 kit come from Xilinx company. Especially, the topic sucessfully designs the

SRAM controller based on FPGA, implements the interfacing SRAM with Microblaze system.

1. Đặt vấn đề

Một kiểu bộ nhớ thường được sử dụng đó là RAM tĩnh không đồng bộ(SRAM).

Không giống như các thanh ghi, nơi mà bên trong dữ liệu được lấy mẫu và lưu trữ tại một

sườn của tín hiệu đồng hồ (clock signal), việc truy cập dữ liệu từ SRAM không đồng bộ trở

nên phức tạp hơn. Một công đoạn đọc hoặc ghi yêu cầu: dữ liệu (data), địa chỉ (address) ,

và các tín hiệu điều khiển (control signals) phải được đặc tả một cách cụ thể, và các tín

hiệu này phải được ổn định trong những khoảng thời gian nhất định của thao tác đọc hoặc

viết dữ liệu. Chúng ta thường sử dụng một bộ điều khiển bộ nhớ (memory controller) như

một bộ giao tiếp (interfacer), nơi mà các lệnh được lấy ra từ hệ thống chính đồng bộ (main

system synchronously) và sau đó phát ra các tín hiệu điều khiển với thời gian hợp lí để truy

cập SRAM. Bộ điều khiển bao bọc

lấy hệ thống chính từ các thời điểm

chi tiết và làm cho việc truy cập bộ

nhớ xuất hiện giống như một thao

tác đồng bộ.

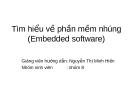

2. Sơ đồ khối và các tín hiệu I/O

của SRAM IS61LV25616AL

Kit thực hành FPGA

Spartan3 của hãng Xilinx có chứa

2 SRAM 256Kx16 .Mỗi SRAM có bus địa chỉ (ad) 18 bit, bus dữ liệu 2 hướng (dio) 16 bit,

Hình 1. Sơ đồ khối chức năng

Tuyển tập Báo cáo Hội nghị Sinh viên Nghiên cứu Khoa học lần thứ 7 Đại học Đà Nẵng năm 2010

563

và 5 tín hiệu điều khiển.

Bus dữ liệu được chia thành 2 kiểu : byte cao (I/O 8-I/O 15), và byte thấp (I/O 0-

I/O 7), mà có thể được truy cập cá nhân riêng biệt. Các tín hiệu điều khiển gồm :

ce (chip enable):kích hoạt hay không kích hoạt chip (SRAM)

we(write enable):kích hoạt hay không kích hoạt thao tác ghi dữ liệu vào SRAM

oe(output enable):kích hoạt hay không kích hoạt thao tác xuất dữ liệu từ SRAM

ub(upper byte enable):kích hoạt hay không kích hoạt chế độ làm việc với byte

cao của SRAM

lb(lower byte enable):kích hoạt hay không kích hoạt chế độ làm việc với byte

thấp của SRAM

Tất cả các tín hiệu đều tích cực ở mức thấp (mức 0).

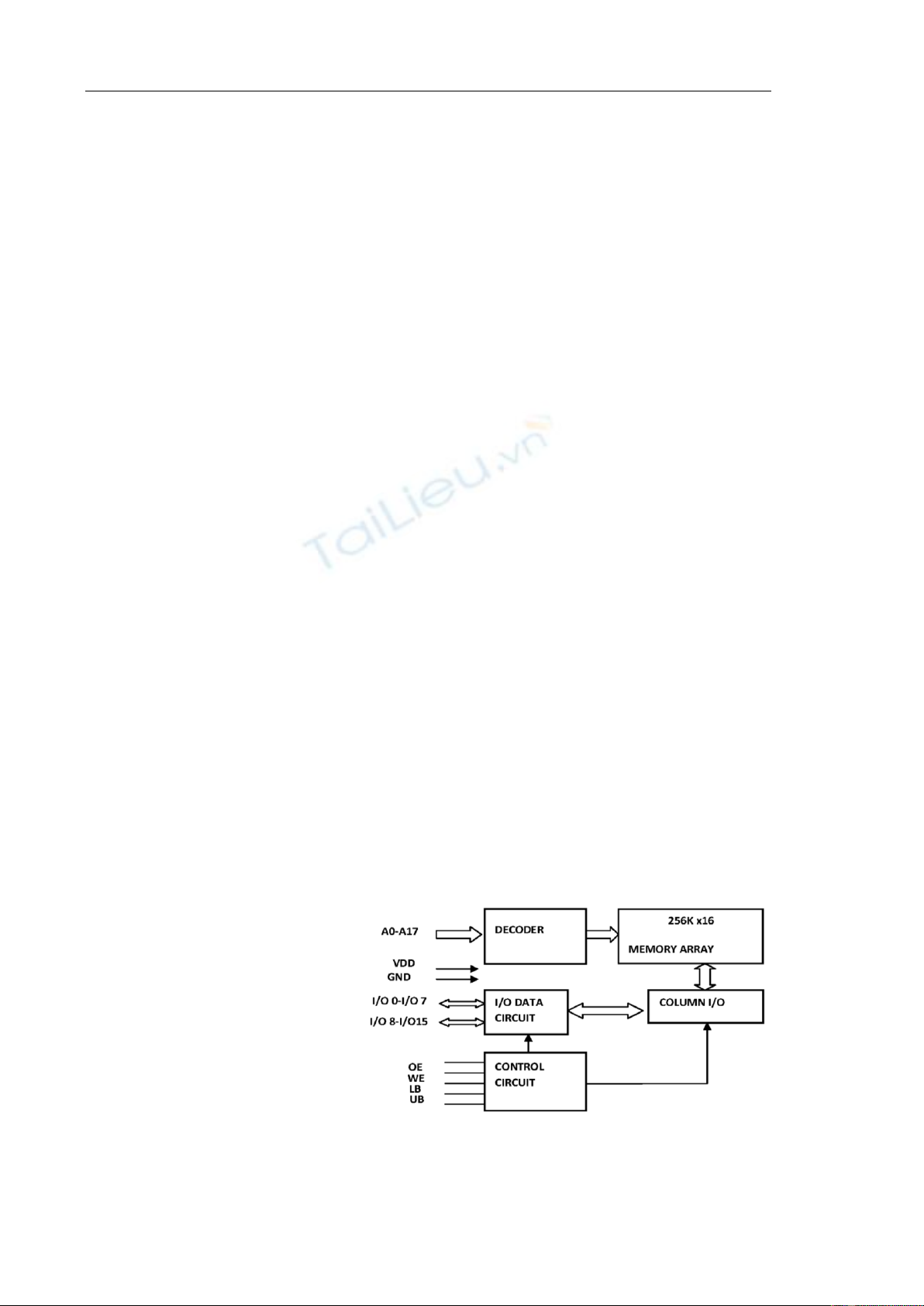

3. Thiết kế một bộ điều khiển bộ nhớ cơ bản (Basic Memory Controler)

3.1. Mô hình giao tiếp giữa hệ thống với SRAM

addr

data_f

data_s_r

VXL

MICROBLAZE Memory

Controller SRAM

data_s_ur

mem

R_W

ready

add

dio

we

oe

0

0

0

Hình 2.Mô hình giao tiếp giữa hệ thống và SRAM thông qua bộ điều khiển (SRAM Controler)

Bộ điều khiển bộ nhớ cơ bản cung cấp một “vỏ bọc đồng bộ “ bên ngoài SRAM.

Khi hệ thống chính muốn truy cập vào bộ nhớ,nó sẽ đặt địa chỉ,hoặc địa chỉ và dữ liệu lên

trên các Bus tương ứng

và kích hoạt lệnh. Tại

mỗi sườn lên của tín

hiệu đồng hồ,tất cả các

tín hiệu được lấy mẫu

bởi bộ điều khiển bộ

nhớ,và các công đoạn

yêu cầu được thực hiện

một cách phù hợp.

3.2. Sơ đồ khối đường

dẫn dữ liệu

Đường dẫn dữ

liệu (Data Path) của bộ

điều khiển SRAM bao

gồm một thanh ghi địa

chỉ và hai thanh ghi dữ

Hình 3. Sơ đồ khối đường dẫn dữ liệu của bộ điều khiển SRAM

Tuyển tập Báo cáo Hội nghị Sinh viên Nghiên cứu Khoa học lần thứ 7 Đại học Đà Nẵng năm 2010

564

liệu. Vì rằng Bus dữ liệu (Data Bus) thực hiện với dữ liệu 2 hướng, nên việc sử dụng bộ

đệm 3 trạng thái (Tri-State Buffer) là cần thiết.

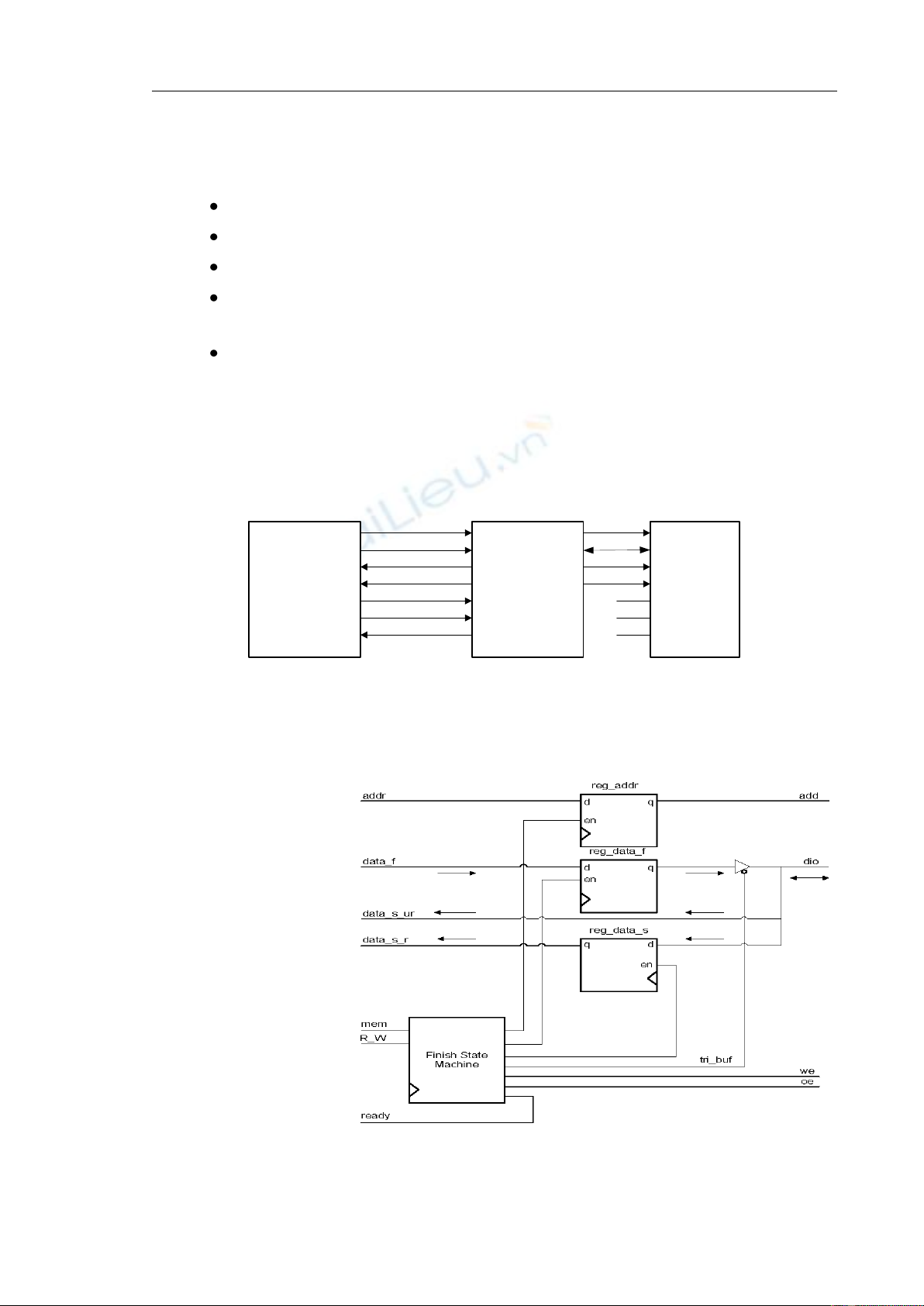

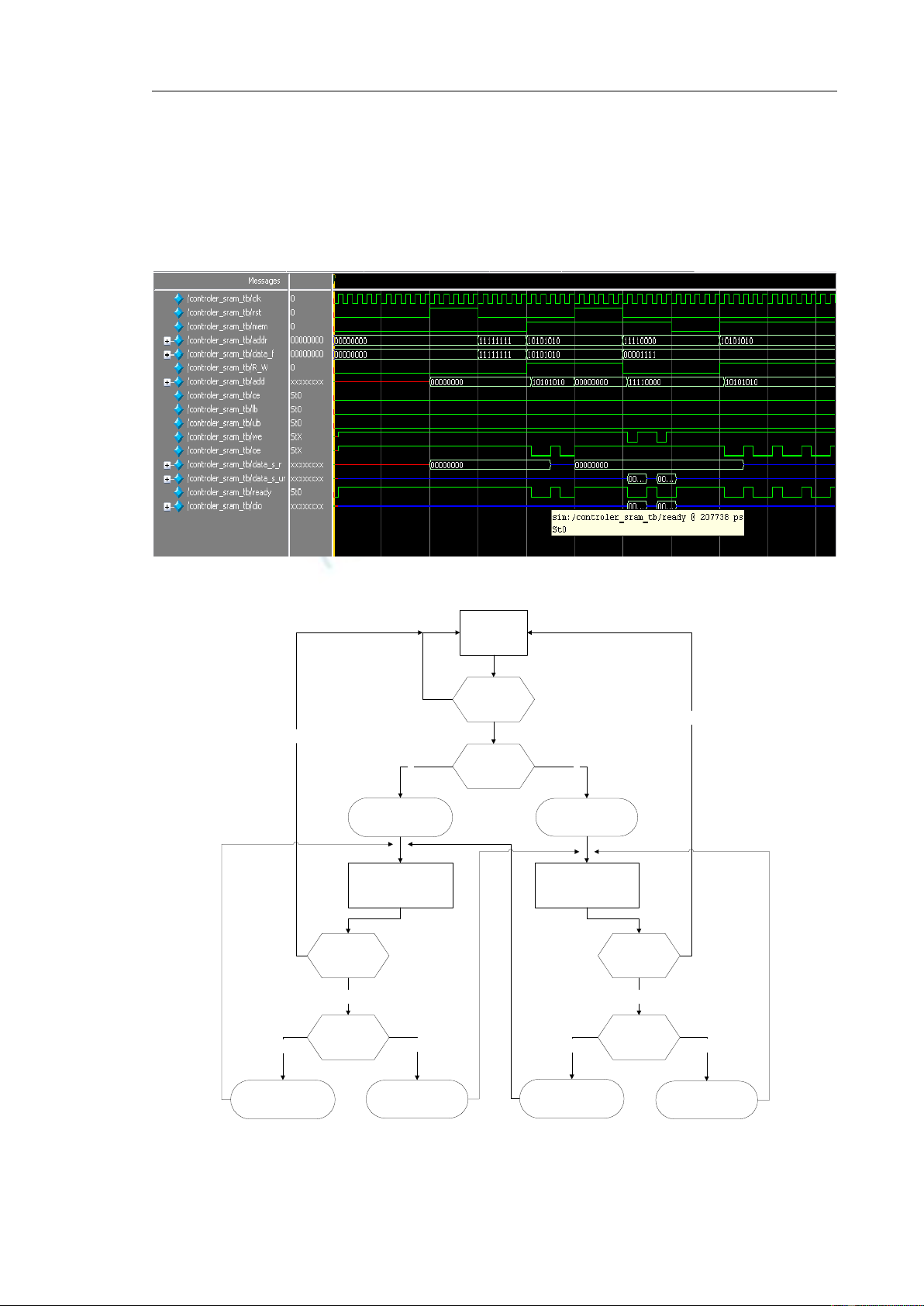

4. Xây dựng chương trình và kiểm tra mô phỏng

4.1. Xây dựng chương trình dựa trên lưu đồ thuật toán

Trong đề tài này,bản thiết kế bộ điều khiển SRAM được xây dựng theo lưu đồ thuật

toán như trong hình 4. Chúng ta có thể khái quát các công đoạn đọc và viết dữ liệu vào

SRAM như sau:

Công đoạn ghi (viết) dữ liệu lên SRAM

Ngắt kích hoạt tín hiệu tại chân oe trong suốt quá trình thực hiện.

Đặt địa chỉ lên đường bus addr, và dữ liệu lên bus dio.

Kích hoạt tín hiệu tại chân we, tín hiệu này phải thực hiện đồng bộ với công

việc đặt địa chỉ và dữ liệu lên các bus.

Đợi ít nhất khoảng thời gian tpwe để xác nhận tín hiệu we được giữ ở mức

thấp.

Ngắt kích hoạt tín hiệu we,dữ liệu lúc này sẽ được chốt lên sram tại mức

chuyển sườn của tín hiệu we.

Tháo bỏ dữ liệu ra khỏi bus dio.

Công đoạn đọc dữ liệu từ SRAM.

Ngắt kích hoạt tín hiệu we trong quá trính thực hiện.

Đặt địa chỉ lên đường bus addr,và kích hoạt tín hiệu oe

Đợi ít nhất khoảng thời gian TAA cho dữ liệu từ SRAM trở nên có giá trị.

Ngắt kích hoạt tín hiệu oe,dữ liệu đọc ra từ bus dio.

Ready=1

Mem==1

R_W==1

reg_addr <-addr reg_addr <-addr

reg_data_f <- data_f

oe=0

oe= 0

reg_data_s=dio

we= 0

tri_buf=0

tri_buf=0

T F

Rd 1

Rd 2 Wr 2

Wr 1

Hình4. Lưu đồ thuật toán bộ điều khiển SRAM (SRAM Controler)

Tuyển tập Báo cáo Hội nghị Sinh viên Nghiên cứu Khoa học lần thứ 7 Đại học Đà Nẵng năm 2010

565

Các khoảng thời gian TAA (address access time),và TPWE (we pulse width time)

thực tế được tra trong datasheet của SRAM IS61LV25616AL.

4.2. Kết quả chạy mô phỏng

Sử dụng phần mềm Model Sim V6.4 để chạy mô phỏng bộ điều khiển,dựa trên

chương trình testbench được viết bằng cách điều khiển từng công đoạn một tại các thời

điểm làm việc khác nhau của SRAM.

Hình 5. Kết quả chạy mô phỏng trên phần mềm ModelSim.

Ready=1

Mem==1

R_W==1

reg_addr <-addr reg_addr <-addr

reg_data_f <- data_f

oe=0 we= 0

tri_buf=0

T F

Rd 1 Wr 1

idle

Mem==1 Mem==1

R_W==1 R_W==1

reg_addr <-addr reg_addr <-addr

reg_addr <-addr

reg_data_f <- data_f reg_addr <-addr

reg_data_f <- data_f

T

TF

T

TF

F

F

Hình 6. Lưu đồ thuật toán phương án thiết kế tối ưu.

Tuyển tập Báo cáo Hội nghị Sinh viên Nghiên cứu Khoa học lần thứ 7 Đại học Đà Nẵng năm 2010

566

5. Kết luận

Với bản thiết kế bộ điều khiển SRAM này,chúng em đã định hướng thiết kế theo

một giới hạn an toàn về thời gian truy cập và điều khiển so với các thông số chuẩn của nhà

sản xuất đưa ra. Điều này tuy đảm bảo cho bộ điều khiển hoạt động đúng theo yêu

cầu,nhưng mặt khác đã ảnh hưởng đến tính tối ưu của bản thiết kế nếu xét trên mặt sản

xuất công nghiệp. Để giải quyết nhược điểm này,chúng em xin đưa ra phương án thiết kế

thứ hai. Cụ thể là sẽ loại bỏ trạng thái thứ hai (Rd2 và Wr2 ) ở cả hai công đoạn đọc hoặc

viết ,đồng thời cho phép thực hiện công đoạn quay đầu mà không cần quay trở ngược về

lại trạng thái Idle ban đầu. Như vậy,ở bộ điều khiển này sẽ tiêu tốn một chu kì clock để

thực hiện một công đoạn bộ nhớ và hai clock cho công đoạn quay đầu, ít hơn so với bản

thiết kế ban đầu.

TÀI LIỆU THAM KHẢO

[1] Xilinx Ltd (2006),Spartan-3 Starter Kit Board User Guide UG230.

[2] Integrated Silicon Solution (2006) Inc,Datasheet SRAM IS61LV25616AL.

[3] Bob Zeidman,”Introduction to CPLD and FPGA Design”

![Ứng dụng máy tính nhúng trong công nghiệp: [Thêm từ mô tả/định tính để tăng CTR]](https://cdn.tailieu.vn/images/document/thumbnail/2013/20130701/lilinz/135x160/7511372680963.jpg)

![Chíp xử lý, điều khiển nhúng: Cấu trúc và Phân loại [A-Z]](https://cdn.tailieu.vn/images/document/thumbnail/2013/20130621/nhungmuadauyeu123/135x160/1631371801545.jpg)

![Chíp xử lý, điều khiển nhúng: [Thông tin chi tiết/ Kinh nghiệm chọn mua/ Ứng dụng mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2013/20130621/nhungmuadauyeu123/135x160/9761371800775.jpg)