KỸ THUẬT SỐ

Biên soạn: Võ Duy Công

Trung tâm Đào tạo Bảo dưỡng Công nghiệp

Đại học Bách khoa TpHCM

Email: congvd@hcmut.edu.vn

1

MẠCH TUẦN TỰ

2

I. Flip-Flop

Flip-Flop: trạng thái kế tiếp của ngõ ra FF sẽ thay đổi theo ngõ vào và trạng thái

trước đó của ngõ ra khi sự thay đổi của xung clock (cạnh lên hoặc cạnh xuống).

Mạch tuần tự

3

Bảng đặc tính và phương trình đặc tính:

Biểu diễn quan hệ của ngõ ra kế tiếp Q+phụ thuộc vào ngõ và và trạng thái

ngõ ra hiện tại Q.

Bảng kích thích

Biểu diễn giá trị các ngõ vào cần phải có khi ngõ ra chuyển từ trạng thái

hiện tại Q sang trạng thái kế tiếp Q+.

I. Flip-Flop

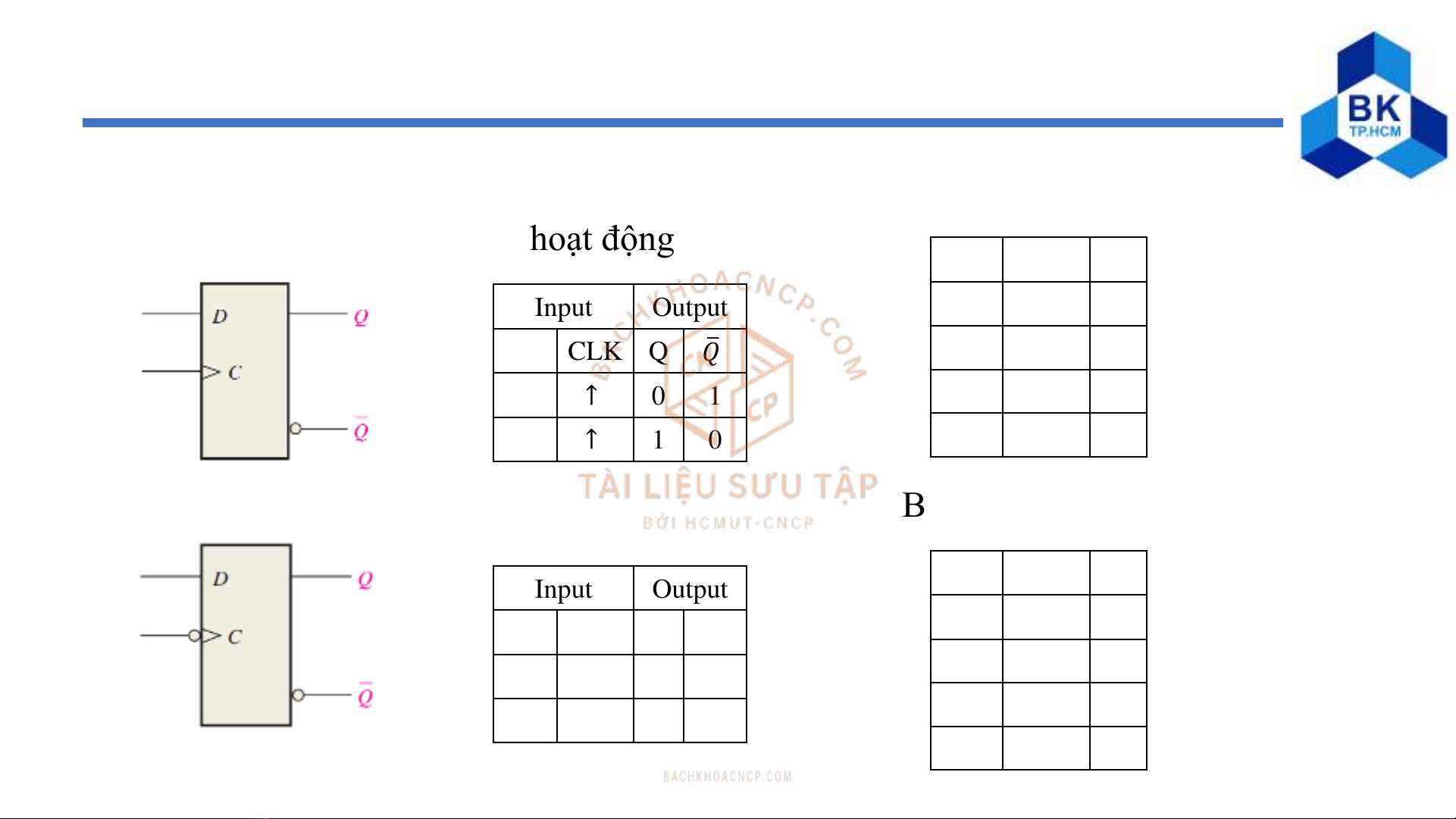

D Flip-Flop

Mạch tuần tự

4

Input Output

D

CLK

Q

ത

𝑄

0↑0 1

1↑1 0

Input Output

D

CLK

Q

ത

𝑄

0↓0 1

1↓1 0

Bảng hoạt động D Q

Q

+

000

010

1 0 1

1 1 1

Bảng kích thích

Bảng đặc tính

Q Q+D

000

011

1 0 0

1 1 1

Q+= D

D = Q+

Hàm đặc tính

Hàm kích thích

I. Flip-Flop

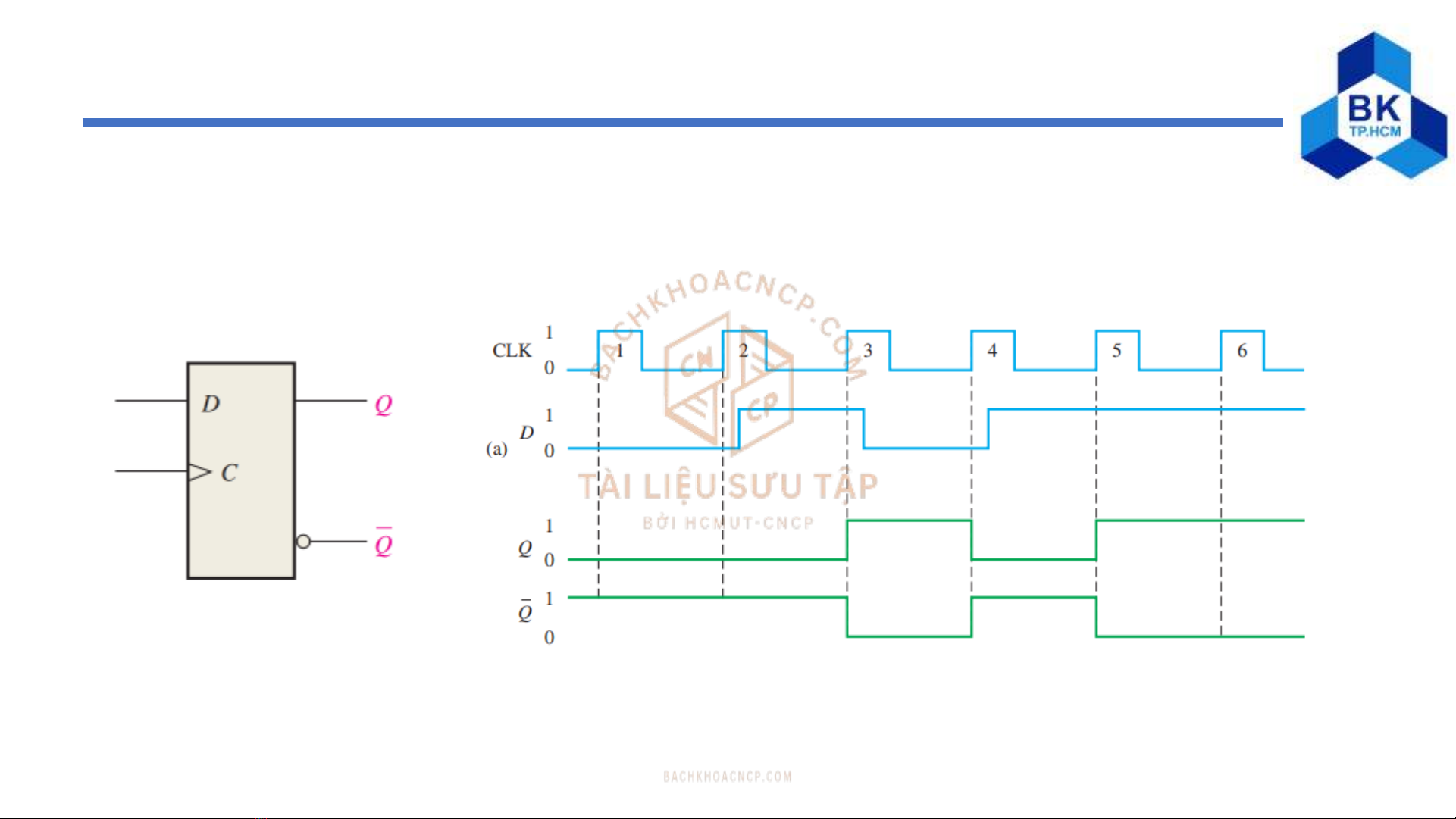

D Flip-Flop

Mạch tuần tự

5

![Trắc nghiệm Mạch điện: Tổng hợp câu hỏi và bài tập [năm hiện tại]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251118/trungkiendt9/135x160/61371763448593.jpg)