ME3081: Mechatronic System Design

2

Lecturer: PhD. Dang Thai Viet

Mechatronics Department, School of Mechanical Engineering, HUST

Viet.dangthai@hust.edu.vn

Chương 9. Điều khiển logic

3

Mục 2. Biểu diễn hàm logic

Mục 3. Mô hình hệ thống điều khiển số

Mục 4. Biến đổi z

Mục 1. Biến và hàm logic

ME3081: Mechatronic System Design

4

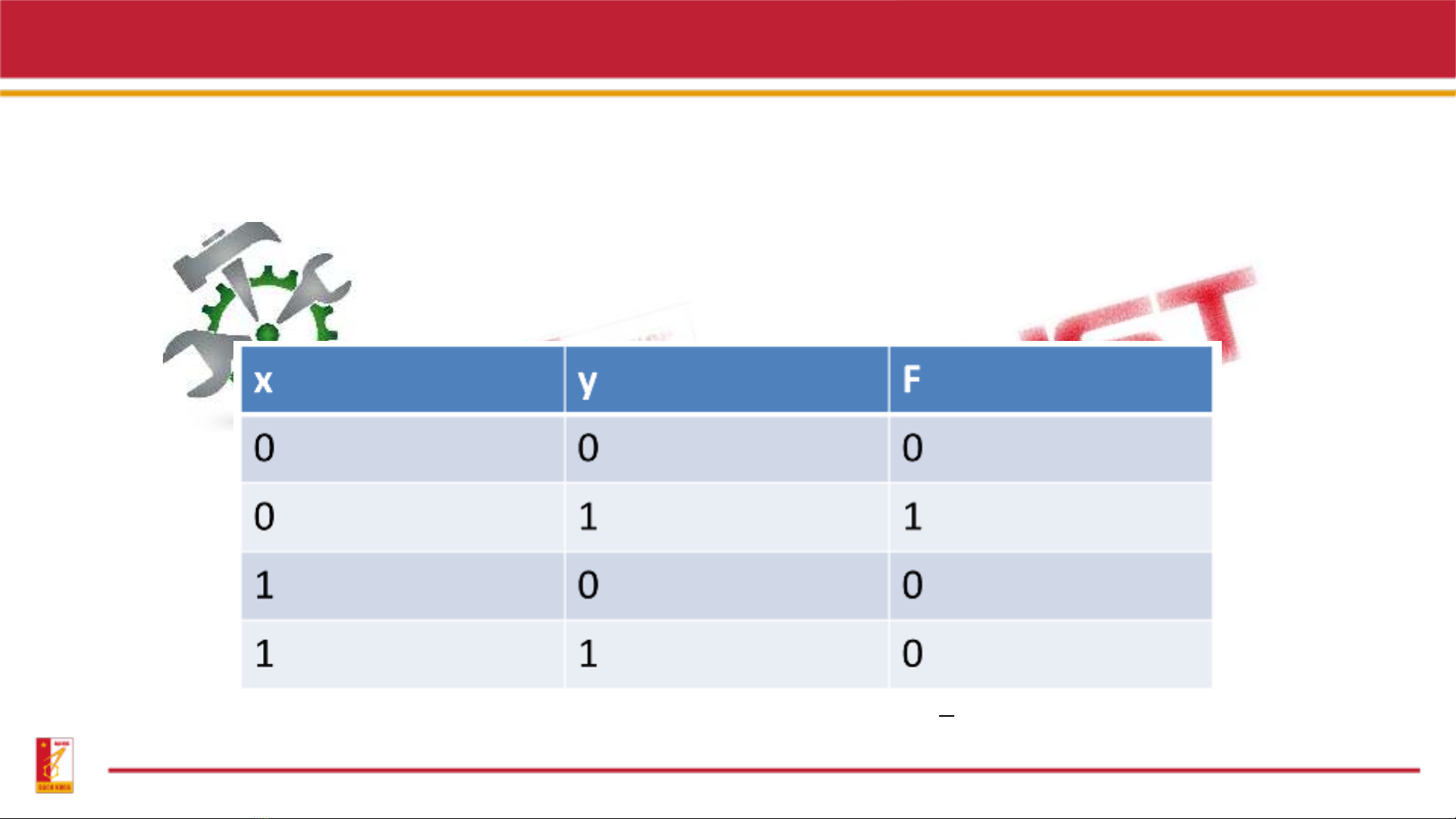

•Biến logic là hai giá trị đối lập nhau 0 và 1.Có thể được chuyển đổi từ trạng thái tương tự là mức

cao và mức thấp.

9.1. Biến và hàm logic (1)

•Hàm logic thực hiện các phép toán logic của các biến logic biểu diễn quan hệ vào ra hệ thống.Biểu

diễn qua bảng chân lý.

Hình 9.1. Bảng chân lý biểu diễn quan hệ logic

.F x y=

5

•Thông qua hàm toán logic:

❑Biểu diễn quan hệ logic

.F x y=

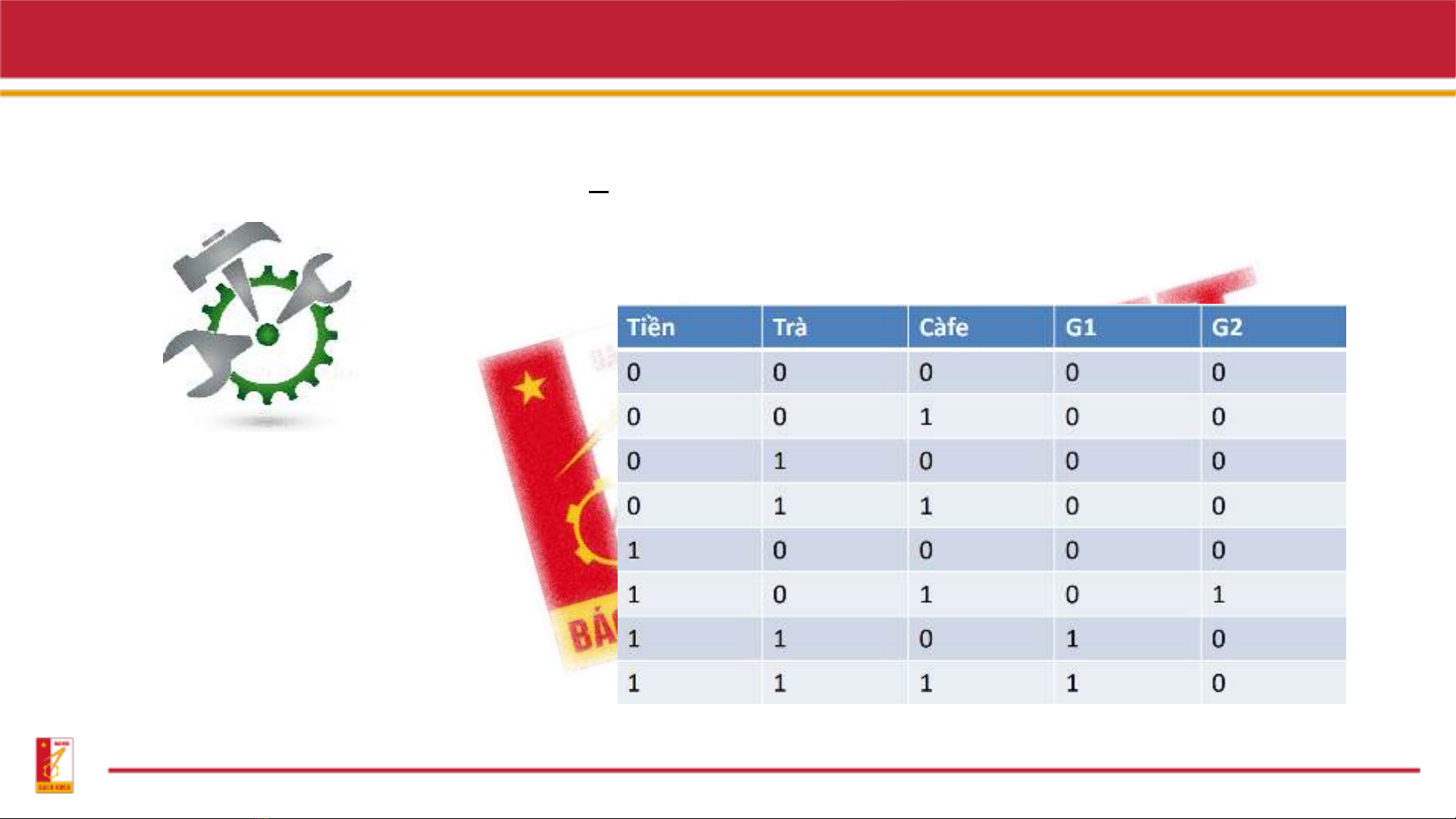

•Thông qua bảng chân lý.Bảng Karnaugh cho nhiều biến logic.

➢Ví dụ:

•Máy bán nước tự động gồm 2loại

trà và cà phê. Có các nút ấn chọn

trà, chọn cà phê và nếu ấn cả hai

nút thì chỉ ra trà. Máy chỉ hoạt

động khi có đồng xu 5000 thả vô

máy.

Hình 9.2. Bảng chân lý biểu diễn giá trị logic

9.1. Biến và hàm logic (2)