Baøi giaûng Vi maïch

CH NG 5ƯƠ

GIAO TI P GI A CMOS & TTLẾ Ữ

5.1 GIAO TI P GI A CÁC C NG LOGIC V I NHAUẾ Ữ Ổ Ớ

5.1.1 Gi a TTL v i TTLữ ớ

Do cùng lo i nên chúng đ ng nhiên có th m c n i tr c ti p v i nhau.ạ ươ ể ắ ố ự ế ớ

Dòng trung bình đ đ m b o m c đi n áp vào, ra m c cao hay th p cho phép thì:ể ả ả ứ ệ ở ứ ấ

IOH = 400uA còn IIH = 40uA khi ra m c cao.ứ

IOL = 16mA còn IIL = 16mA khi ra m c th p.ứ ấ

Nh v y 1 c ng TTL có th thúc đ c kho ng d i 10 c ng logic cùngư ậ ổ ể ượ ả ướ ổ

lo i. đây ch xét tính t ng đ i do TTL có nhi u lo i nên kh năng thúc t i (tínhạ Ở ỉ ươ ố ề ạ ả ả

s to ra) cũng khác nhau nh lo i ALS có th thúc đ c t i 20 c ng 74ALS khác.ố ả ư ạ ể ượ ớ ổ

Đ bi t chính xác h n có th d a vào thông s c a dòng vào và ra c a IC trong sể ế ơ ể ự ố ủ ủ ố

tay tra c u IC đ tính toán.ứ ể

5.1.2 Gi a TTL v i CMOS h 74HC, 74HCTữ ớ ọ

m c th p TTL có th thúc đ c CMOS do VỞ ứ ấ ể ượ OLmax(TTL)< VILmax(CMOS)

và IOLmax(TTL) > IILmax(CMOS).

m c cao TTL không th thúc đ c CMOS do áp m c cao c a TTL có khiỞ ứ ể ượ ứ ủ

ch còn 2,5 V trong khi CMOS ch ch p nh n áp m c cao không d i 3,5V. n uỉ ỉ ấ ậ ứ ướ ế

n i m ch thì ho t đ ng có th sai logic.ố ạ ạ ộ ể

Có 1 cách đ kh c ph c là dùng đi n tr kéo lên ngõ ra c a c ng TTL. Khiể ắ ụ ệ ở ở ủ ổ

đó, qua đi n tr R này, dòng t ngu n s nâng dòng vào CMOS nh đó áp ra m cệ ở ừ ồ ẽ ờ ứ

cao TTL s không quá th p, CMOS s hi u đ c.ẽ ấ ẽ ể ượ

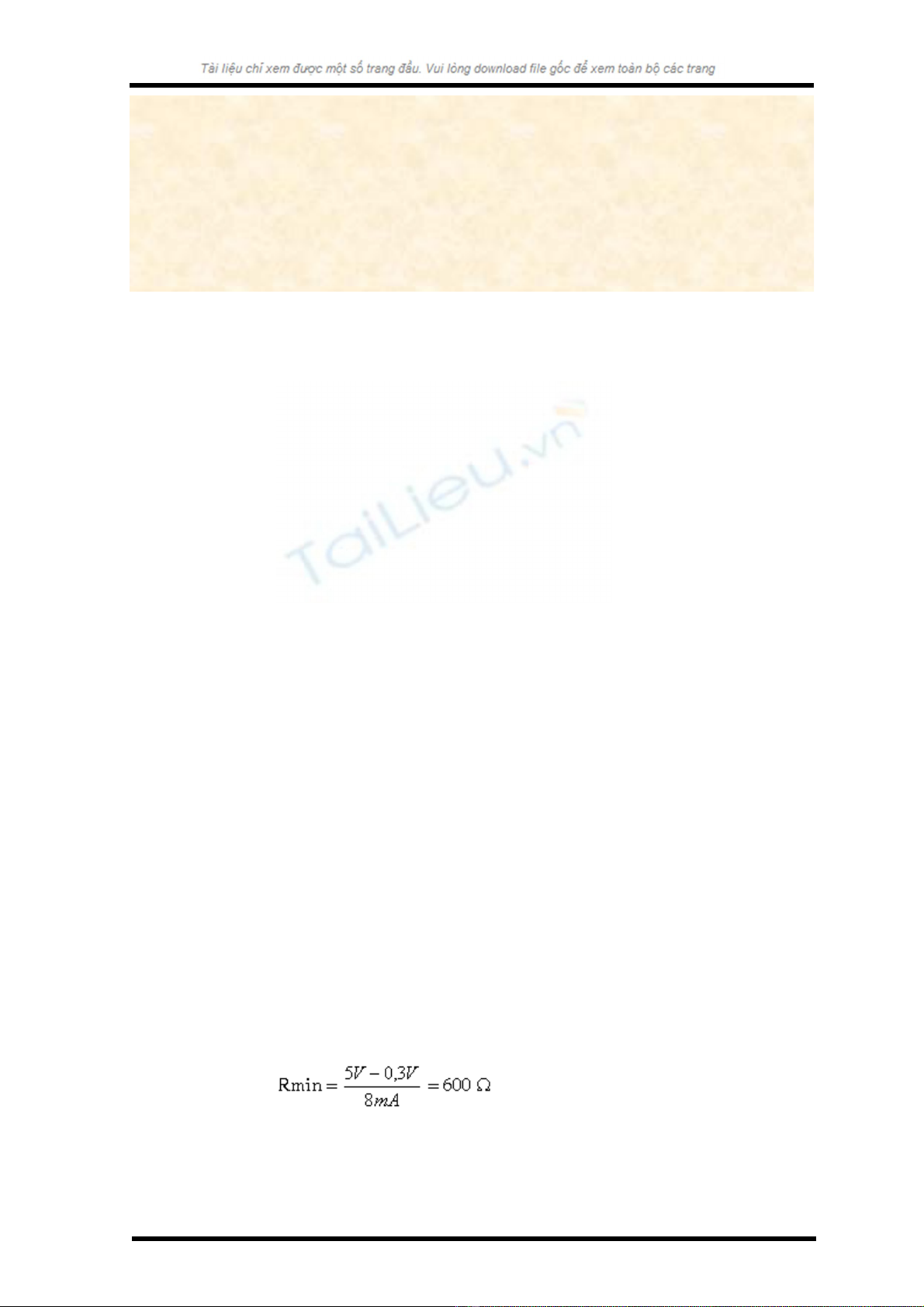

Ch ng h n m t c ng 74LS01 có Iẳ ạ ộ ổ OLmax = 8mA, VOLmax = 0,3V thúc m tộ

c ng 74HC00 có VổIHmin = 3,5V, IIHmin = 1uA.

Khi 74LS01 m c th p 0,3V thì nó s nh n dòng h t m c là 8mA đ c c pở ứ ấ ẽ ậ ế ứ ượ ấ

thông qua đi n tr kéo lên (trong khi dòng Iệ ở IHmin ch có d i 1uA r t nh ), th thìỉ ướ ấ ỏ ế

s ph i c n đi n tr kéo lên có giá tr nh nh t Rẽ ả ầ ệ ở ị ỏ ấ min.

Còn khi m c cao 3,5V 74LS01 nh n dòng 100uA và 74HC00 nh n dòngở ứ ậ ậ

1uA. V y khi này đi n tr kéo lên s ph i có giá tr max đ h n l i dòng cho 2ậ ệ ở ẽ ả ị ể ạ ạ

c ngổ

Chöông 5: Giao tieáp giöõa TTL vaø CMOS

71

Baøi giaûng Vi maïch

Khi Rmax thì công su t tiêu tán max s nh nh t.ấ ẽ ỏ ấ

T C = 15pF đ c thêm vào đ khi đang m c th p 0,3V mà chuy n lênụ ượ ể ở ứ ấ ể

m c cao thì t s n p cho áp lên 3,5V đ CMOS “hi u”.ứ ụ ẽ ạ ể ể

Hình 5.1 Giao ti p gi a TTL v i CMOSế ữ ớ

5.1.3 TTL thúc CMOS có áp ngu n cao h n 5Vồ ơ

Cũng gi ng nh tr ng h p trên, n u ra m c th p thì TTL có th thúc tr cố ư ở ườ ợ ế ứ ấ ể ự

ti p CMOS nh ng n u ra m c cao Vế ư ế ứ OH(TTL) ch có 2,7V đ n 5V thì ch c ch nỉ ế ắ ắ

không th thúc đ c CMOS vì kho ng áp này r i vào vùng b t đ nh c a ngõ vàoể ượ ả ơ ấ ị ủ

CMOS. Ta cũng ph i dùng đi n tr kéo lên, có th dùng TTL ngõ ra c c thu đ hả ệ ở ể ự ể ở

cho tr ng h p này.ườ ợ

5.1.4 Giao ti p CMOS-CMOSế

V i cùng đi n th c p, m t c ng CMOS có th thúc cho r t nhi u c ng cùngớ ệ ế ấ ộ ổ ể ấ ề ổ

lo i CMOS vì dòng c p kho ng 0,5 đ n 5mA trong khi dòng nh n r t nh (d iạ ấ ả ế ậ ấ ỏ ướ

1uA).

Tuy nhiên n u t n s ho t đ ng càng cao thì kh năng thúc t i s càng gi mế ầ ố ạ ộ ả ả ẽ ả

đi (có khi ch còn d i 10 c ng). Lý do là t n s cao, các đi n dung ngõ vào c aỉ ướ ổ ở ầ ố ệ ủ

các c ng t i s làm tăng công su t tiêu tán và trì hoãn truy n c a m ch.ổ ả ẽ ấ ề ủ ạ

5.1.5 CMOS thúc TTL

Khi thúc t i m c cao th ng Vả ở ứ ườ OH(CMOS) > VIH(TTL) còn dòng nh nậ

IIH(TTL) ch vài ch c uA nên CMOS có th thúc nhi u t i TTL.ỉ ụ ể ề ả

Khi thúc TTL m c th p thì r t ph c t p tuỳ lo i.ở ứ ấ ấ ứ ạ ạ

CMOS cũ (4000) không thúc đ c TTL.ượ

CMOS m i (74HC) thì có th , s c ng thúc đ c tuỳ thu c VOL(CMOS) >ớ ể ố ổ ượ ộ

VIL(TTL) và dòng t ng ngõ ra (CMOS) ph i l n h n t ng các dòng ngõ vào Iổ ả ớ ơ ổ IL c aủ

các t i TTL.ả

Nh v y, vi c giao ti p các c ng v i nhau cũng r t đa d ng tuỳ thu c yêuư ậ ệ ế ổ ớ ấ ạ ộ

c u ng i s d ng. M t v n đ khác cũng c n ph i quan tâm là các IC giao ti pầ ườ ử ụ ộ ấ ề ầ ả ế

nhau chung ngu n c p hay giao ti p cùng kho ng m c áp s đ m b o ho t đ ngồ ấ ế ả ứ ẽ ả ả ạ ộ

Chöông 5: Giao tieáp giöõa TTL vaø CMOS

72

Baøi giaûng Vi maïch

h n. Vì v y có m t s IC đã đ c s n xu t đ ph c v cho vi c chuy n m cơ ậ ộ ố ượ ả ấ ể ụ ụ ệ ể ứ

đi n áp giao ti p gi a CMOS v i TTL hay CMOS 4000 v i CMOS 74HC.ệ ế ữ ớ ớ

5.2 GIAO TI P GI A C NG LOGIC V I CÁC THI T B ĐI NẾ Ữ Ổ Ớ Ế Ị Ệ

5.2.1 Giao ti p v i công t c c khí ế ớ ắ ơ

Các công t c th ng s d ng đ đóng m ngu n c p t o tr ng thái logicắ ườ ử ụ ể ở ồ ấ ạ ạ

cho c ng nh ng do làm d ng ti p xúc c khí nên khi đóng mổ ư ạ ế ơ ở s sinh ra hi nẽ ệ

t ng d i.ượ ộ

Hình 5.2 Giao ti p v i công t c c khíế ớ ắ ơ

V i đi n gia d ng nh đèn qu t thì hi n t ng d i này không nh h ng gìớ ệ ụ ư ạ ệ ượ ộ ả ưở

c vì d i x y ra r t ng n ch kho ng vài ms, đèn qu t không k p sáng t t hay quayả ộ ả ấ ắ ỉ ả ạ ị ắ

d ng ho c n u có đi thì m t cũng không th th y đ c. Nh ng v i các vi m chừ ặ ế ắ ể ấ ượ ư ớ ạ

đi n t , r t nh y v i nh ng thay đ i r t nh và r t nhanh. ệ ử ấ ạ ớ ữ ổ ấ ỏ ấ

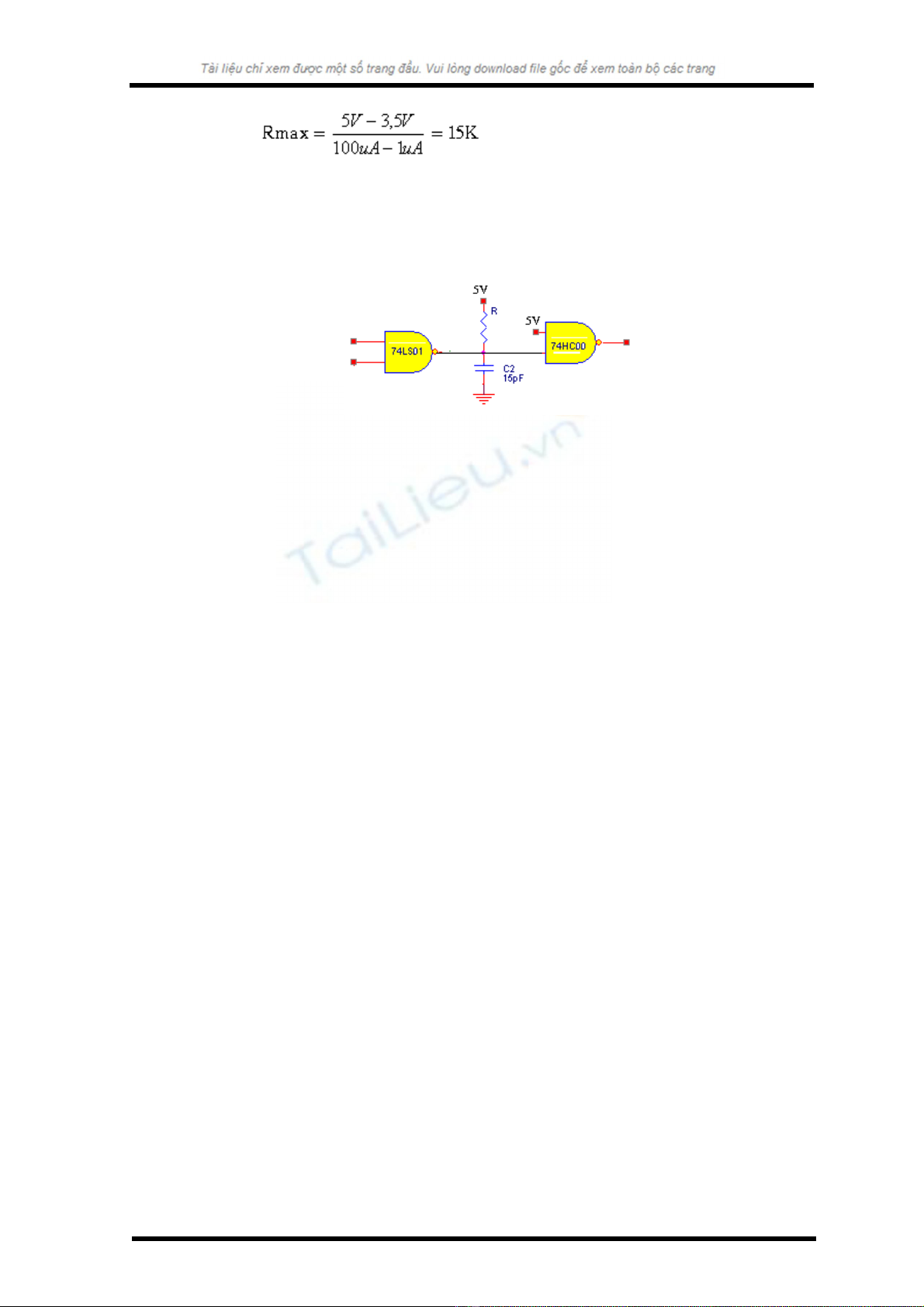

đây dùng c ng schmitt trigger CMOS đ chuy n m ch tín hi u t o b iỞ ổ ể ể ạ ệ ạ ở

công t c. Do khi nh n công t c, gây ra d i, công t c chuy n qua l i gi a mass vàắ ấ ắ ộ ắ ể ạ ữ

Vcc đ a vào c ng logic, Schmitt trigger r t nh y khi áp vào l n h n hay nh h nư ổ ấ ạ ớ ơ ỏ ơ

áp ng ng c a nó thì l p t c áp ra s là m c cao hay m c th p, m c này cung c pưỡ ủ ậ ứ ẽ ứ ứ ấ ứ ấ

cho m ch đ m và m ch hi n th n u đ c n i t m ch đ m s cho s đ m là sạ ế ạ ể ị ế ượ ố ừ ạ ế ẽ ố ế ố

l n d i công t c.ầ ộ ở ắ

Hi n t ng này ch x y ra vài ch c ms nh ng v i m ch logic đôi khi cũng làệ ượ ỉ ả ụ ư ớ ạ

“nguy hi m” r i. Đ ch ng d i ta có th s d ng ph n c ng hay ph n m m.ể ồ ể ố ộ ể ử ụ ầ ứ ầ ề

Ch ng h n bàn phím máy tính đ u là các công t c c khí, 1 ph n m m trongẳ ạ ở ề ắ ơ ầ ề

máy s dò đ c công t c đó chuy n ti p trong m t kho ng th i gian ng n kho ngẽ ọ ắ ể ế ộ ả ờ ắ ả

20ms, n u th c s công t c đ c nh n thì m c logic m i n n đ nh sau kho ngế ự ự ắ ượ ấ ứ ớ ấ ổ ị ả

th i gian d i y và ph n m m m i ch p nh n đ c tr ng thái c a công t c. Cònờ ộ ấ ầ ề ớ ấ ậ ượ ạ ủ ắ

đây trình bày cách ch ng d i b ng t và m ch ch t.ở ố ộ ằ ụ ạ ố

Ch ng d i dùng t l c đ u vàoố ộ ụ ọ ầ

T C giá tr kho ng 0,01us đ c n i ngõ vào c a c ng logic nh hình v .ụ ị ả ượ ố ở ủ ổ ư ẽ

Khi nh n công t c, t C n p qua công t c vào t . T i khi công t c nh ra, có hi nấ ắ ụ ạ ắ ụ ớ ắ ả ệ

t ng d i t s x qua R xu ng mass. Th i h ng x là 100k x 0,01uF = 1ms l nượ ộ ụ ẽ ả ố ờ ằ ả ớ

h n chu kì d i t i đa c a công t c ch vài trăm ns. Do đó khi này c ng logic ch aơ ộ ố ủ ắ ỉ ổ ư

Chöông 5: Giao tieáp giöõa TTL vaø CMOS

73

Baøi giaûng Vi maïch

chuy n m ch, t i khi áp x trên t gi m xu ng t i d i m c ng ng c a c ngể ạ ớ ả ụ ả ố ớ ướ ứ ưỡ ủ ổ

logic thì tr ng thái logic ngõ ra m i l t l i (hình 5.3).ạ ớ ậ ạ

Hình 5.3 Cách ch ng d i dùng t l cố ộ ụ ọ

C ng logic NOT đ c dùng có th là lo i TTL th ng hay Schitt trigger.ổ ượ ể ạ ườ

Ch ng d i dùng m ch ch tố ộ ạ ố

M ch ch t c b n dùng 2 c ng nand m i c ng 2 ngõ vào có h i ti p chéoạ ố ơ ả ổ ỗ ổ ồ ế

đ c k t h p v i 2 đi n tr kéo lên m c ngõ vào đ t o thành m ch ch ng d iượ ế ợ ớ ệ ở ắ ở ể ạ ạ ố ộ

t công t c.ừ ắ

Khi công t c b t lên v trí 1 (nh hình ắ ậ ị ư 5.4) ngõ vào NAND1 m c 0 do đóở ứ

ngõ ra Q' = 1.

Hình 5.4 Cách ch ng d i dùng m ch ch tố ộ ạ ố

Q' = 1 đ a v ngõ vào NAND2, đ ng th i ngõ vào còn l i m c 1 đó n i quaư ề ồ ờ ạ ở ứ ố

R2 lên Vcc nên ra Q= 0, Q= 0 đ a v ngõ vào nand1 khi này n u d i có x y ra điư ề ế ộ ả

chăng n a làm cho ngõ vào t công t c t 1 xu ng 0 thì do = 0 nên ngõ ra nand1ữ ừ ắ ừ ố

luôn là 1.

Nh v y ch ng t r ng Q và không h b nh h ng b i công t c b d i.ư ậ ứ ỏ ằ ề ị ả ưở ở ắ ị ộ

Tr ng thái c a nó ch chuy n m ch d t khoát m t l n khi công t c đ c nh n quaạ ủ ỉ ể ạ ứ ộ ầ ắ ượ ấ

a và ch l t l i tr ng thái khi công t c đ c nh n qua 2.ỉ ậ ạ ạ ắ ượ ấ

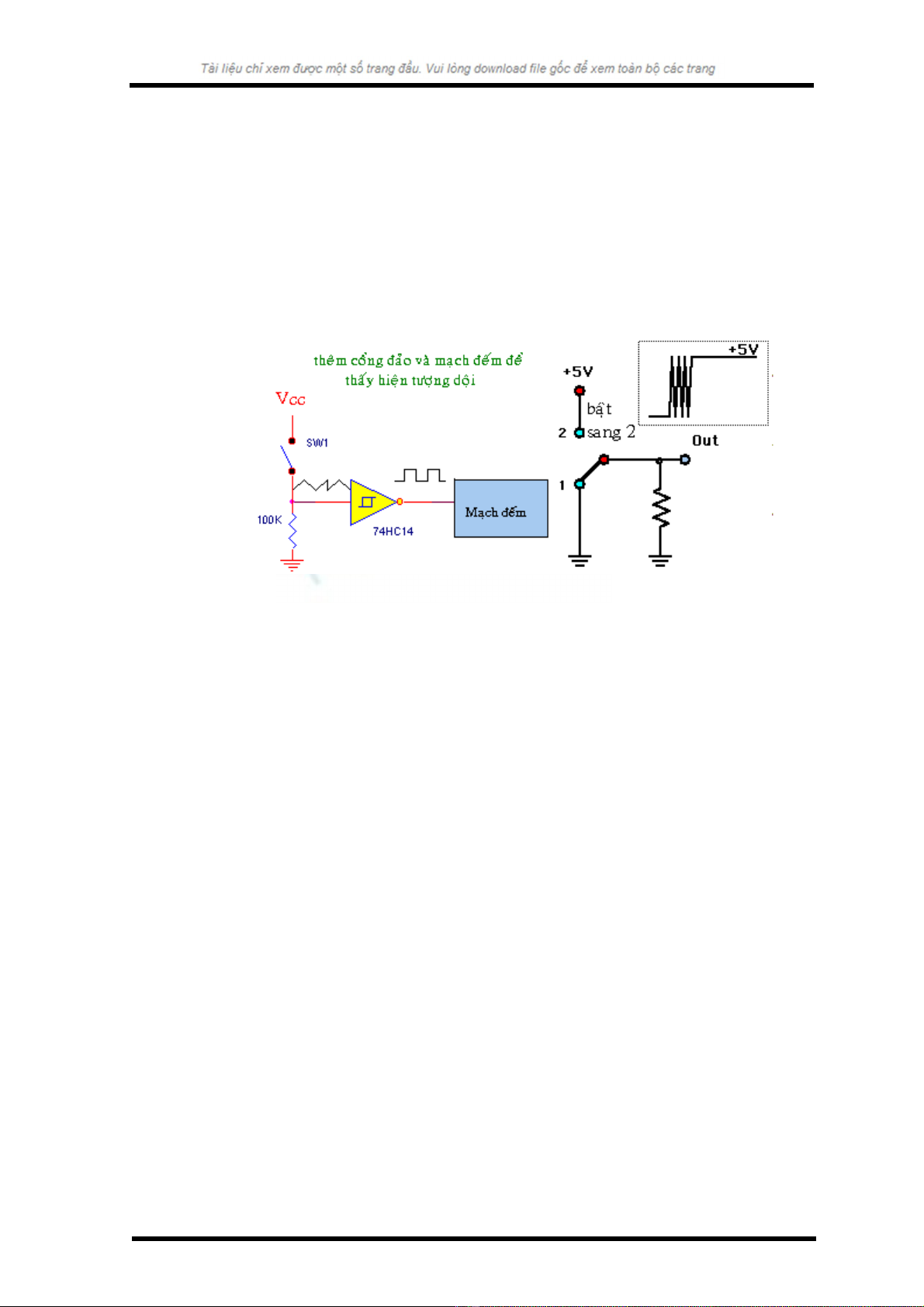

M t d ng khác cũng có th ch ng d i đ c th hi n nh hình 5.5:ộ ạ ể ố ộ ượ ể ệ ư

Chöông 5: Giao tieáp giöõa TTL vaø CMOS

74

Baøi giaûng Vi maïch

Hình 5.5 Ch ng d i dùng c ng NOTố ộ ổ

B t công t c sang mass, ngõ ra I2 m c 0 đ a v qua R ngõ vào I1 nên v nậ ắ ở ứ ư ề ẫ

làm I2 ra 0 cho dù công t c có b d i lên xu ng nhi u l n. Do đó ngõ ra I3 luôn ở ắ ị ộ ố ề ầ ở

m c 1.ứ

Ng c l i nh n công t c qua Vcc, ngõượ ạ ấ ắ ra I2 m c 1 đ a v ngõ vào I1 m c 1ứ ư ề ứ

l i v n làm I2 ra m c 1 b t ch p công t c b d i, k t qu ra I3 luôn m c 0.ạ ẫ ứ ấ ấ ắ ị ộ ế ả ở ứ

C ng logic đ c s d ng trong m ch ch t trên có th là lo i TTL hayổ ượ ử ụ ạ ố ở ể ạ

CMOS th ng hay schmitt trigger đ u đ c c nh c ng NOT 4069, 4040; c ngườ ề ượ ả ư ổ ổ

NAND 7400, 4011, 74132,…

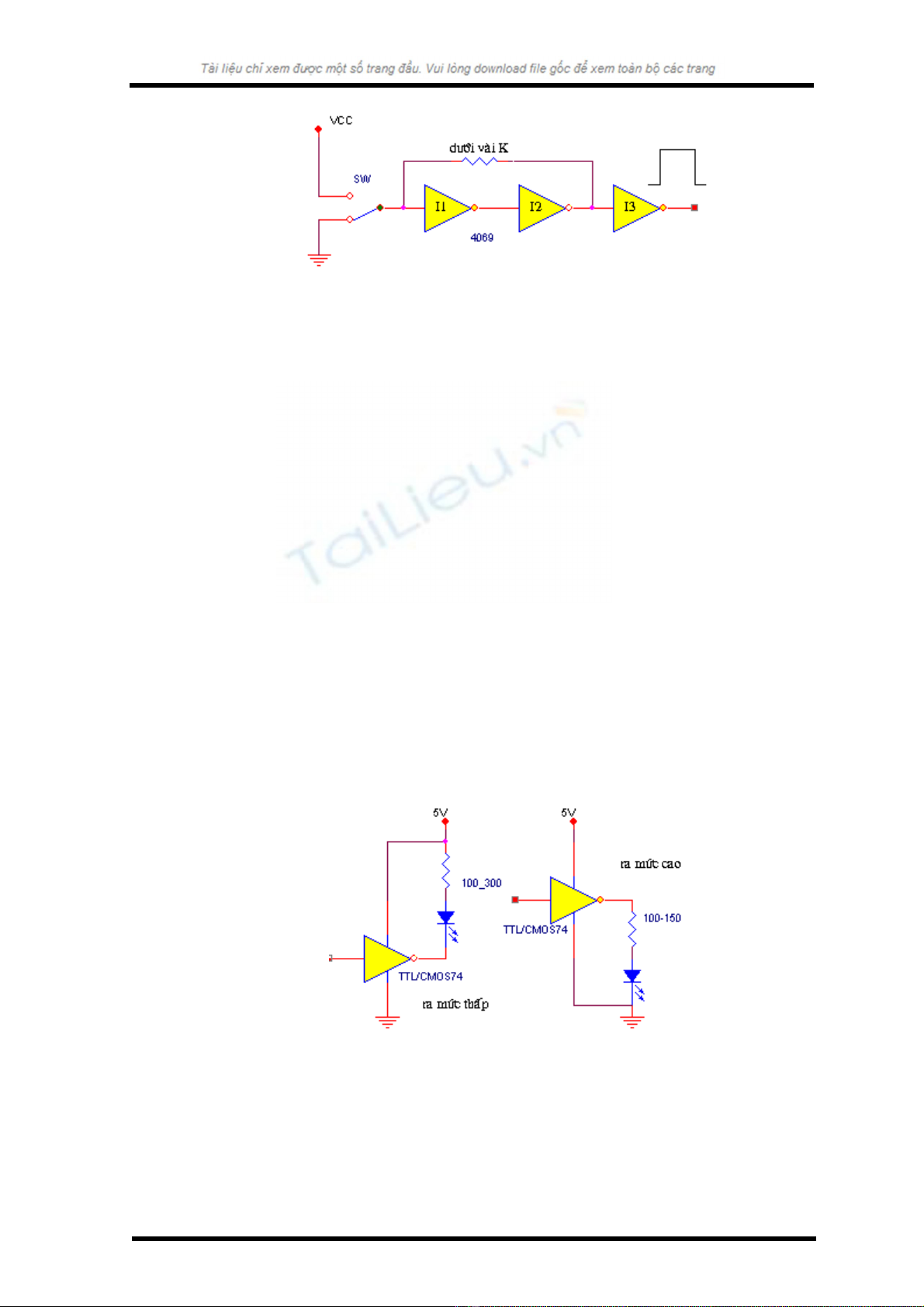

5.2.2 Giao ti p v i t i nh ế ớ ả ỏ

M t s kh năng c a c ng logic khi giao ti p v i các lo i t i khác nhau:ộ ố ả ủ ổ ế ớ ạ ả

Led đ n r t hay đ c s d ng đ hi n th các vi m ch đi n t , áp r i trênơ ấ ượ ử ụ ể ể ị ở ạ ệ ử ơ

nó d i 2V, dòng qua kho ng vài mA do đó nhi u c ng logic lo i TTL và CMOSướ ả ề ổ ạ

74HC/HCT có th thúc tr c ti p led đ n.ể ự ế ơ

Tuy nhiên lo i CMOS 4000, 14000 thì không th do dòng vào ra m c cao vàạ ể ứ

th p đ u r t nh (d i 1uA, và d i 0,5mA) m c dù chúng có th ho t đ ng vàấ ề ấ ỏ ướ ướ ặ ể ạ ộ

cho áp l n h n lo i 2 lo i kia.ớ ơ ạ ạ

M ch giao ti p v i led nh hình 5.6:ạ ế ớ ư

Hình 5.6 Giao ti p v i LEDế ớ

R là đi n tr gi i h n dòng cho led, cũng tuỳ lo i c ng logic đ c s d ngệ ở ớ ạ ạ ổ ượ ử ụ

mà R cũng khác nhau th ng ch n d i 330 Ω (đi n áp Vườ ọ ướ ệ cc = 5VDC) tuỳ theo vi cệ

l a ch n đ sáng c a led.ự ọ ộ ủ

Chöông 5: Giao tieáp giöõa TTL vaø CMOS

75

![Cắt bằng hồ quang điện [Mới Nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2014/20140331/hoangtuxuquang/135x160/7351396310863.jpg)

![MAX232: Mạch DUAL EIA 232 DRIVERS/RECEIVERS [Thông tin chi tiết]](https://cdn.tailieu.vn/images/document/thumbnail/2011/20110611/tanthanh2603/135x160/max232_501.jpg)

![Giáo trình Vận hành hệ thống cung cấp điện (Nghề Quản lý kinh doanh điện, Trình độ Cao đẳng) - Trường Cao đẳng Du lịch và Công thương [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260428/ronaldinho09/135x160/43801777435701.jpg)

![Giáo trình Kỹ thuật điện tử (Nghề: Kỹ thuật lắp ráp sửa chữa và lắp ráp máy tính - Trình độ: Trung cấp) - Trường Cao đẳng Du lịch và Công thương [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260428/ronaldinho09/135x160/98151777435702.jpg)