464

tiên đoán là trong tương lai màn hình TV sẽ được mua một cách riêng lẻ. Các

thiết bị điều khiển như phần vừa được mô tả trên sẽ được cung cấp bởi các nhà

cung cấp nhỏ thứ ba. Vì thế, toàn bộ thị trường mới sẽ được mở và một số việc

465

làm được tăng lên trong lĩnh vực này. Trong tương lai truyền hình sẽ có khả

năng hiện thị menu có khả năng lập trình được.

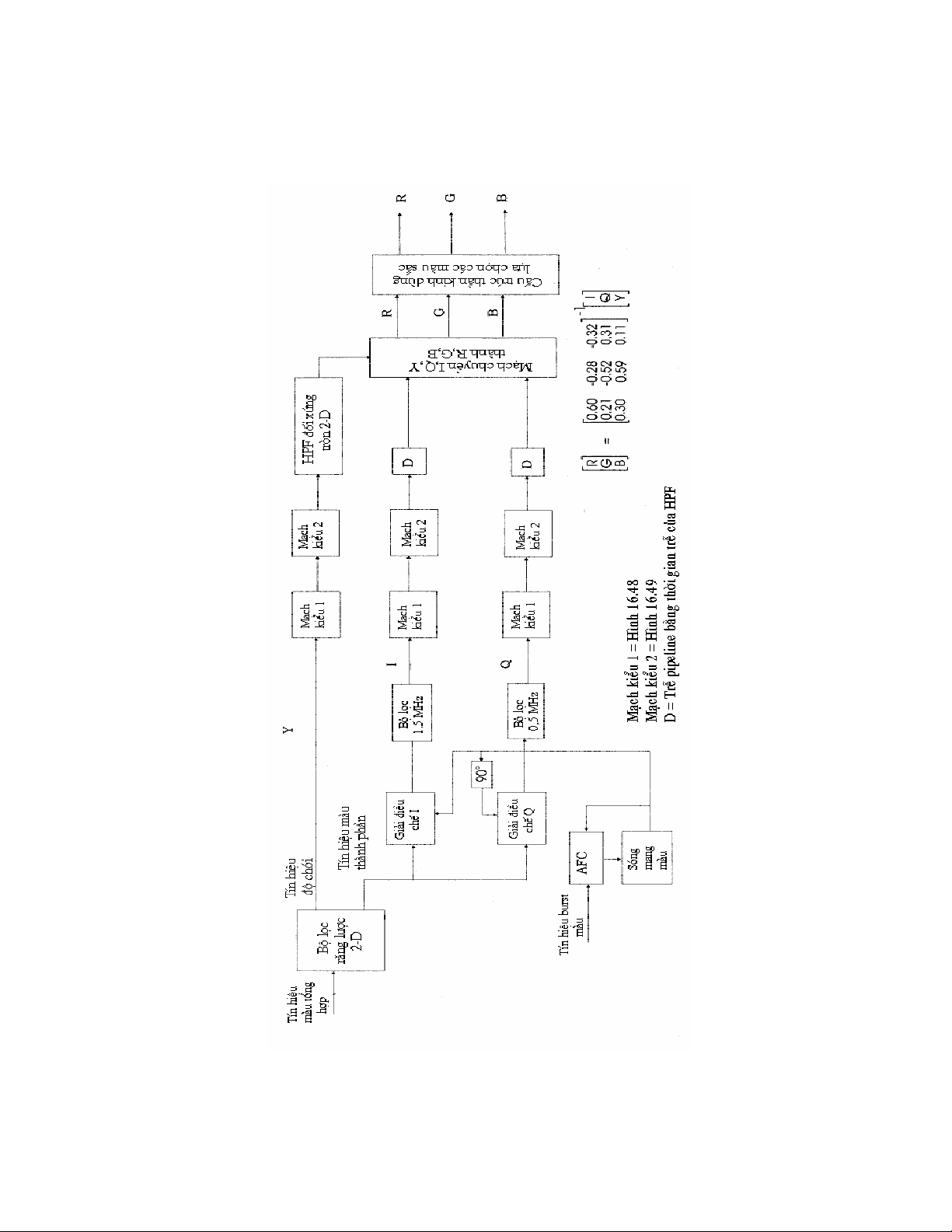

Hình 16.50 Cải tiến hệ NTSC.

466

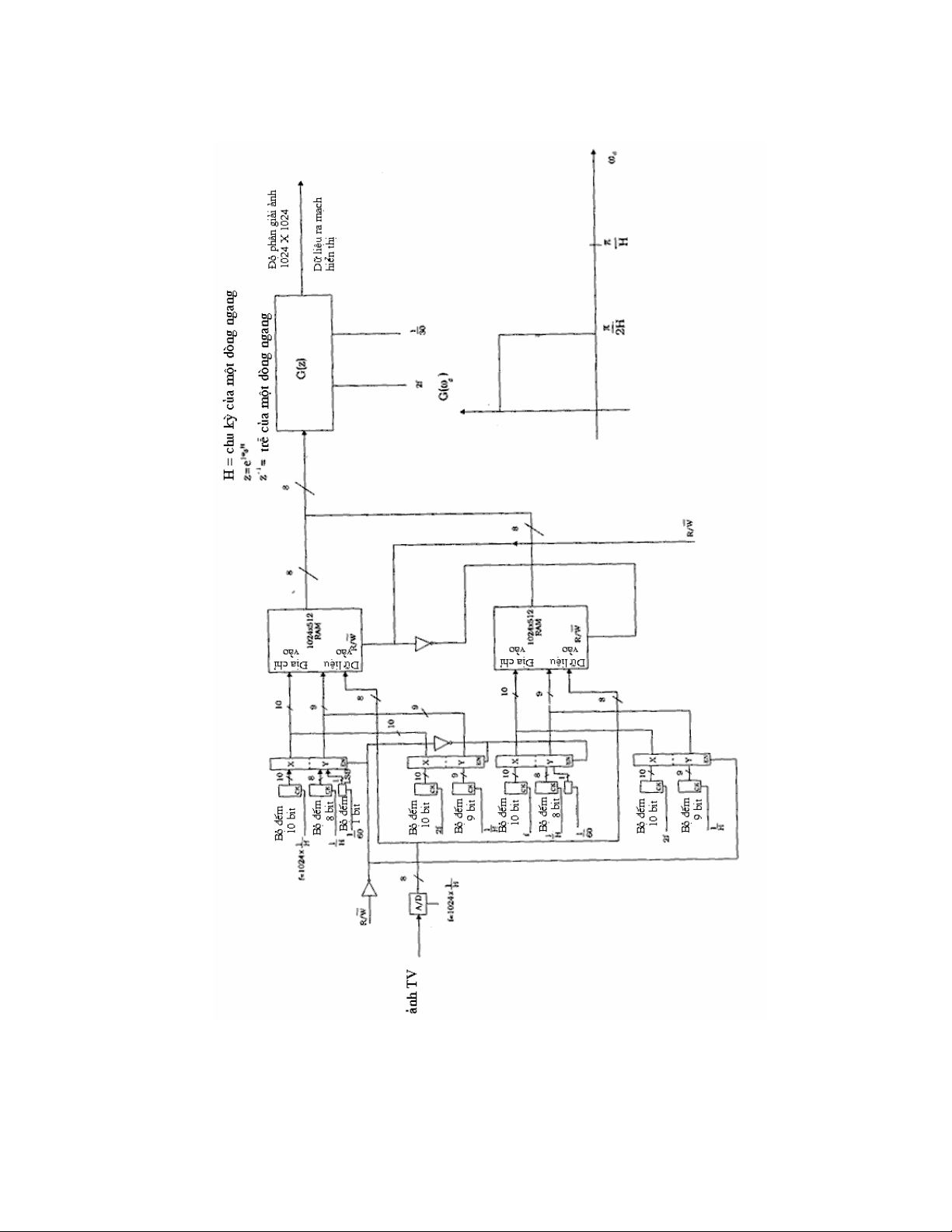

Hình 16.51 Kiến trúc nội suy ảnh thời gian thực sử dụng lấy mẫu nhanh dọc

theo hướng quét ngang và 1-D LPF có đặc tính dọc theo hướng dọc.

467

16.12 Biến đổi ảnh thời gian thực

Có khả năng để phát triển mảng tâm thu tuyến tính mà cần bộ xử lý log2N

đưa ra các biến đổi như 1-D FFT và DCT. Choi và Boriakoff đã phát triển một

hệ thống tâm thu tuyến tính cho 1-D FFT. Phương pháp khéo léo này có thể

dùng để phát triển cấu trúc cho DCT 1-D. Tôi sẽ không đi vào chi tiết cho các

phát triển này, và để nó như là một bài tập cho các độc giả. Chúng ta sẽ giới

thiệu cách làm thế nào chúng ta có thể dùng phần cứng cho biến đổi 1-D DCT

để phát triển cho 2-D DCT. Các ứng dụng chính cho cấu trúc này là các khối

mã hoá và phóng đại ảnh hoặc thu nhỏ ảnh.

Bài tập 16.9

1. Nghiên cứu trang “Một mảng tâm thu tuyến tính mới cho tính FFT” bởi

Choi và Boriakoff trong IEEE Transaction on Circuit and Systems_II:

Analog and Digital Signal Processing, cuốn 39, số 4, tháng 4 năm 1992.

2. Dùng phương pháp trong trang này để phát triển một kỹ thuật tâm thu

tuyến tính cho DCT mà yêu cầu chỉ log2N khối xử lý.

3. Thực hiện 2-D DCT trước khi đọc tiếp phần tiếp theo.

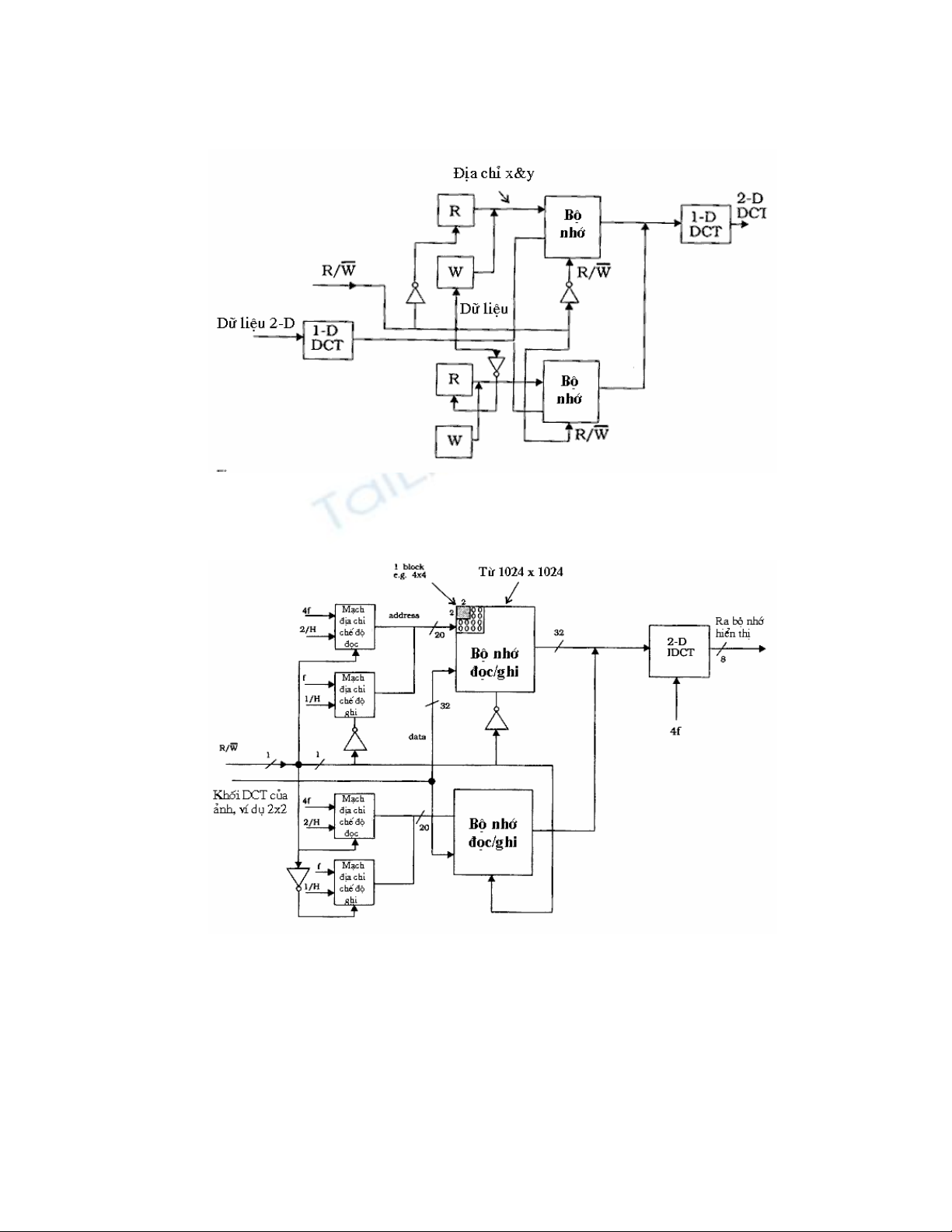

Các kỹ thuật cho biến đổi 1-D có thể dùng để đưa ra các kỹ thuật cho biến

đổi 2-D như trong hình 16.52. Các khối R và W trong hình và các thanh ghi

điều khiển địa chỉ đọc viết. Thanh ghi địa chỉ chế độ viết tạo ra địa chỉ để viết

trong bộ nhớ trong một hàng trong kiểu viết theo hàng, và thanh ghi địa chỉ

đọc tạo ra địa chỉ đọc từ bộ nhớ viết theo cột. Hai mảng bộ nhớ đọc/viết được

cần để cho phép liên tục dòng dữ liệu, như giải thích trong phần 16.9. Đầu ra

của khối DCT thứ hai là đầu vào dữ liệu của 2-D DCT. Rất dễ dàng để phát

triển mạch điện cho các khối R và W.

Để phóng đại ảnh vào dùng khối DCT chúng ta có thể dùng cấu trúc trong

hình 16.53. Một lần nữa nhắc lại, thiết kế các thanh ghi chế độ đọc và viết

được để lại cho độc giả. Giá trị không được thêm vào tất cả các khối DCT và

một 2-D IDCT cng cấp nhân đôi ảnh nhập vào. Đầu ra được gửi đến một mạch

khác để hiển thị, và tất nhiên, trở nên khác so với trong trường hợp này.

468

Hình 16.52 2-D DCT.

Hình 16.53 Sự phóng đại ảnh trong thời gian thực sử dụng DCT.

Một thiết kế thiết kế cho hình 16.53 được giới thiệu trong hình 16.54 và

16.55. Thiết kế này không yêu cầu dùng các bộ lọc 2-D và có thể trở nên hấp

dẫn hơn phương pháp nội suy không gian đề cập trước đây. Thiết kế các thanh

ghi địa chỉ được để lại như một bài tập cho độc giả. Phần cứng hoạt động theo:

Dữ liệu được đọc từ bộ nhớ đọc được 512 512 bộ nhớ R/W trong các khối 4

![Bài giảng Thiết kế Macromedia Flash 8 [Chuẩn SEO]](https://cdn.tailieu.vn/images/document/thumbnail/2021/20210711/chuheodethuong/135x160/1350144886.jpg)

![Giáo trình Nguyên lý hệ điều hành - Trường Cao đẳng Kỹ thuật Công nghệ Hòa Bình [Mới Nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260410/songngu_011/135x160/13351776314356.jpg)

![Giáo trình Tin học văn phòng Trường Cao đẳng Kỹ thuật Công nghệ Hòa Bình [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260410/songngu_011/135x160/86771776310992.jpg)