ThiÕt kÕ m¹ch logic sè PhÇn V: Phô lôc

1

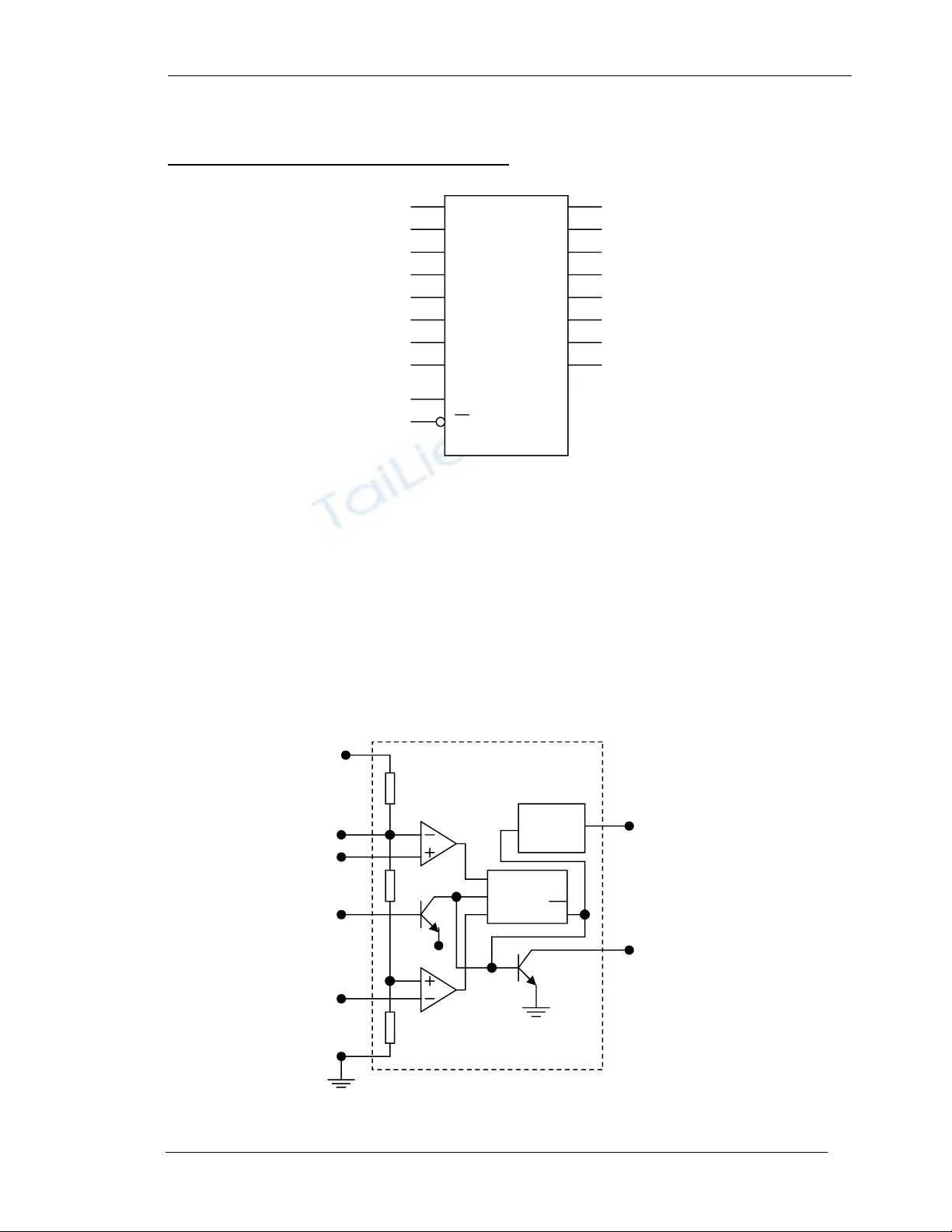

7. Bé ®Öm tÝn hiÖu hai chiÒu 74245:

Bé ®Öm tÝn hiÖu hai chiÒu 74245 cho phÐp tÝn hiÖu ®i theo hai chiÒu tuú

thuéc møc logic ë ®Çu vµo DIR. Khi DIR ë møc cao th× tÝn hiÖu ®i tõ

®Çu vµo Ai ra ®Çu Bi, ng-îc l¹i, khi DIR ë møc logic thÊp th× tÝn hiÖu ®i

tõ ®Çu vµo Bi ra ®Çu Ai.

A1

A2

A3

A4

A5

A6

A7

A8

B1

B2

B3

B4

B5

B6

B7

B8

DIR

G

2

3

4

5

6

7

8

9

1

19

11

12

13

14

15

16

17

18

74245

R

S

Rd

FF

Q

Output

Buffer

R

R

R

Comparator 1

Comparator 2

T1

T2

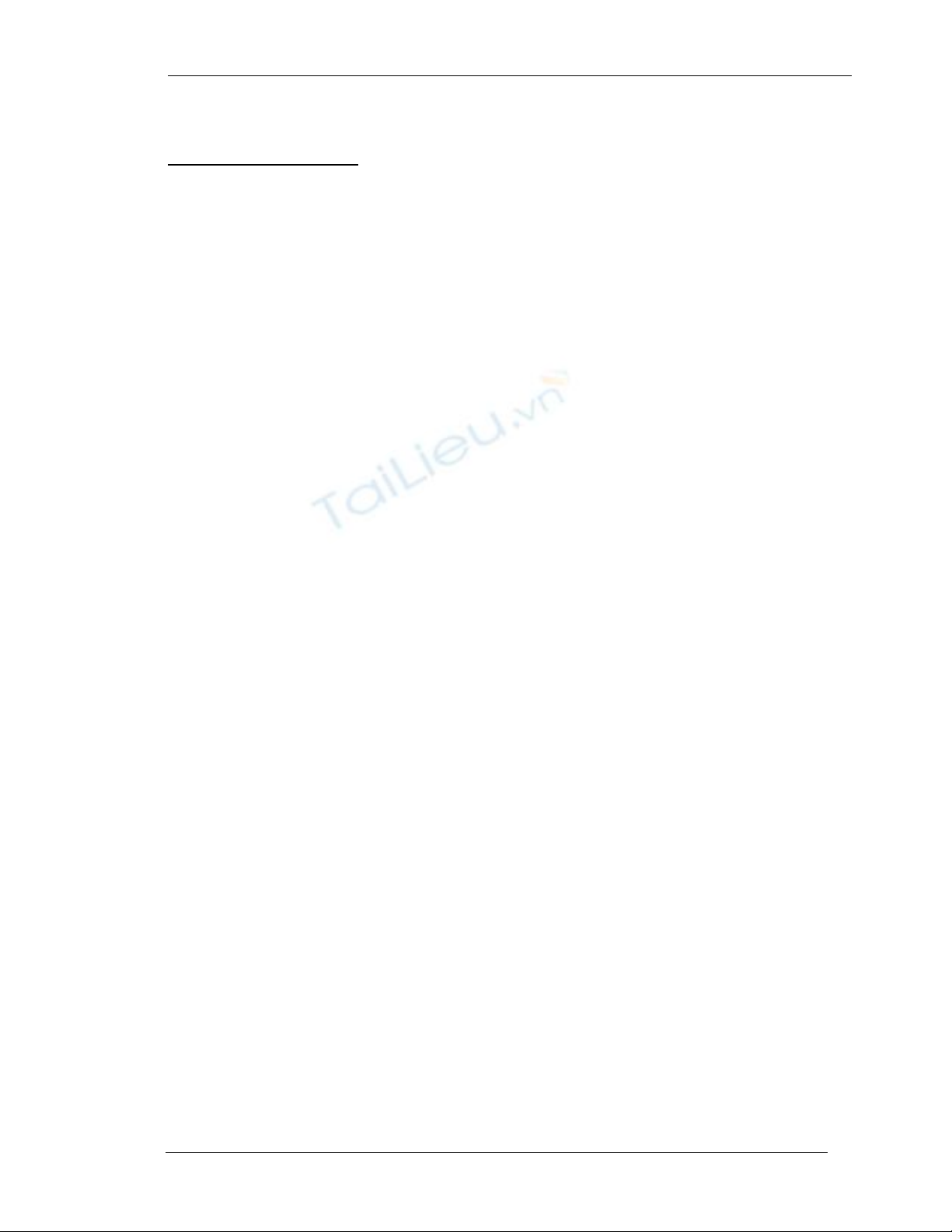

H×nh I.8.1

–

S¬ ®å chøc n¨ng bé

®Þnh thêi 555

ThiÕt kÕ m¹ch logic sè PhÇn V: Phô lôc

2

8. Bé ®Þnh thêi 555:

Vi m¹ch 555 cã thÓ dïng ®Ó thùc hiÖn nhiÒu chøc n¨ng nh-: t¹o

xung thêi gian, t¹o dao ®éng ®a hµi (xung vu«ng, xung tam gi¸c), ®iÒu

chÕ ®é réng xung, v.v.. Trªn h×nh I.8.1 lµ s¬ ®å chøc n¨ng cña vi m¹ch

555. Vi m¹ch nµy cã thÓ lµm viÖc víi ®iÖn ¸p nguån cung cÊp UCC tõ

+5V ®Õn +15V. D·y ®iÖn trë m¾c theo kiÓu ph©n ¸p tõ UCC ®Õn ®Êt t¹o

ra ®iÖn ¸p chuÈn cho hai bé so s¸nh 1 vµ 2, trong ®ã ®iÖn ¸p chuÈn cho

bé so s¸nh 2 lµ UCC/3 vµ cho bé so s¸nh 1 lµ 2UCC/3. Nh- ta sÏ thÊy c¸c

®iÖn ¸p chuÈn nµy dïng ®Ó ®iÒu khiÓn viÖc ®Þnh thêi gian. Trong c¸c

øng dông mµ ta muèn thay ®æi viÖc ®Þnh thêi gian b»ng ph-¬ng ph¸p

®iÖn tö ta cã thÓ thùc hiÖn b»ng c¸ch ®-a mét ®iÖn ¸p ®iÒu chÕ vµo ch©n

5 (®Çu vµo ®iÖn ¸p ®iÒu khiÓn). Cßn trong c¸c øng dông kh¸c th× ta cã

thÓ nèi ch©n 6 xuèng ®Êt qua mét tô ®iÖn (cã trÞ sè vµo kho¶ng

0,001F).

Trung t©m ho¹t ®éng cña vi m¹ch 555 lµ FF-RS. §Çu vµo R cña

FF lµ ®Çu ra

ThiÕt kÕ m¹ch logic sè PhÇn V: Phô lôc

3

cña bé so s¸nh 1, cßn ®Çu vµo S cña FF lµ ®Çu ra cña bé so s¸nh 2.

M¹ch ra cña FF gåm 2 phÇn: mét phÇn lµ bé ®Öm ®Çu ra vµ mét phÇn

gåm 2 transistor T1, T2. Trong ®ã T1 dïng ®Ó biÕn ®æi tÝn hiÖu ra ®·

®-îc ghi gi÷, chÝnh ®iÖn ¸p nµy sÏ ®-îc sö dông cho nhiÒu môc ®Ých

kh¸c nhau. Th«ng qua T2 ta cã thÓ ®iÒu khiÓn ®-îc tr¹ng th¸i bªn trong

cña bé ®Öm ®Çu ra.

1 8

2 7

3 6

4 5

Ground

Trigger

Output

Reset

U

CC

Discharge

Threshold

Control Voltage

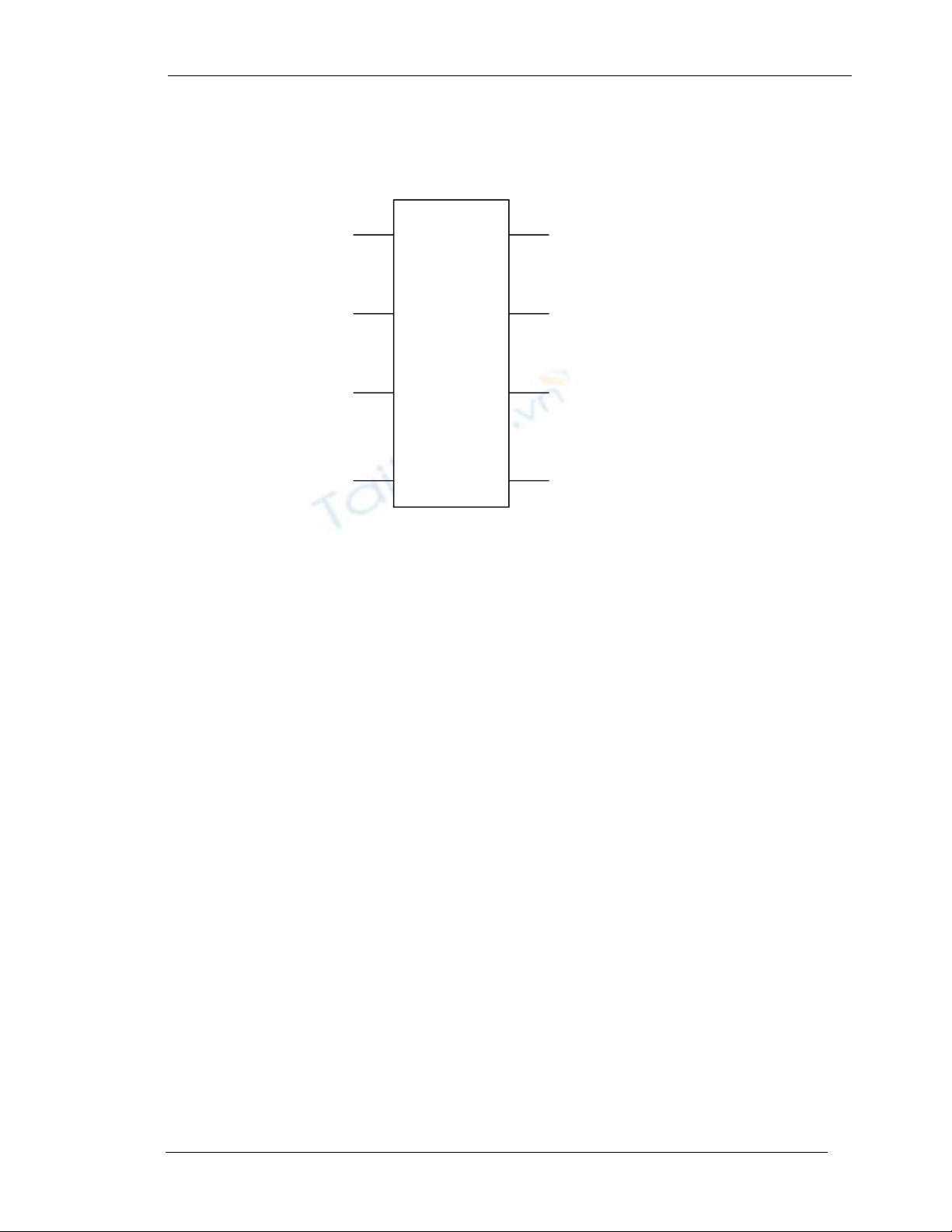

H×nh I.8.2

–

C¸c ch©n bªn

ngoµi

cña vi m¹ch 555

ThiÕt kÕ m¹ch logic sè PhÇn V: Phô lôc

4

Vi m¹ch 555 gåm cã 8 ch©n nh- h×nh I.8.2, trong ®ã ch©n1 lµ

ch©n nèi ®Êt (Ground), ch©n 2 lµ ®Çu vµo bé so s¸nh 2 (Trigger), ch©n 3

lµ ®Çu ra (Output), ch©n 4 lµ ch©n ®iÒu khiÓn ®iÖn ¸p ®Çu ra (Reset),

ch©n 5 lµ ch©n ®iÖn ¸p ®iÒu khiÓn (Control Voltage), ch©n 6 lµ ng-ìng

cña bé so s¸nh 1 (Theshold), ch©n 7 lµ ch©n ®Ó phãng ®iÖn (Discharge)

vµ ch©n 8 lµ ch©n ®iÖn ¸p nguån cung cÊp (UCC).

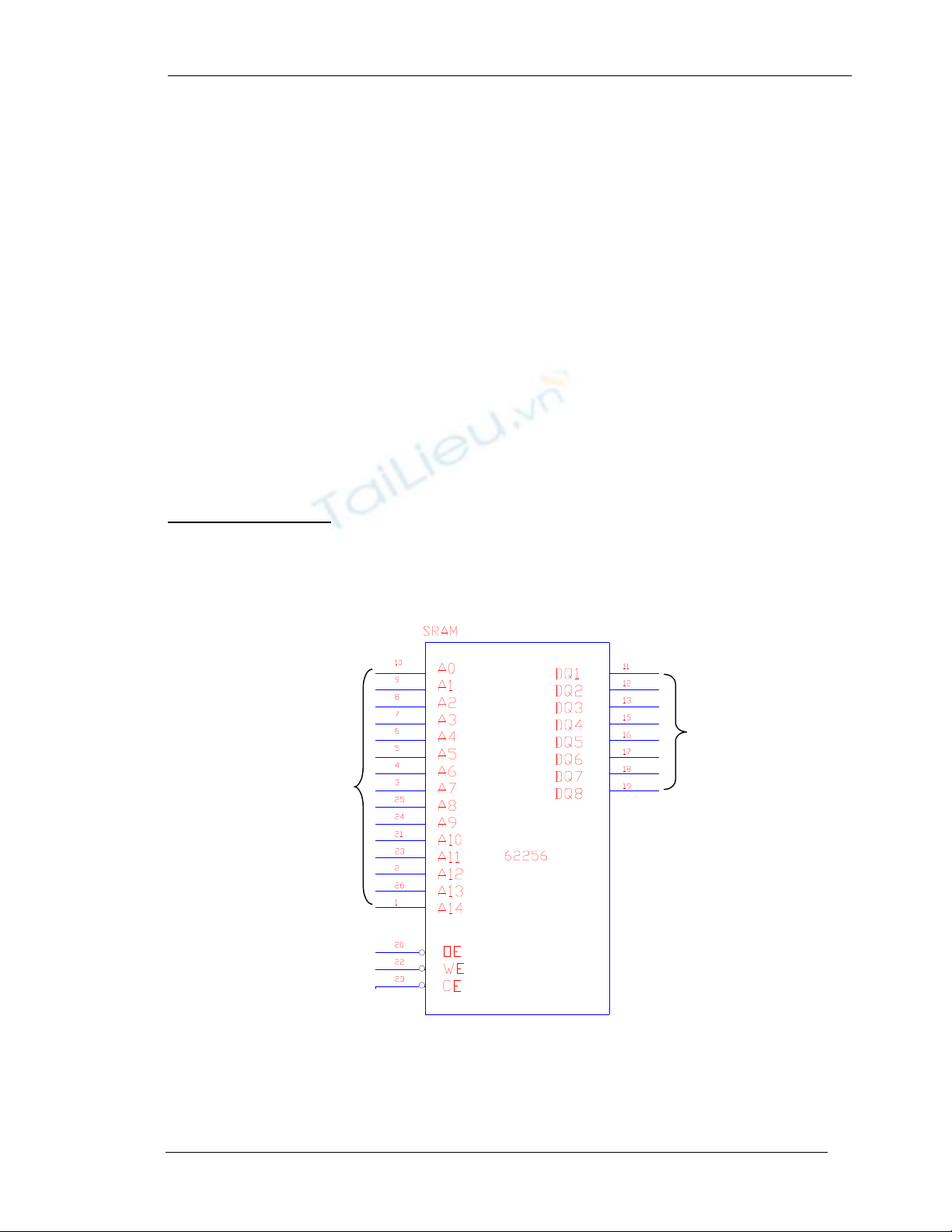

9. SRAM 62256

Dung l-îng: 32K x 8bit

S¬ ®å c¸c ch©n:

I C3 9

I C3 3

§Çu

vµo

§Þa

chØ

§Çu

ra

d÷

liÖu

Cho phÐp ®äc

Cho phÐp ghi

Chän chÝp

ThiÕt kÕ m¹ch logic sè PhÇn V: Phô lôc

5

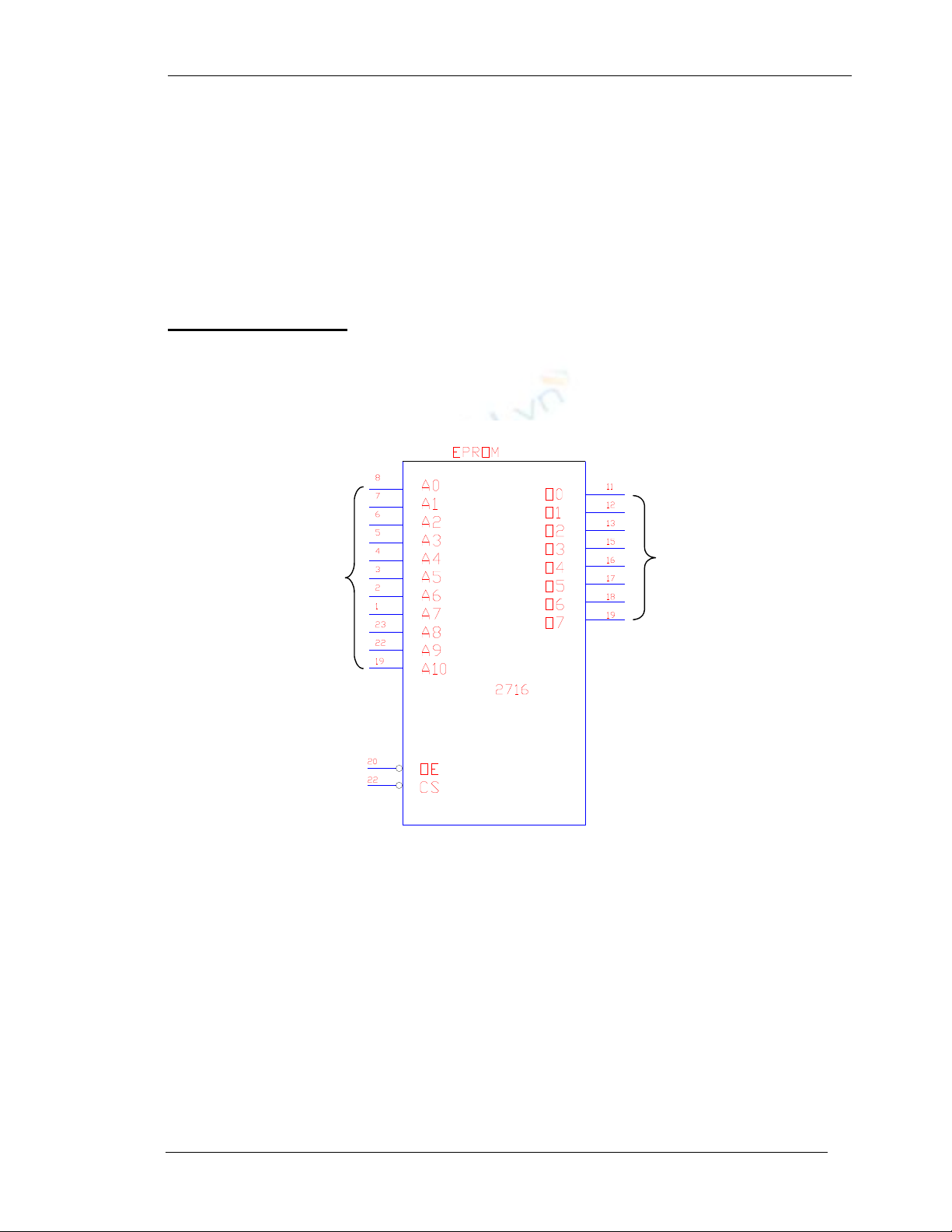

10. EPROM 2716

Dung l-îng: 2K x 8 bit

S¬ ®å c¸c ch©n:

§Çu

vµo

§Þa

chØ

§Çu

ra

d÷

liÖu

Cho phÐp ®äc

Chän chÝp

![Tài Liệu Kỹ Thuật: [Thêm thông tin chi tiết để tối ưu SEO]](https://cdn.tailieu.vn/images/document/thumbnail/2011/20110929/dohongpro/135x160/machrobot_6244.jpg)

![Giáo trình CAD và ứng dụng (Phần thực hành): [Hướng dẫn chi tiết]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260305/hoatulip2026/135x160/80431773135924.jpg)

![Giáo trình CAD và ứng dụng: [Hướng dẫn chi tiết/Tài liệu đầy đủ]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260305/hoatulip2026/135x160/37741773135924.jpg)