T ng quan v atmega16ổ ề

Các tính năng c a Atmega16 :ủ

- Hi u xu t cao ( high performance ), là lo i vi đi u khi n AVR 8 bit côngệ ấ ạ ề ể

su t th pấ ấ

- C u trúc l nh đ n gi n, th i gian th c thi l nh nh nhau ( th t ra làấ ệ ơ ả ờ ự ệ ư ậ

Advanced RISC Architecture )

o130 l nh th c thi trong vòng 1 chu kì chipệ ự

o32 x 8 thanh ghi công d ng chung ( ch c là 32 thanh ghi côngụ ắ

d ng chung 8 bit )ụ

oĐ y đ các s lí tĩnhầ ủ ử

oH tr 16 MIPS khi ho t đ ng t n s 16 MHzỗ ợ ạ ộ ở ầ ố

oTích h p b nhân 2 th c hi n trong 2 chu kì chipợ ộ ự ệ

- B nh ch ng trình và d li u không bay h i ( nonvolatile )ộ ớ ươ ữ ệ ơ

o16k byte trong h th ng flash kh trình có th n p và xóa 1,000ệ ố ả ể ạ

l nầ

o Tùy ch n kh i đ ng ph n mã v i các bit nhìn đ c l p trong họ ở ộ ầ ớ ộ ậ ệ

th ng b ng cách vào ch ng trình kh i đ ng chipố ằ ươ ở ộ

o512 byte EEPROM có th ghi và xóa 100,000 l nể ầ

o1k byte ram nh tĩnh trong ( internal SRAM )ớ

oL p trình khóa cho ph n m m b o m pậ ầ ề ả ậ

- Tính năng ngo i viạ

○ 2 b đ nh th i/b đ m ( timers/counters ) 8 bit v i các ch độ ị ờ ộ ế ớ ế ộ

đ m ế riêng r và ki u so sánhẽ ể

○ 1 b đ nh th i/b đ m ( timer/counter ) 16 bit v i các ch đ đ mộ ị ờ ộ ế ớ ế ộ ế

riêng r , ki u so sánh và ki u b t s ki nẽ ể ể ắ ự ệ

○ B đ m th i gian th c v i máy giao đ ng riêng rộ ế ờ ự ớ ộ ẽ

○ 4 kênh băm xung PWM

○ 8 kênh ADC 10 bit

○ Byte đ nh h ng 2 đ ng giao ti p n i ti pị ướ ườ ế ố ế

○ Giao ti p USART n i ti p kh trìnhế ố ế ả

○ Giao ti p SPI n i ti p ch /t ( master/slave )ế ố ế ủ ớ

○ B đ nh th i kh trình giám sát xung nh p c a chip 1 cách riêng rộ ị ờ ả ị ủ ẽ

○ Tích h p b so sánh tín hi u t ng tợ ộ ệ ươ ự

- Giao ti p JTAGế

- Các tính năng đ t bi t c a vi đi u khi nặ ệ ủ ề ể

○ Ch đ b t ngu n reset và phát hi n Brown-out kh trìnhế ộ ậ ồ ệ ả

○ Tích h p m ch dao đ ng RC bên trongợ ạ ộ

○ Các ng t trong và ngoàiắ

○ 6 ch đ ngh : r nh r i,gi m nhi u ADC, Ti t ki m năng l ng,ế ộ ỉ ả ỗ ả ễ ế ệ ượ

ngu n th p, Standby và Extended Standbyồ ấ

- Vào/ra và các gói d li uữ ệ

○ 32 chân vào ra kh trìnhả

○ 40-pin PDIP and 44-lead TQFP

- Đi n áp s d ngệ ử ụ

○ 2.7 – 5.5V dùng v i atmega16Lớ

○ 4.5 – 5.5V dùng v i atmega16ớ

- T c đ xung nh p dùng cho chipố ộ ị

○ 0 – 8 MHz cho atmega16L

○ 0 – 16 MHz cho atmega16

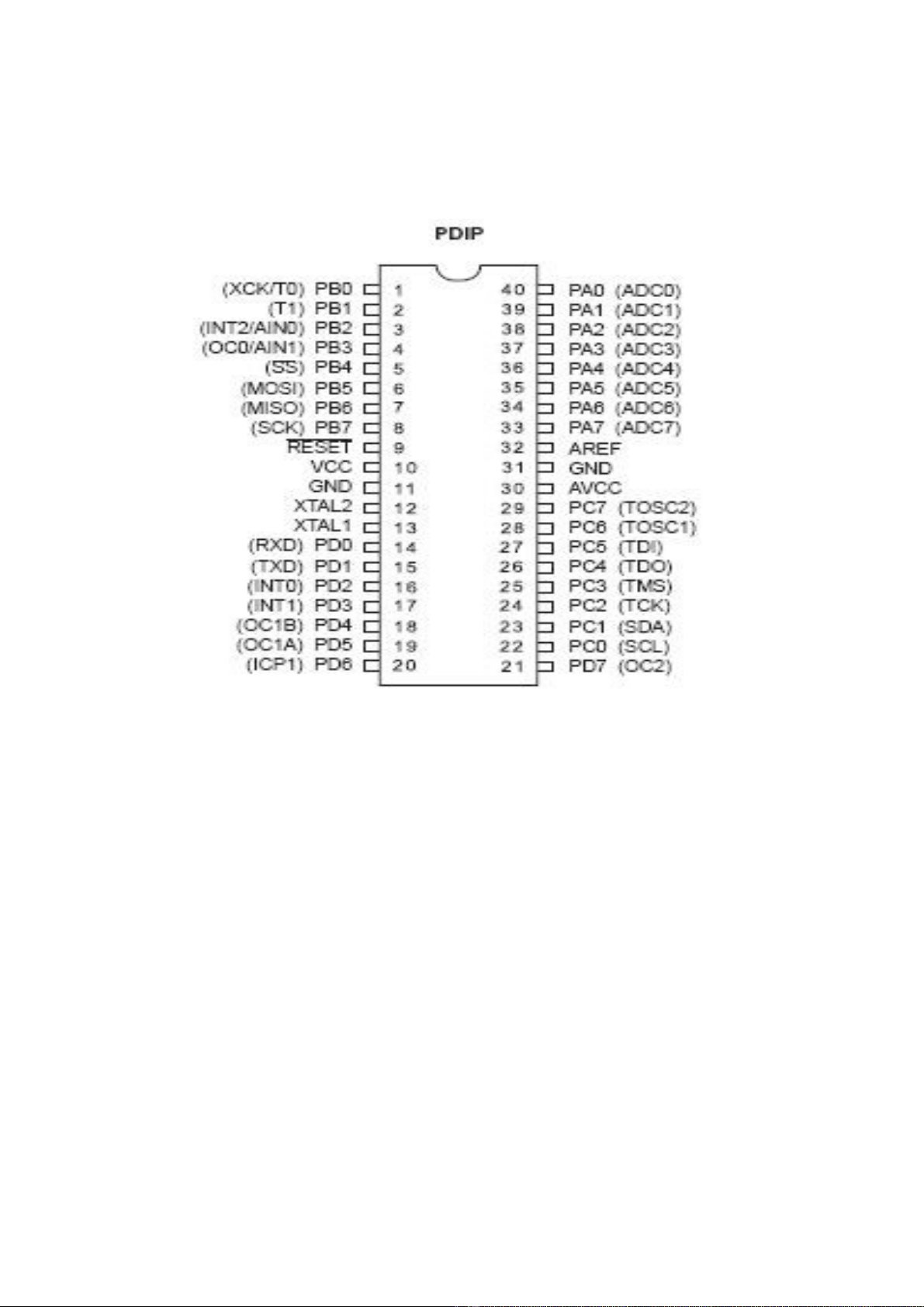

1, s đ chânơ ồ

Atmega16 g m có 40 chân:ồ

- Chân 1 đ n 8 : C ng nh p xu t d li u song song B ( PORTB ) nó cóế ổ ậ ấ ữ ệ

th đc s d ng các ch c năng đ c bi t thay vì nh p xu t d li uể ử ụ ứ ặ ệ ậ ấ ữ ệ

- Chân 9 : RESET đ đ a chip v tr ng thái ban đ uể ư ề ạ ầ

- Chân 10 : VCC c p ngu n nuôi cho vi đi u khi nấ ồ ề ể

- Chân 11,31 : GND 2 chân này đc n i v i nhau và n i đ tố ớ ố ấ

- Chân 12,13 : 2 chân XTAL2 và XTAL1 dùng đ đ a xung nh p t bênể ư ị ừ

ngoài vào chip

- Chân 14 đ n 21 : C ng nh p xu t d li u song song D ( PORTD ) nó cóế ổ ậ ấ ữ ệ

th đc s d ng các ch c năng đ c bi t thay vì nh p xu t d li uể ử ụ ứ ặ ệ ậ ấ ữ ệ

- Chân 22 đ n 29 : C ng nh p xu t d li u song song C ( PORTC ) nó cóế ổ ậ ấ ữ ệ

th đc s d ng các ch c năng đ c bi t thay vì nh p xu t d li uể ử ụ ứ ặ ệ ậ ấ ữ ệ

- Chân 30 : AVCC c p đi n áp so sánh cho b ADCấ ệ ộ

- Chân 32 : AREF đi n áp so sánh tín hi u vào ADCệ ệ

- Chân 33 đ n 40 : C ng vào ra d li u song song A ( PORTA ) ngoài raế ổ ữ ệ

nó còn đc tích h p b chuy n đ i tín hi u t ng t sang tín hi u sợ ộ ể ổ ệ ươ ự ệ ố

ADC ( analog to digital converter

2, Vào ra c a vi đi u khi nủ ề ể

PORTA ( PA7 … PA0 ) : là các chân s 33 đ n 40. Là c ng vào ra song songố ế ổ

8 bít khi không dùng ch đ ADC. Bên trong có s n các đi n tr kéo, khi PORTAở ế ộ ẵ ệ ở

là output thì các đi n tr kéo ko ho t đ ng , khi PORTA là input thì các đi n trệ ở ạ ộ ệ ở

kéo đc kích ho t.ạ

PORTB ( PB7 ... PB0 ) : là các chân s 1 đ n 8. Nó t ng t nh PORTAố ế ươ ự ư

khi s d ng vào ra song song. Ngoài ra các chân c a PORTB còn có các ch c năngử ụ ủ ứ

đ t bi t s đc nh c đ n sau.ặ ệ ẽ ắ ế

PORTC ( PC7 ... PC0 ) : là các chân 22 đ n 30. Cũng gi ng PORTA vàế ố

PORTB khi là c ng vào ra song song. N u giao ti p JTAG đc b t, các tr treo cácổ ế ế ậ ở ở

chân PC5(TDI), PC3(TMS), PC2(TCK) s ho t đ ng khi s ki n reset s y ra. Ch cẽ ạ ộ ự ệ ả ứ

năng giao ti p JTAG và 1 s ch c năng đ c bi t khác s đc nghiên c u sauế ố ứ ặ ệ ẽ ứ

PORTD ( PD7 ... PD0 ) : là các chân 13 đ n 21. Cũng là 1 c ng vào ra songế ổ

song gi ng các PORT khác, ngoài ra nó còn có 1 s tính năng đ c bi t s đc nghiênố ố ặ ệ ẽ

c u sau.ứ

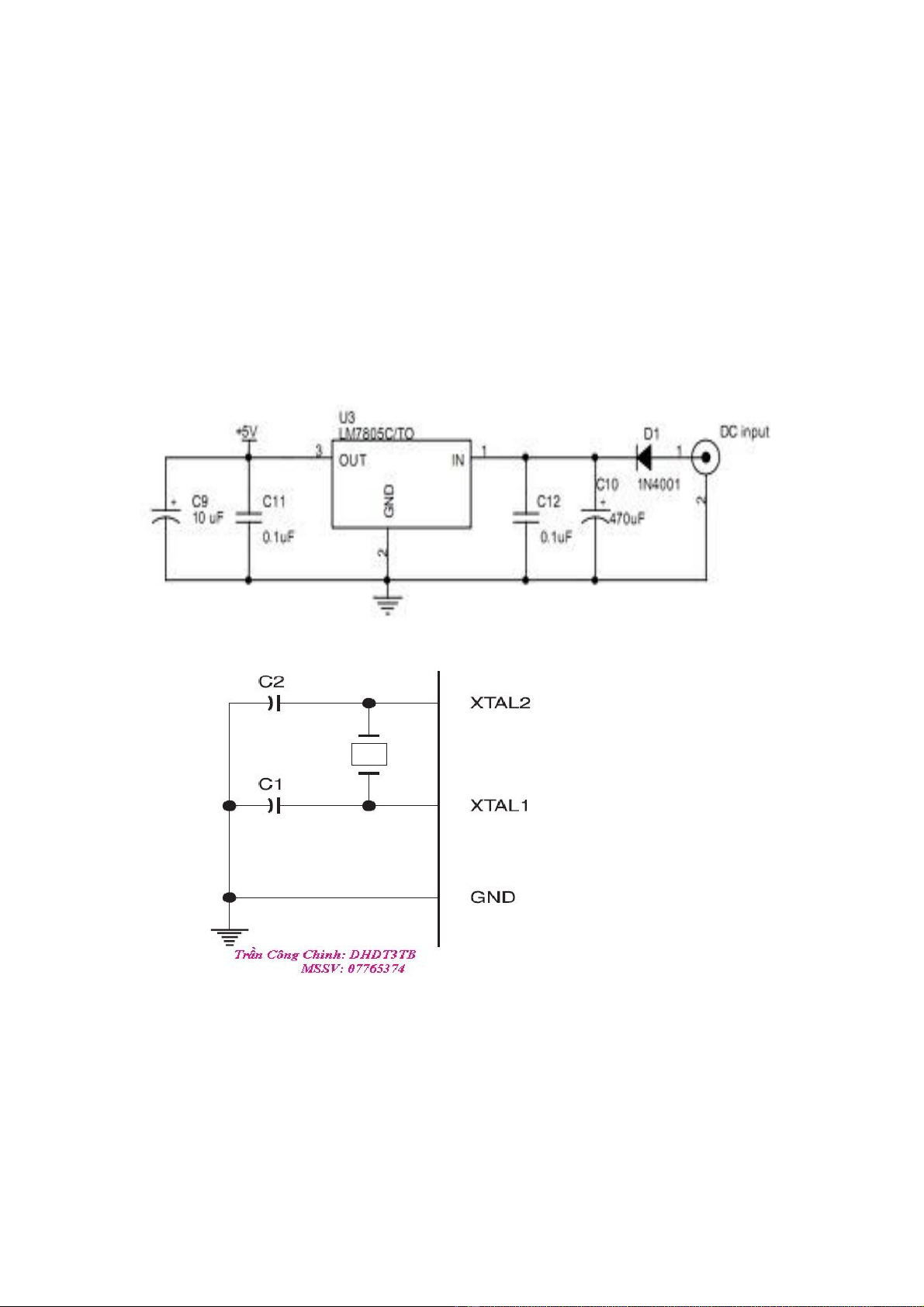

3, m ch c p ngu n nuôi cho vi đi u khi nạ ấ ồ ề ể

4, m ch c p giao đ ng ngoài cho vi đi u khi n dùng th ch anhạ ấ ộ ề ể ạ

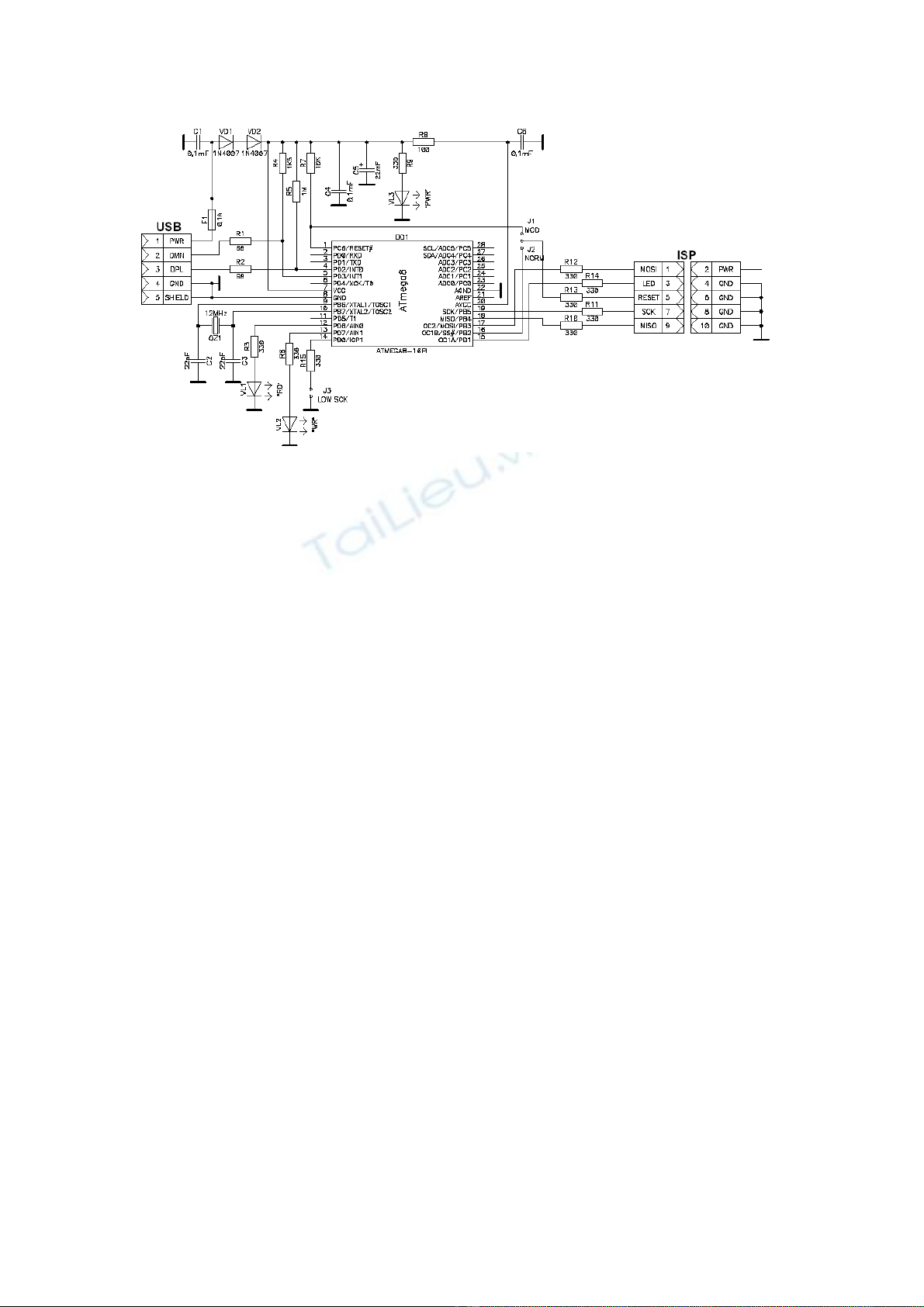

5, M ch n p avr910 usbạ ạ

![Bảng mô tả hệ thống điều khiển [chuẩn SEO]](https://cdn.tailieu.vn/images/document/thumbnail/2011/20111003/jakkyjery/135x160/thuyet_minh_toa_nha_fpt_6163.jpg)

![Hệ thống BMS của Nguyễn Duy Minh: [Thêm Mô Tả Giá Trị Cao]](https://cdn.tailieu.vn/images/document/thumbnail/2011/20111003/jakkyjery/135x160/he_thong_bms_do_nguyen_duy_minh_viet_1114.jpg)

![Giáo trình Vô tuyến điện viên hàng hải GMDSS hạng tổng quát: Phần 1 [Chuẩn Nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260504/vispacex_27/135x160/45101777969769.jpg)