•Bách Khoa Online: hutonline.net

Bách Khoa Online: hutonline.net

•Tìm ki m & download ebook: ế

Tìm ki m & download ebook: ế

bookilook.com

bookilook.com

Bay gi ng K thu t Vi x lýả ỹ ậ ử

Ngành Đi n t -Vi n thôngệ ử ễ

Đ i h c Bách khoa Đà N ngạ ọ ẵ

c a H Vi t Vi t, Khoa CNTT-ĐTVTủ ồ ế ệ

Tài li u tham kh oệ ả

[1] K thu t vi x lý, Văn Th Minh, NXB ỹ ậ ử ế

Giáo d c, 1997ụ

[2] K thu t vi x lý và L p trình Assembly cho ỹ ậ ử ậ

h vi x lý, Đ Xuân Ti n, NXB Khoa h c & ệ ử ỗ ế ọ

k thu t, 2001ỹ ậ

Chương 3

Vi x lý 8088-Intelử

3.1 Ki n trúc và ho t đ ng c a 8088ế ạ ộ ủ

- Nguyên lý ho t đ ngạ ộ

- S đ kh i ch c năngơ ồ ố ứ

3.2 C u trúc thanh ghi c a 8088ấ ủ

3.3 Ph ng pháp qu n lý b nhươ ả ộ ớ

3.4 Mô t t p l nh Assemblyả ậ ệ

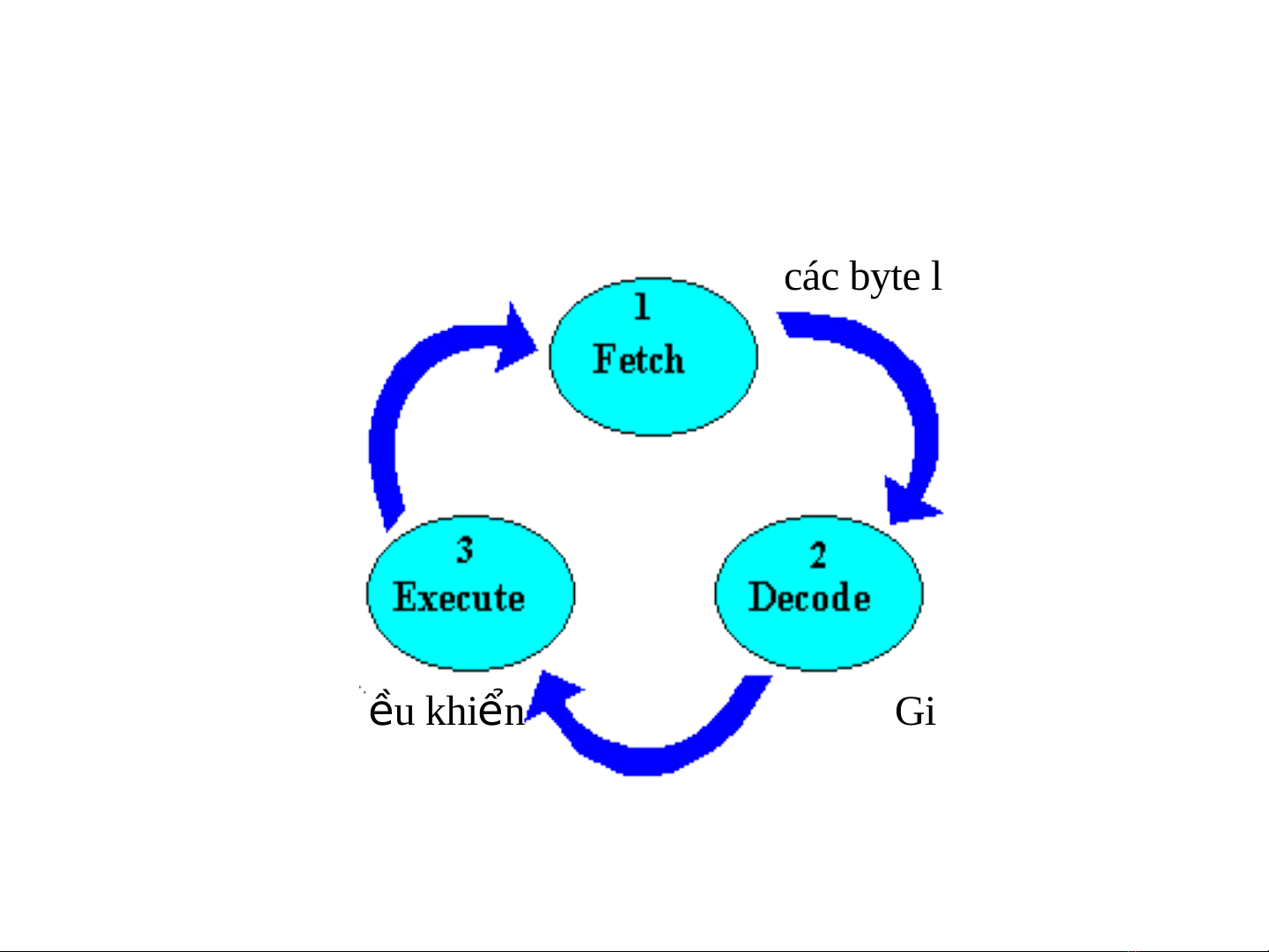

L y - Gi i mã - Th c hi n l nhấ ả ự ệ ệ

Tìm và copy

các byte l nh t b nhệ ừ ộ ớ

Gi i mã l nhả ệT o ra các tín hi u đi u khi nạ ệ ề ể

đ th c hi n l nhể ự ệ ệ

Nguyên lý ho t đ ng c a m t b vi x lýạ ộ ủ ộ ộ ử

Chu kỳ l nh và Chu kỳ máyệ

•Chu kỳ l nh: T ng th i gian tìm l nh, gi i ệ ổ ờ ệ ả

mã l nh và th c hi n 1 l nhệ ự ệ ệ

•Nói chung, Chu kỳ l nh c a các l nh khác ệ ủ ệ

nhau là khác nhau

•Chu kỳ l nh bao gi cũng b ng m t s ệ ờ ằ ộ ố

nguyên l n chu kỳ máyầ

•Chu kỳ máy b ng ngh ch đ o c a t n s ằ ị ả ủ ầ ố

ho t đ ng (t c đ đ ng h ) c a b vi x ạ ộ ố ộ ồ ồ ủ ộ ử

lý