DuyTan University Assembly Language Programming

CHNG 7

ASSEMBLY CHO

VI IUKHIN

I HCDUY TÂN

KHOA CÔNG NGHTHÔNG TIN

Nguyn VnTh

Bmôn in tvinthông

Khoa Công nghthông tin, i hcDuy Tân – 2007

5-2

Nguyen Van Tho – Duy Tan University

5-2

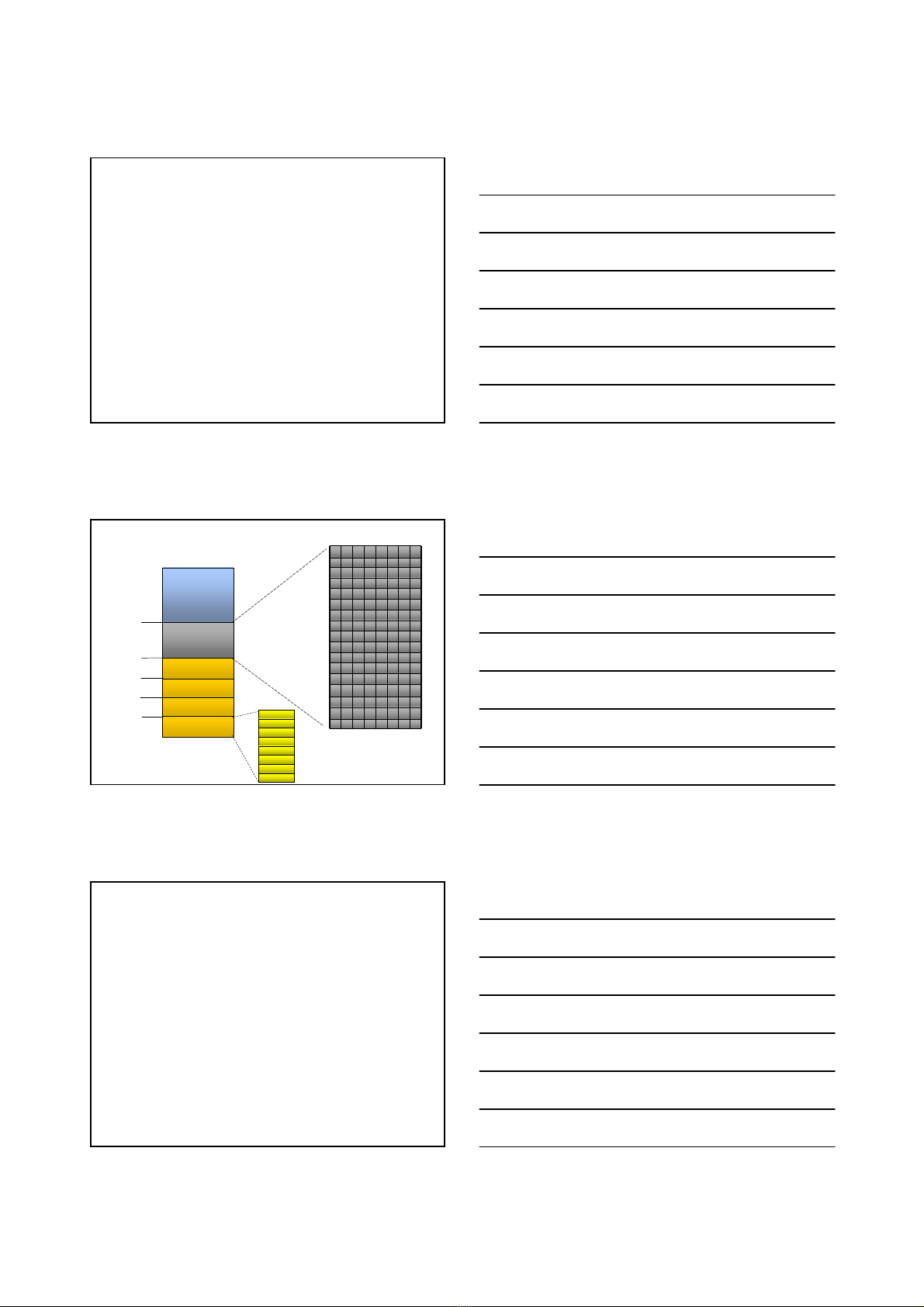

GIITHIU

Các vi b% &i'ukhi+nvà các b%vi x/lý có ba &i+mkhác

nhau chính sau:

Ki8ntrúc ph=n c>ng

PhAmvi >ng dCng

Dc&i+m tEp lFnh

Các hGvi &i'ukhi+nphHbi8n

Intel 8051

PIC16C5x

Motorola MC68xxx

AVR

PSoC

5-3

Nguyen Van Tho – Duy Tan University

5-3

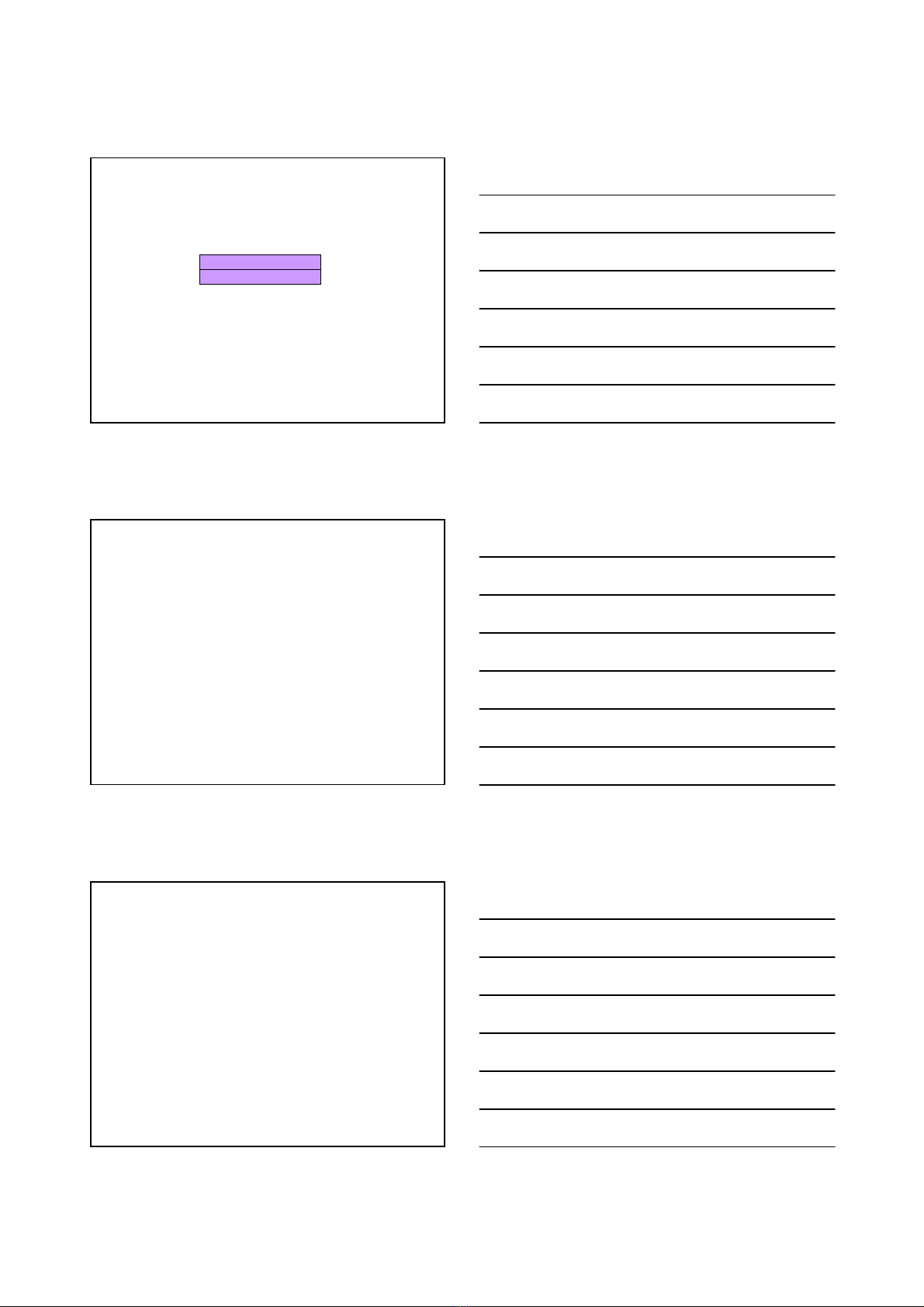

VI IUKHIN8051

HiFnnay có hRn40 công ty sUnxuVtcác loAivi &i'ukhi+n

khác nhau cWa hG8051.

M%t sYcông ty có trên 40 version 8051.

Các CORE 8051 có th+&[\c tHh\ptrong các FPGA hay

ASIC.

Trên 100 triFuvi &i'ukhi+n8051 &[\cbán ra m^i n_m.

HG8051 gDthái &[\c rVtnhi'uthành công và nó c`ng

tracti8pUnh h[bng &8n cVutrúc cWacác hGvi &i'ukhi+n

hiFnnay.