ChươngIV:MchLogics

143

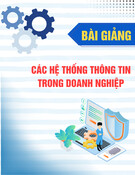

A

B

Sum

Carry

0 0 0 0

0 1 1 0

1 0 1 0

1 1 0 1

!"

#

Hình4.16.Bncacng

Bn^acngnàychchophéptatínhtngbitcGcph*ic+a

hait`ñVuvàonhiubit,nhưngkhôngthGchiDnñưZcchovtríbít

=gi<at`vìnókhôngxclýsmangt`bênph*isangvtrínày,

haynóicáchkháckhôngcngvQisnhQtrongphépcongthông

thưWng.Nhưv!ybncacngnàykhôngth ápdmngñ thi(tk(

mt b cngcho 2 s có nhiu bit, thayvào ñó, ph*i càn tQi b

cngñVyñ+(fulladderl).

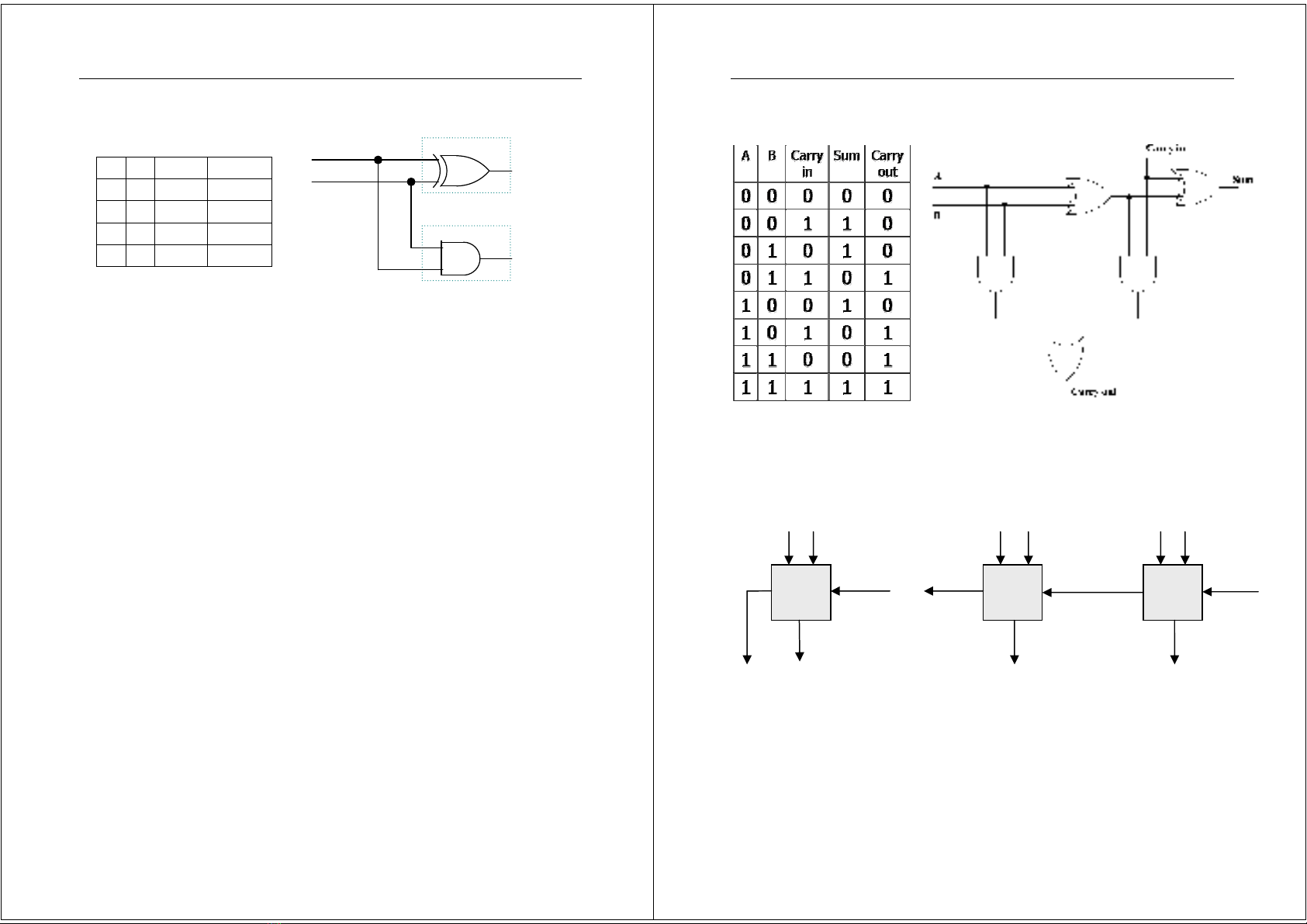

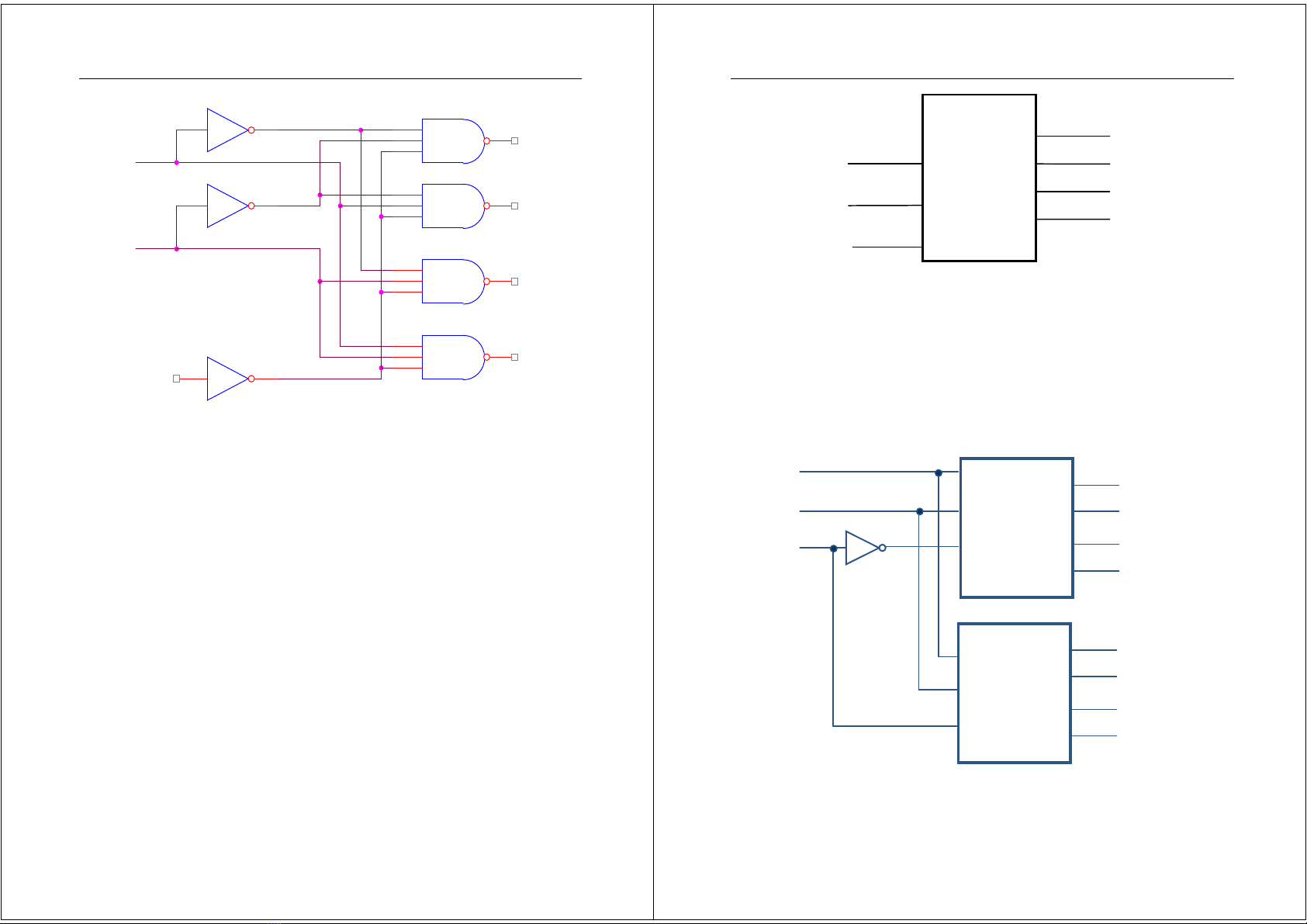

b)BJcJngñ;yñ?(FullAdder)

B*ngchântrvàm-chchobcng1bitñVyñ+tronghình

4.17.BcngñVyñ+ñưZccButhànht`haibncacng.ðVura

Sum

là1n(usliA,B,và

Carryin

b\ng1.

Carryout

b\ng1

khic*A và Bñub\ng 1(ñVuvào trái c+acngOR)hocñúng

mttrongschúngb\ng1vàbitCarryincũngb\ng1.

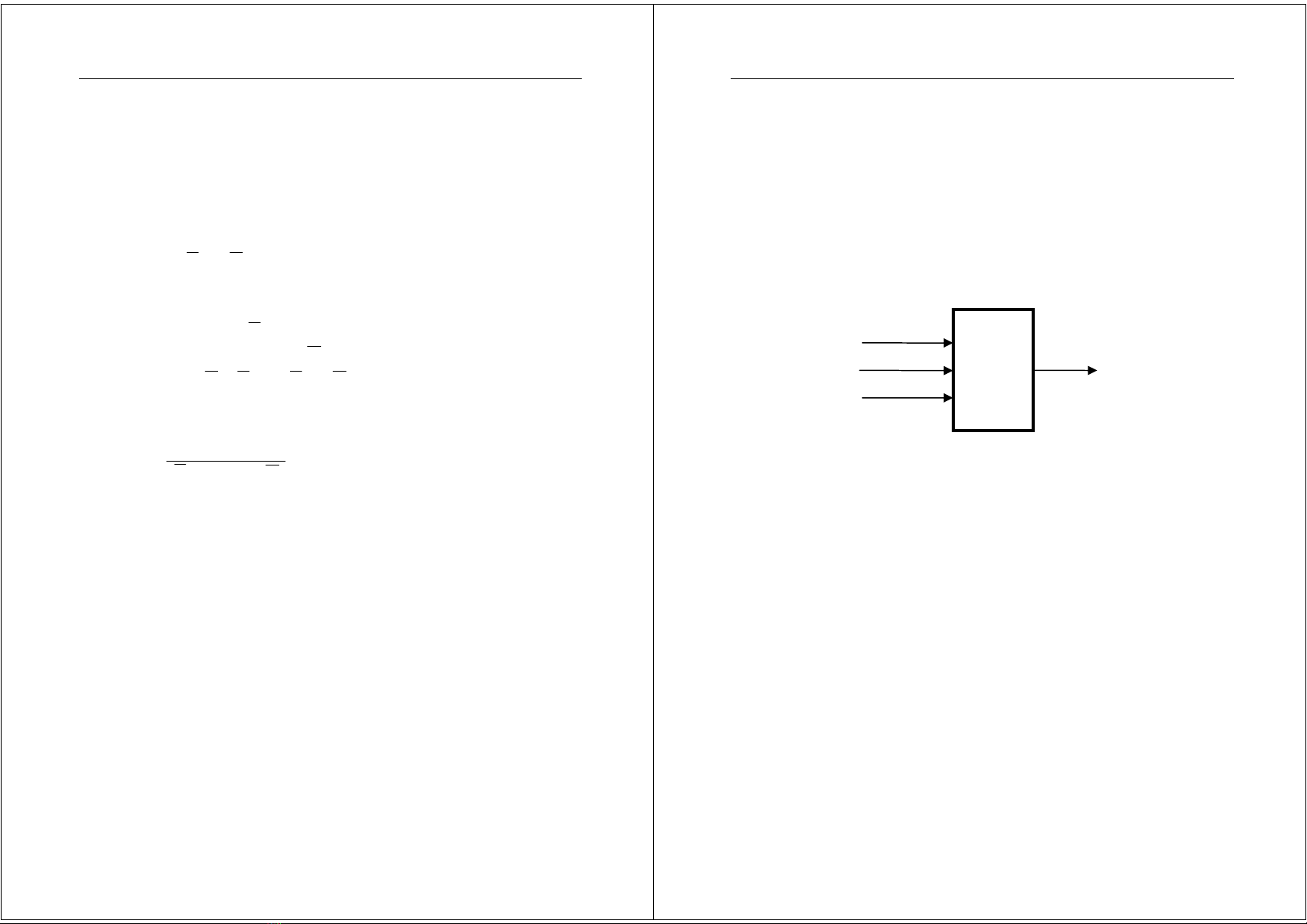

Gi*scñ(t-obcngchohait`AvàB,meit`16bt,ch

viDcsaochépm-chtronghình4.12ñúng16lVn.SnhQt`bítñưZc

dùnglàmsnhQvàobitbêntrái.SnhQvàobtcGctráiñưZcni

vào0.Lo-ibcngnàyñưZcg$ilàbcngsnhQ

ripple(ripple

carryadder)

.VìtrongtrưWnghZpxBunhBt,cng1vào111...11

1(nhphân),snhQripplet`bitcGcph*isangbitcGctráithìmQi

cngxongñưZc.DoñótrongcáctrưWnghZpnhưv!ythìbcng

nàys8rBtch!mvàkhônghiDuqu*.CũngcóbcngkhôngcósG

ChươngIV:MchLogics

144

trfnày,vàdoñónhanhhơn.SơñybcngñVyñ+chonbitnhư

hình4.18.

Hình4.17.BcngñVyñ+

4.3.5.M"chgi?imãvàmãhóa

Kháini[m:

M-chmãhoá

(ENCODER

)làm-chcónhiDmvmbi(nñi

nh<ngkýhiDuquenthucvQiconngưWisangnh<ngkýhiDukhông

quen thuc con ngưWi. M-ch gi*i mã (

DECODER

) là m-ch làm

Full

Adder

Full

Adder

Full

Adder

Carry

in0=0

Carry

in1

Carry

out0

Carry

out1

Carry

inno1

S0

S1

Sno1

B0

A0

B1

A1

Bno1

Ano1

Sn

Hinh4.18.Bcngnbit

ChươngIV:MchLogics

145

nhiDmvmngưZcl-im-chmãhóa,bi(nñinh<ngkýhiDukhông

quenthucvQiconngưWisangnh<ngkýhiDuquenthucvQicon

ngưWi.

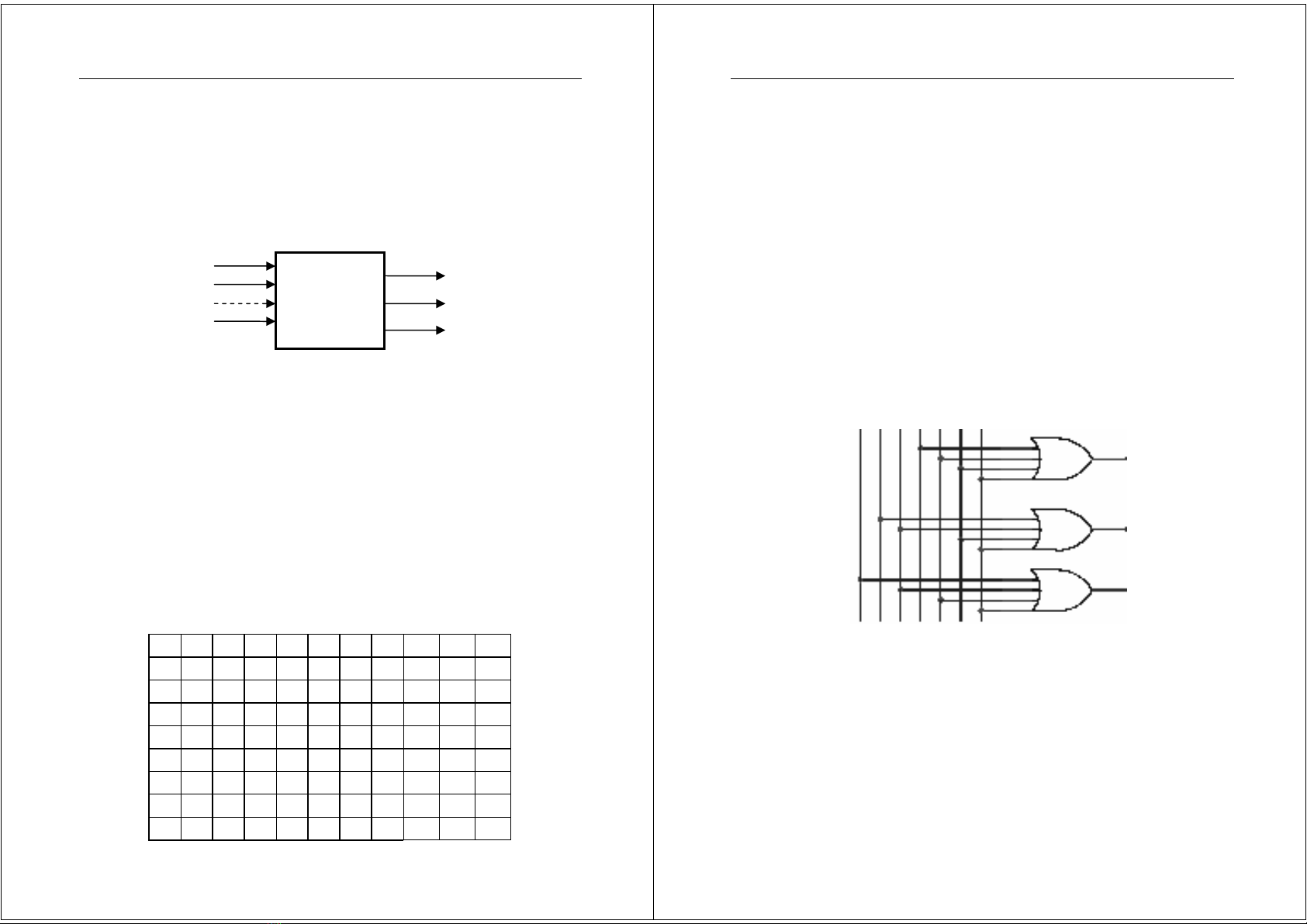

a)M"chmãhoá(Encoder)

Xétm-chmãhóanhphânt`8sang3(8ngõvàovà3ngõ

ra).Sơñykhic+am-chñưZcchotrênhình4.19.

Trongñó:

ox

0

,x

1

,…,x

7

làcácngõvàotínhiDu.

oA

0

,A

1

,A

2

làcácngõra.

M-chmãhóanhphân8

3thGchiDnbi(nñitínhiDungõ

vàothànhmtt`mãnhphântương^ng=ngõra,cmth nhưsau:

0

000 2

100 4

100 6

110

1

001 3

011 5

101 7

111

Ch$nm^ctácñng(tíchcGc)=ngõvàolàm^clogic1,ta

cób*ngtr-ngtháimôt*ho-tñngc+am-chnhưsau:

x

7

x

S

x

T

x

4

x

3

x

2

x

1

x

0

A

2

A

1

A

0

0 0 0 0 0 0 0 1 0 0 0

0 0 0 0 0 0 1 0 0 0 1

0 0 0 0 0 1 0 0 0 1 0

0 0 0 0 1 0 0 0 0 1 1

0 0 0 1 0 0 0 0 1 0 0

0 0 1 0 0 0 0 0 1 0 1

0 1 0 0 0 0 0 0 1 1 0

1 0 0 0 0 0 0 0 1 1 1

ENCODER

8

3

x

0

x

1

x

7

A

0

A

1

A

2

Hình4.19.SơñykhiEncoder8

3

ChươngIV:MchLogics

146

Gi*ithíchb*ngtr-ngthái:Khimtngõvào=tr-ngtháicao

(m^clogic1)vàcácngõvàocònl-ithBp(m^clogic0)thìngõra

xuBthiDnt`mãtương^ng.Ngõvàonào=tr-ngtháicaothìtương

^ngvQiconsñó=hDth!pphân,vídmngõvào4=tr-ngtháicao

s8tương^ngvQis4ñưZcñưavàongõnh!p.Cmth là:khingõ

vàox

0

=1vàcácngõvàocònl-ib\ng0thìt`mã=ngõralà000,

khingõvàox

1

=1vàcácngõvàocònl-ib\ng0thìt`mãnhphân

=ngõralà001,…

Phươngtrìnhlogictigi*n:

A

0

=x

1

+x

3

+x

5

+x

7

A

1

=x

2

+x

3

+x

6

+x

7

A

2

=x

4

+x

5

+x

6

+x

7

Sơ

ñym-chc+aENCODER8

3nhưhình4.20.

x

1

x

2

x

3

x

4

x

5

x

6

x

7

A

2

A

1

A

0

Hình4.20.ENCODER8

3

TươngtGtadfdàngcóth thi(tk(m-chmãhóath!pphân,

dùngmãhóacácst`0ñ(n9sanghDnhphân.TrongtrưWnghZp

nàytacVncó4ñVurañ mãhóañưZcs8(1000)và9(1001).

ChươngIV:MchLogics

147

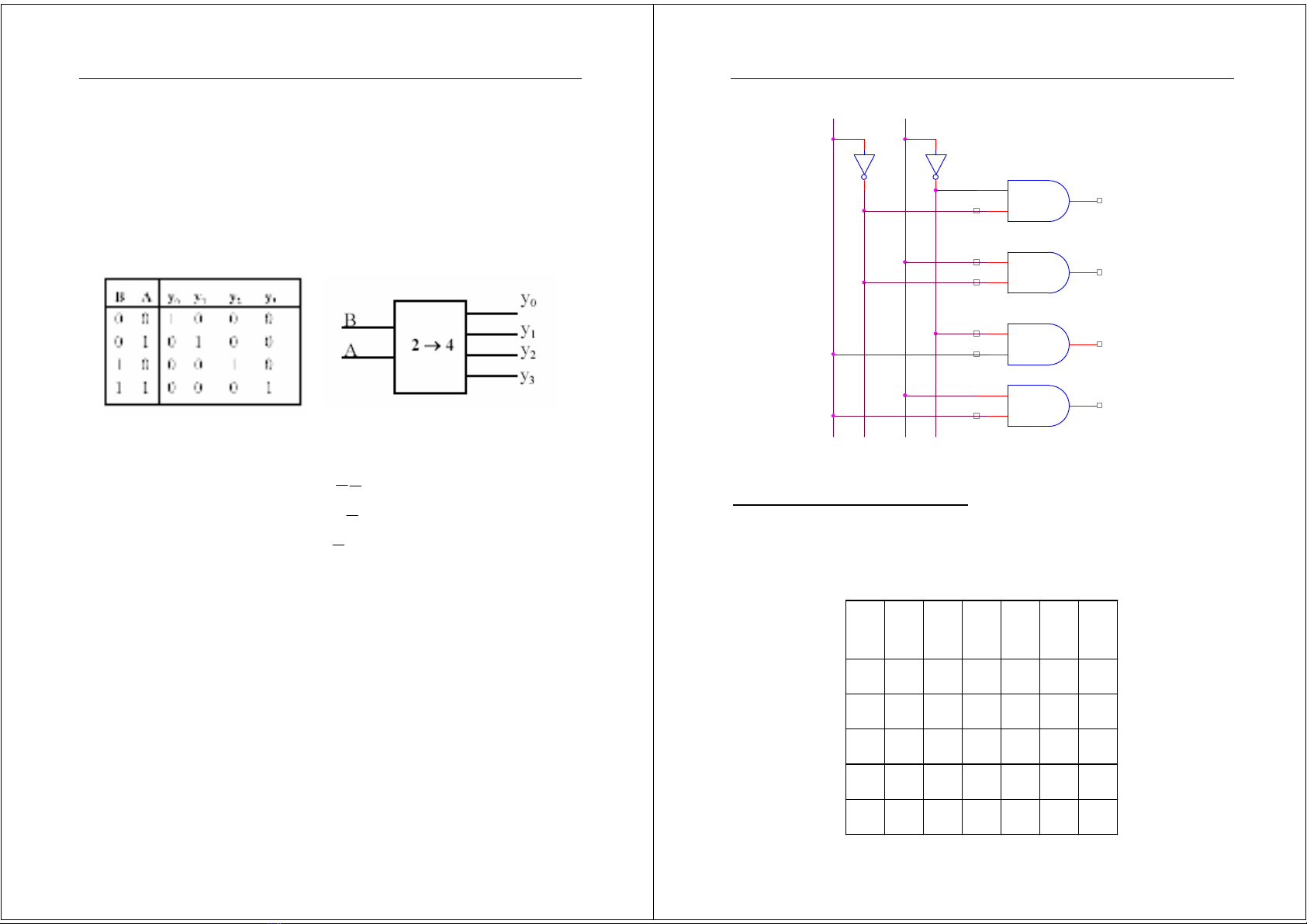

b)M"chgi?imã(Decoder)

NgưZcvQim-chmãhóa,m-chgi*imãlàm-chthZpñi

thôngtinnhphânvQinngõnh!pthành2

n

ngõxuBt.N(ungõnh!p

cómtsthZpkhôngdùngthìsngõracóth íthơn2

n

.Khiñó

m-chgi*imãg$ilàm-chgi*imãnom,vQi

n

m2≤.

ð ñơngi*ntaxétm-chgi*imã2o4vQisơñykhivà

b*ngchântrm-chgi*imãnhphân2

4nhưhình4.21.

Hình4.21.Decoder2

4

T`b*ngchântrtacóphươngtrìnhlogictigi*nchom-ch:

ABy

BAy

BAy

BAy

=

=

=

=

3

2

1

0

Sơñym-chc+aDECODER2

4nhưhình4.22.

M-ch gi*i mã ñưZc ñóng gói thành các vi m-ch và ñưZc

bánratrênthtrưWngthưWngcód-ng4o16,3o8và2o4kép(t^chai

bgi*imãñưZcñóngchungvàotrongmtvim-chñơn).Ngoàira

còn phbi(n bgi*i mã 4o10 dùnggi*i mã s nh phân sang hD

th!pphân.Ngoàicácngõnh!pvàxuBtd<liDuthưWngcòncómt

ngõñiukhi nho-tñngc+am-ch.NgõnàythưWngkýhiDulàE,

khiE=1,chophépm-chho-tñngvàkhiE=0thìkhôngcho

phépm-chho-tñng.

ChươngIV:MchLogics

148

Hình4.22.Sơñym-chDecoder2

4

Mchgi&imãvVicngNAND

Mtsm-chgi*imãñưZct-ot`cngNANDthayvìcng

AND.Nót-orangõxuBttheod-ngñ*ol-i.Hình4.23làm-chgi*i

mã2

4vQicngNANDvQimtñưWngvàoñiukhi nE.Tương

^ngvQinólàB*ngchântrsau:

1

1

1

1

1

1

1

1

x

x

x

x

1

1

0

0

1

1

1

1

1

1

1

1

1

1

0

0

1

1

0

0

1

1

1

1

0

0

1

1

0

0

1

1

1

1

0

0

1

1

1

1

0

0

0

0

1

1

1

1

1

1

0

0

0

0

0

0

0

0

D3

D3

D2

D2

D1

D1

D0

D0

A0

A0

A1

A1

E

E

1

1

1

1

1

1

1

1

x

x

x

x

1

1

0

0

1

1

1

1

1

1

1

1

1

1

0

0

1

1

0

0

1

1

1

1

0

0

1

1

0

0

1

1

1

1

0

0

1

1

1

1

0

0

0

0

1

1

1

1

1

1

0

0

0

0

0

0

0

0

D3

D3

D2

D2

D1

D1

D0

D0

A0

A0

A1

A1

E

E

ChươngIV:MchLogics

149

Hình4.23.M-chgi*imãvQicngNAND

M-chnàyh$atñngkhitínhiDuñiukhi nE=0vàngõra

s8cógiátr0tương^ngvQisnhphân=cácngõvào.KhiE=1

thìkhôngchophépm-chho-tñngt^clàkhôngphmthucvàocác

giátrñVuvào,ñVuraluônb\ng1.

Cácm-chgi*imãngoàithtrưWngthưWngñưZcñónggói

vàcókýhiDunhưhình4.24.ðólà mtm-chgi*mã2

4dùng

cng AND và vQi mt ñưWng ñiu khi n E cho phép m-ch ho-t

ñngkhiE=1vàkhôngho-tñngkhiE=0.

ChươngIV:MchLogics

150

Mr3ngm"chgi?imã

TrongmtstrưWnghZpcVnm-chgi*imãvQimtkínhcO

lQnmàtal-ichcóm-chvQikíchthưQcnh_hơnthìtacóth ghép

haihocnhiuhơncácm-chñangcóñ t-omtm-chmãhóalQn

hơn.Vídmtacóth t-om-chgi*imã3

8t` haim-chgi*i mã

2

4 (hình 4.25). Trong trưWng hZp này ta ñã t!n dmng ngõ vào

ñiukhi nEñ làmngõnh!pth^3.

DECODER

2x4

2

0

2

1

E

D

0

D

1

D

2

D

3

Hình4.24.KýhiDuDecoder2

4

Hình4.25.M-chgi*imã3

8

ChươngIV:MchLogics

151

CÂUHZIVÀBÀIT\PCHƯƠNGIV

1.L!pb*ngchântrvàv8sơñym-chchohàm4bi(nsau:

a)x=AB+A(C+D)

b)y=(A+BC)(D+AB)

c)z=

)( DACBA ++

2.Rútg$ncáchàmsaudùngcácñnhlýc+aBooleanalgebra

a)x=

BCDAACD +

b)y=AB+A(

DCCD +

)

c)z= ))((

DCBADACB ++

3.DùngñnhlýDeMorgan,rútg$nbi uth^csauchoñ(nkhich

cònbi(nñơnñ*o(mtg-chtrên)

z=

)).(( DBCA ++

4.Mtnhàlu!nlýh$cláixevàomttiDmbánñyăn,ngyitrongxe

ông nói: “Làm ơn cho tôi mt bánh Hambuger

hoZc

xúc xích

và

khoaitâychiên”.Ti(cr\ngngưWibánhàngcònchưah$ch(tlQp6

và không bi(t (và không mun bi(t) trong hai t` logic “hoc” và

“và”thìt`nàoñưZcưutiên.Anhtachor\ngtrongtrưWnghZpnày

difngi*ith(nàocũngñưZc.TrongtrưWnghZpnàodưQiñâylàdifn

ñ-tñúngñơnñthàng:

a)ChHambuger

b)Chxúcxích

c)Chkhoaitâychiên

d)Xúcxíchvàkhoaitâychiên

e)Hambugervàkhoaitâychiên

f)Xúcxíchvàhambuger

ChươngIV:MchLogics

152

g)TBtc*3th^

h)Khôngcógì–nhàlu!nlýbñóibmngvìquáthôngminh

5.Mtnhàtruyngiáol-cñưWngt-ingãr8ba=chngd`ngNam

California.Ôngtabi(thaitoánñixemáy=khuvGcnày,mttoán

luônnóith!tvàmttoánluônnóidi.Ôngtamunbi(tñưWngnào

ñitQiDisneylandthìôngtaph*iñtcâuh_inhưth(nào?

6.ð làmmtthi(tbñiukhi nbáoñngtrongxehơi,ngưWita

thi(tk(1m-chbáoñngnhưsau:

TínhiDu:

o

DRV(driver)=m^ccaokhitàix(ngyivàogh(láivà=

m^cthBpkhikhôngngyivào;

o

Bph!nñánhlca:1–b!t,0–tJt;

o

BELT=m^ccaokhitàix(càidâyantoànvà=m^c

thBpkhikhôngcàidâyantoàn.

Hãythi(tk(m-chlogicvQi3ñVuvào(DRV,bph!nñánh

lca,BELT),1ñVura(báoñng),saochobph!nbáoñngs8ho-t

ñng(báoñng=1)khitynt-imttrong2tr-ngtháisau:

o

Tàix(chưangyivàoxetronglúcbph!nñánhlcab!t,

o

Tàix(ñãngyivàoxenhưngchưacàidâyantoàntrong

lúcbph!nñánhlcab!t

L!pb*ngchântrc+ahàmra.

7.ðơngi*ncáchàmsaudùngb*nñyKarnaugh

a)

∑

=

)6,4,3,2,0(),,(

CBAf

b)

∑

=

)15,11,7,5,4,2,1,0(),,,(

DCBAf

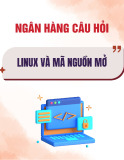

Mch

Logic

DRV

Bph!nñánhlca

BELT

Báoñng

![Bài giảng Phần mềm mã nguồn mở [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250526/vihizuzen/135x160/6381748258082.jpg)

![Tài liệu giảng dạy Hệ điều hành [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250516/phongtrongkim0906/135x160/866_tai-lieu-giang-day-he-dieu-hanh.jpg)

![Bài giảng Hệ điều hành: Trường Đại học Công nghệ Thông tin (UIT) [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250515/hoatrongguong03/135x160/6631747304598.jpg)

![Bài giảng Hệ điều hành Lê Thị Nguyên An: Tổng hợp kiến thức [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250506/vinarutobi/135x160/8021746530027.jpg)

![Bài tập Tin học đại cương [kèm lời giải/ đáp án/ mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251018/pobbniichan@gmail.com/135x160/16651760753844.jpg)

![Bài giảng Nhập môn Tin học và kỹ năng số [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251003/thuhangvictory/135x160/33061759734261.jpg)

![Tài liệu ôn tập Lý thuyết và Thực hành môn Tin học [mới nhất/chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251001/kimphuong1001/135x160/49521759302088.jpg)

![Trắc nghiệm Tin học cơ sở: Tổng hợp bài tập và đáp án [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250919/kimphuong1001/135x160/59911758271235.jpg)

![Giáo trình Lý thuyết PowerPoint: Trung tâm Tin học MS [Chuẩn Nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250911/hohoainhan_85/135x160/42601757648546.jpg)

![Bài giảng Nhập môn điện toán Trường ĐH Bách Khoa TP.HCM [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250806/kimphuong1001/135x160/76341754473778.jpg)