Nguyên lý thit kmch dãy

Nguyn Quc Cưng – 3I

Sequential logic design 2

Ni dung

• Gii thiu

• Các phn thai trng thái nñnh

• Flip-Flops

• Phân tích các máy trng thái ñng bbi xung

nhp

• Thit kcác máy trng thái ñng bbi xung

nhp

Sequential logic design 3

Tài liu tham kho

• Digital Design: Principles & Practices – John F

Wakerly – Printice Hall

Sequential logic design 4

Gii thiu

• M

ch logic dãy:

– output 2 tín hiu input ti thiñim t

n

– output 2 cvào tín hiu input trong quá kh

• Ví d

: m

ch

ñ

i

u khi

n ch

n kênh TV s

d

ng nút b

m

channel–up và channel-down:

– nu trưcñó kênh ñang chn là 9, nu bm channel-up thì kênh

la chn là 10

– nu trưcñó kênh ñang chn là 1, nu bm channel-up thì kênh

la chn là 2

– ...

• Vi

c s

d

ng b

ng

ñ

mô t

các output ph

thu

c vào t

h

p các inputs

ñ

i v

i các m

ch dãy là KHÔNG TH

Sequential logic design 5

Trng thái

• Trong mch dãy sdng khái nim trng thái ñ

mô t:

– Tr

ng thái c

a m

t m

ch dãy là t

p h

p các bi

n

tr

ng thái mà giá tr

c

a nó t

i m

t th

i

ñ

i

m ch

a

ñ

y

ñ

các thông tin c

n thi

t trong quá kh

cho phép

xác

ñ

nh các ho

t

ñ

ng c

a m

ch trong t

ươ

ng lai

– Trong m

ch logic các bi

n tr

ng thái ch

có hai giá tr

0 và 1.

– S

tr

ng thái c

a m

ch có n bi

n tr

ng thái b

ng 2

n

tr

ng thái

Sequential logic design 6

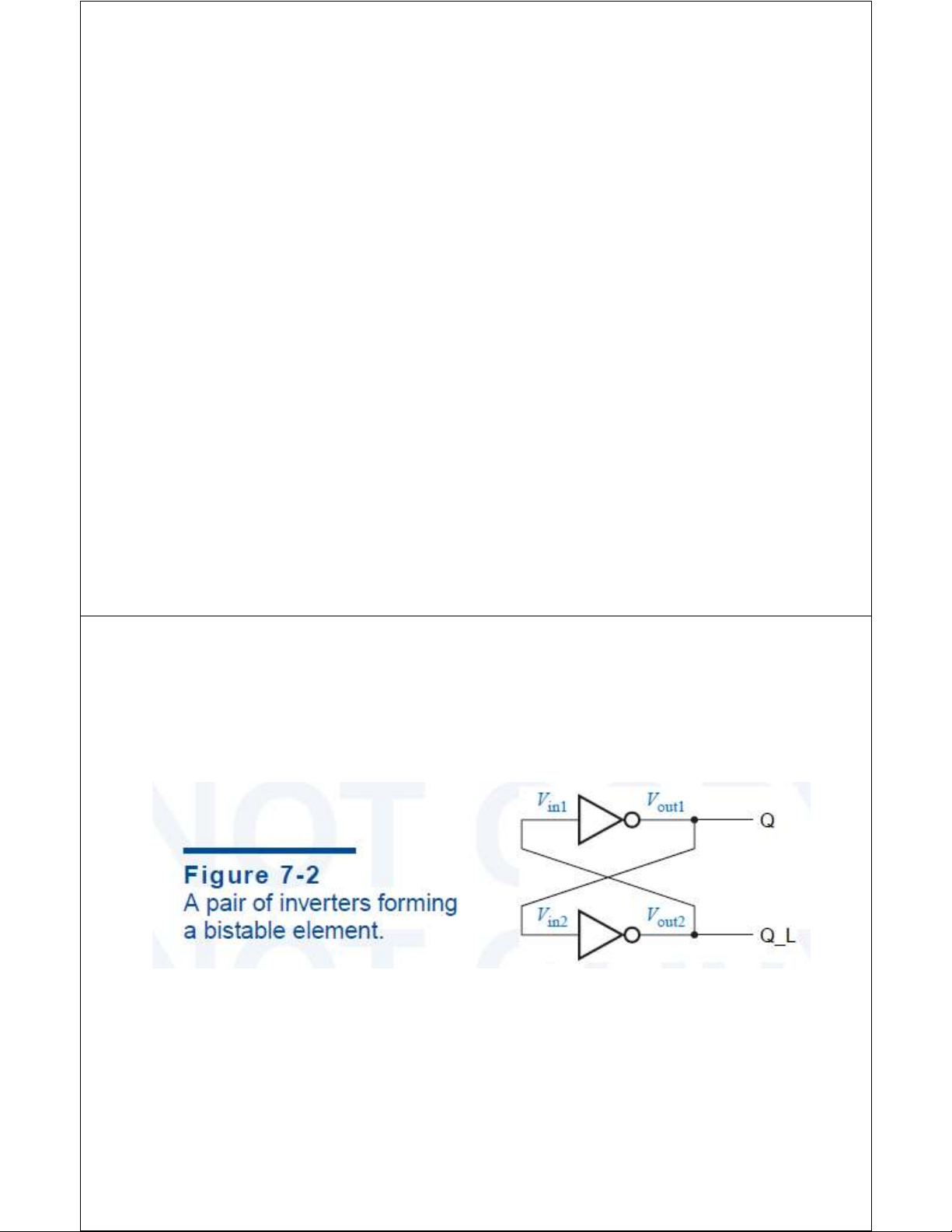

Các phn t2 trng thái nñnh

Mch có hai trng thái nñnh:

• Nu Q = HIGH thì Q_L = LOW

• Nu Q = LOW thì Q_L = HIGH

Sequential logic design 7

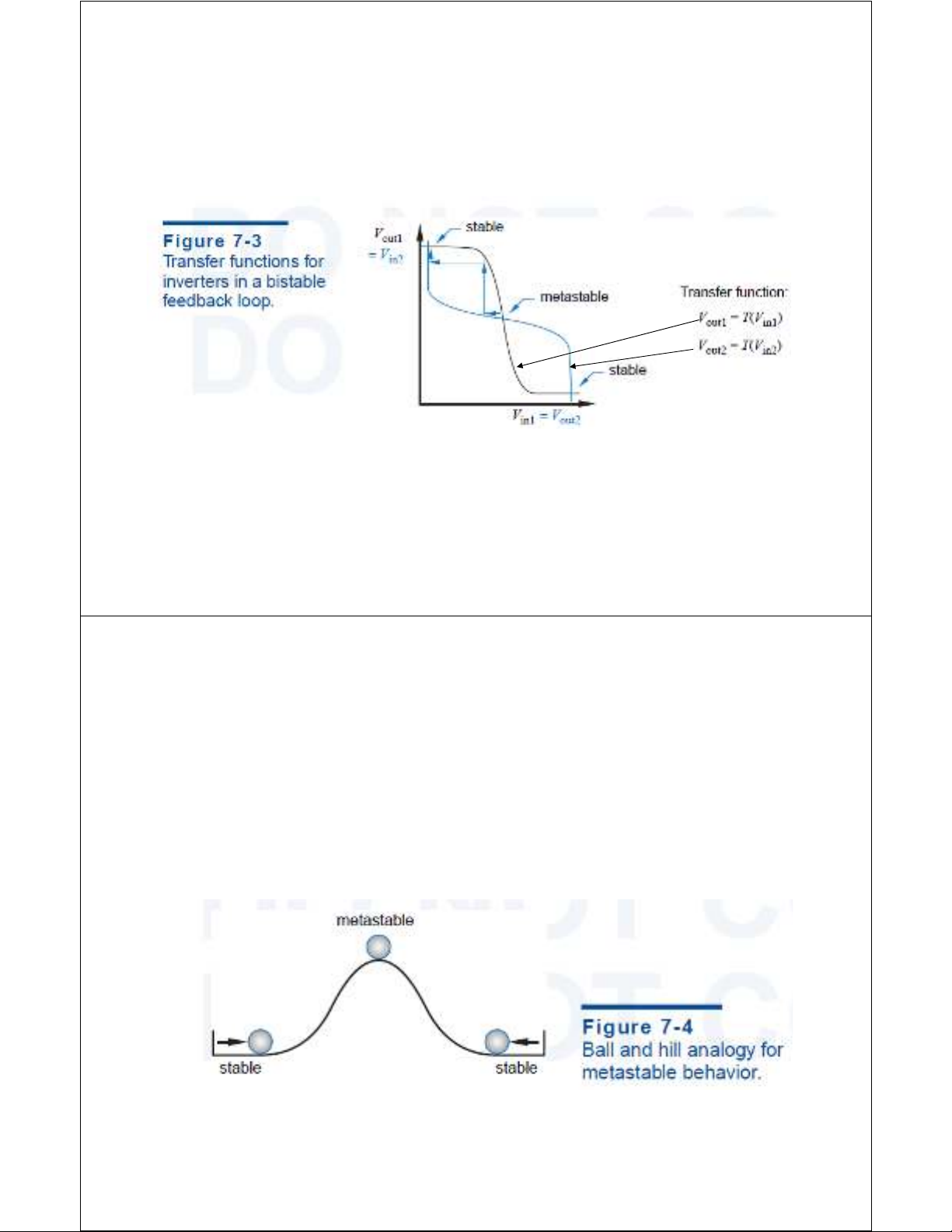

Phân tích tương t

• Xem xét ñin áp V

out

và V

in

Giao ca 2 ñ thti 3 ñimñó là các ñim cân bng ca mch:

• Hai ñimnñnh (ng vi các trng thái Q = 0 ho c Q = 1)

• Mtñim metastable: tiñó V

out1

và V

out2

có giá tr ñin áp nm gi!a mc 1

và 0

Sequential logic design 8

Metastable

• Thc tthi gian mch trng thái metastable

thưng ng"n, lý do, chcn mt tác ñng ñ ln

ca nhiu s#kéo nó vmt trong hai trng thái

stable

Sequential logic design 9

Latch và Flip-Flops

• Latch và Flip-flops là các ph

n t

c

ơ

b

n trong m

ch

logic dãy

• Flip-Flops: dùng

ñ

ch

m

t thi

t b

logic dãy có kh

n

ă

ng

l

y m

%

u tín hi

u

ñ

u vào và thay

ñ

i tín hi

u

ñ

u ra t

i

th

i

ñ

i

m

ñư

c xác

ñ

nh b

i tín hi

u xung nh

p

• Latch: dùng

ñ

ch

thi

t b

logic dãy có kh

n

ă

ng quan

sát tín hi

u inputs m

t cách liên t

c và có th

thay

ñ

i

ñ

u ra c

a nó t

i b

t k

ỳ

th

i

ñ

i

m nào mà không ph

thu

c vào tín hi

u xung nh

p

• Tuy nhiên th

ư

ng 2 khái ni

m này có th

s

d

ng nh

ư

nhau

Sequential logic design 10

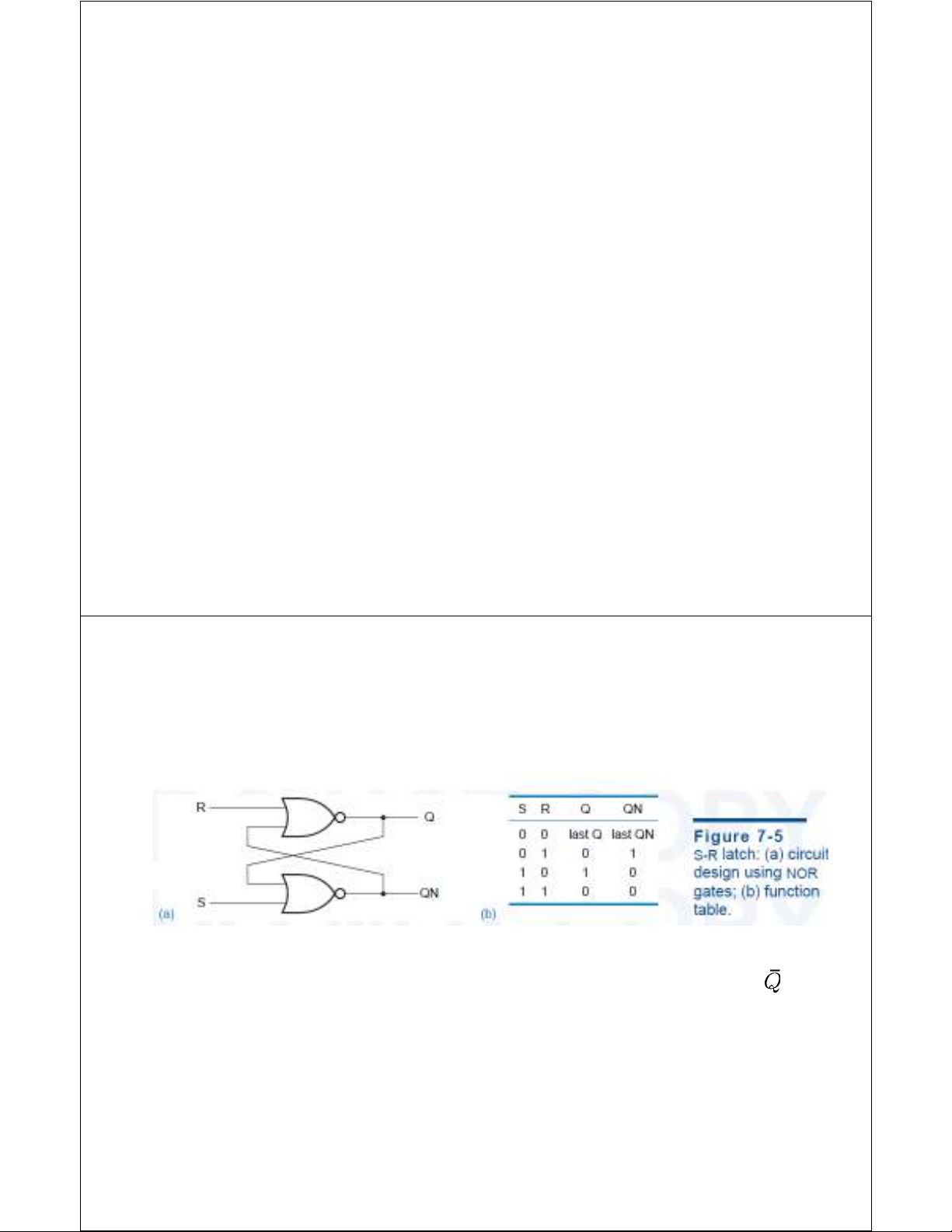

S-R Latch (Flip-flops)

S-R flip-flop: (set-reset)

R = 1, S = 0 Q = 0 (reset) S=1, R=0 Q = 1(set)

QN : thưng là ñu bù ca Q, trong các tài liu còn ñưc ký hiu Q_L hay

Nu R = 0, S = 0 thì mch ging nhưmt phn tbistable

Tuy nhiên trong trng hp S=R=1 thì Q = QN = 0

![Bài giảng công tắc tơ [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260506/vispacex_27/135x160/93891778142285.jpg)

![Giáo trình Điện tử tương tự 1: Phần 1 [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260506/vispacex_27/135x160/69111778210056.jpg)