1

1/Chapter7

N i dung môn h cộ ọ

N i dung môn h cộ ọ

1. Gi i thi u chung v h vi x lýớ ệ ề ệ ử

2. B vi x lý Intel 8088/8086ộ ử

3. L p trình h p ng cho 8086ậ ợ ữ

4. T ch c vào ra d li uổ ứ ữ ệ

5. Ng t và x lý ng tắ ử ắ

6. Truy c p b nh tr c ti p DMAậ ộ ớ ự ế

7. Các b vi x lý trên th c tộ ử ự ế

2

2/Chapter7

Ch ng 7: Các b vi x lý trên th c tươ ộ ử ự ế

Ch ng 7: Các b vi x lý trên th c tươ ộ ử ự ế

•General purpose microprocessors

Intel 80x86

Xu h ng phát tri nướ ể

•Microcontrollers

Vi đi u khi n c a Motorolaề ể ủ

H vi đi u khi n 8051ọ ề ể

H vi đi u khi n AVRọ ề ể

PSOC

Xu h ng phát tri nướ ể

•Digital signal processors

Texas Instruments

Motorola

Philips

Xu h ng phát tri nướ ể

3

3/Chapter7

Ch ng 7: Các b vi x lý trên th c tươ ộ ử ự ế

Ch ng 7: Các b vi x lý trên th c tươ ộ ử ự ế

•General purpose microprocessors

Intel 80x86

Xu h ng phát tri nướ ể

•Microcontrollers

Vi đi u khi n c a Motorolaề ể ủ

H vi đi u khi n 8051ọ ề ể

H vi đi u khi n AVRọ ề ể

PSOC

Xu h ng phát tri nướ ể

•Digital signal processors

Texas Instruments

Motorola

Philips

Xu h ng phát tri nướ ể

4

4/Chapter7

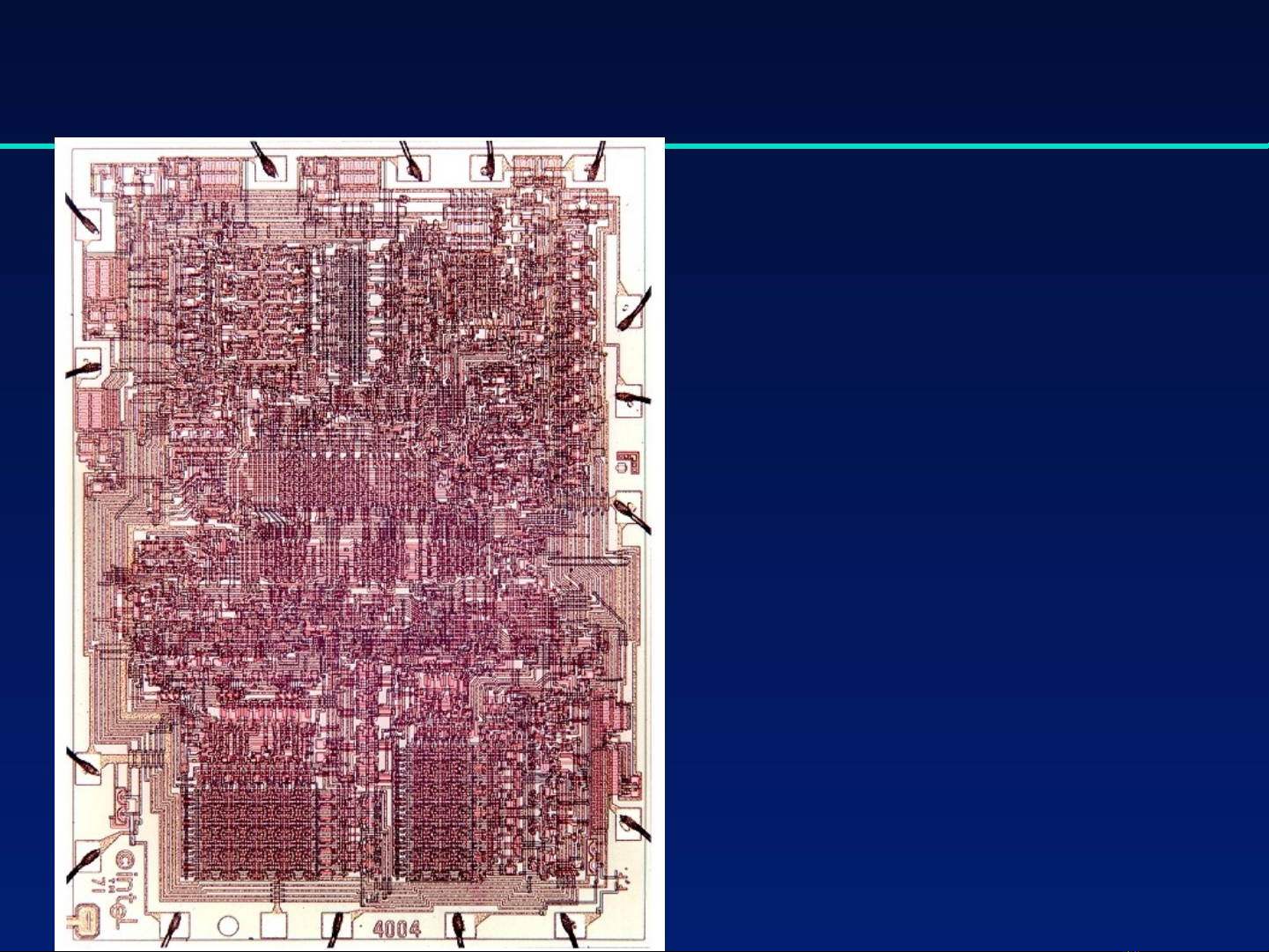

Intel 4004

Intel 4004

•First microprocessor

(1971)

•4-bit processor

•2300 Transistors (P-

MOS), 10 µm

•0.06 MIPS, 108 KHz, 640

bytes addressable

memory

•-15V power supply

5

5/Chapter7

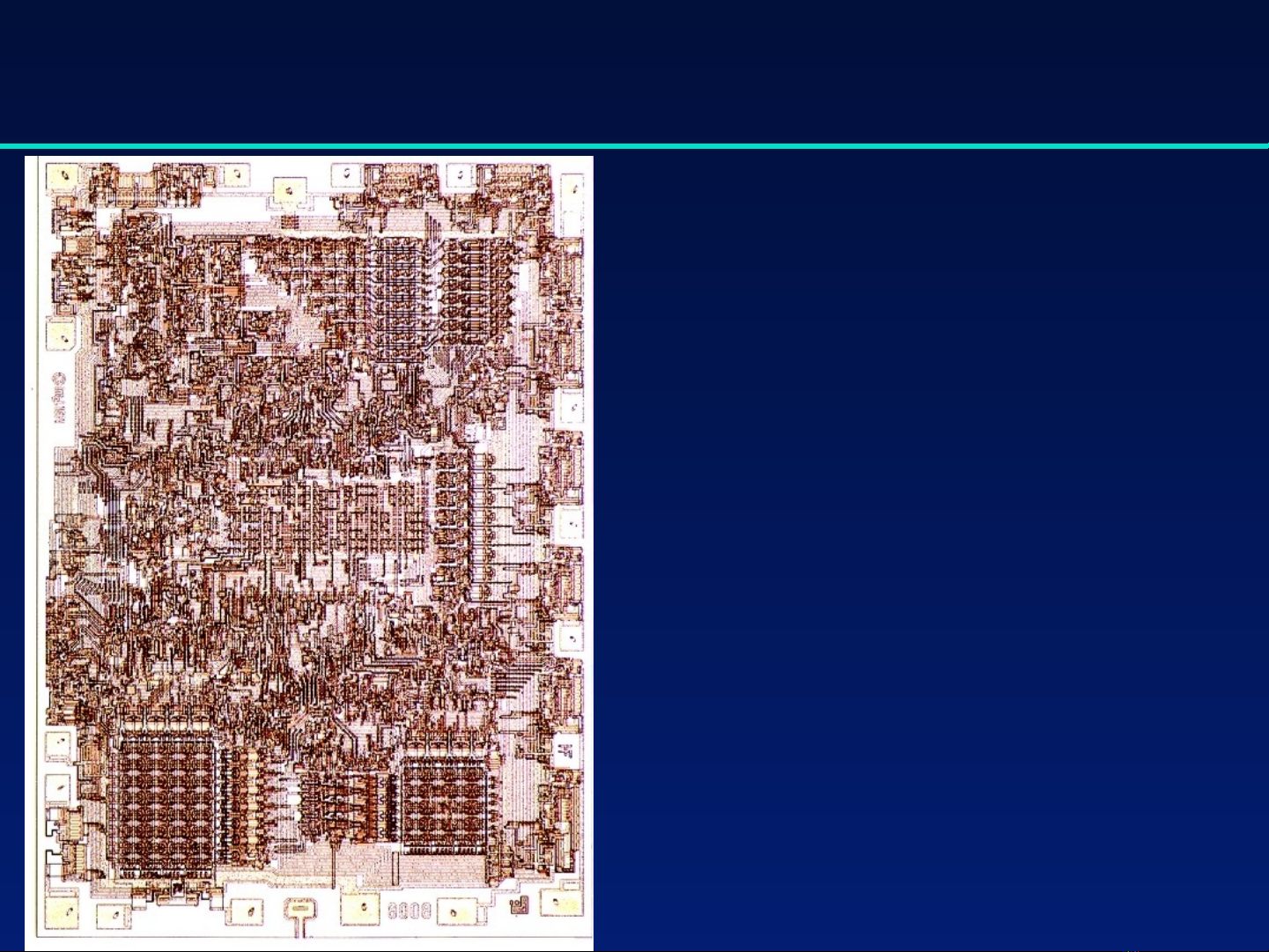

Intel 8008

Intel 8008

•First 8-bit processor (1972)

•Cost $500; at this time, a 4-

bit processor costed $50

•Complete system had 2

Kbyte RAM

•200 KHz clock frequency,

10 µm, 3500 TOR, 0.06

MIPS, 16 Kbyte addressable

memory

•18 pin package, multiplexed

address and data bus