Ạ Ọ

Ệ

Ộ Đ I H C CÔNG NGHI P HÀ N I

KHOA ĐI N TỆ Ử

́

ự

̣ ̣

Th c tâp tôt nghiêp

ứ

ế

ề

ể

ắ

Đ tàiề

: Nghiên c u lý thuy t và l p ráp modul đi u khi n

nhà thông minh

ệ

ướ

ẫ : Lê Vi

ế t Ti n

Giáo viên h

ng d n

ễ

ự

Sinh viên th c hi n

ệ : Nguy n Bách Khoa

1

ệ ử

ớ

L p: CNKT Đi n T 3 Khóa 7

ộ Hà N i 032016

NHẬN XÉT CỦA GIẢNG VIÊN HƯỚNG DẪN

...........................................................................................................................

...........................................................................................................................

...........................................................................................................................

...........................................................................................................................

...........................................................................................................................

...........................................................................................................................

...........................................................................................................................

...........................................................................................................................

...........................................................................................................................

...........................................................................................................................

...........................................................................................................................

...........................................................................................................................

...........................................................................................................................

...........................................................................................................................

...........................................................................................................................

...........................................................................................................................

ộ Hà N i, Ngày……..tháng……..năm 2016

ả ướ ẫ Gi ng viên h ng d n

(Ký và ghi rõ h tênọ )

Lời cảm ơn

Trước tiên em xin gửi lời cảm ơn chân thành sâu sắc tới các thầy

cô giáo trong trường Đại Học Công Nghiệp Hà Nội nói chung và các

thầy cô giáo trong khoa Điện Tử nói riêng đã tận tình giảng dạy, truyền

đạt cho chúng em những kiến thức, kinh nghiệm quý báu trong suốt 4

năm ngồi trên giảng đường qua.

Đặc biệt em xin gửi lời cảm ơn đến thầy Lê Việt Tiến, thầy đã tận

tình giúp đỡ, trực tiếp chỉ bảo, hướng dẫn em trong suốt quá trình làm

thực tập tốt nghiệp. Trong thời gian làm việc với thầy, em không ngừng

tiếp thu thêm nhiều kiến thức bổ ích mà còn học tập được tinh thần làm

việc, thái độ nghiên cứu khoa học nghiêm túc, hiệu quả, đây là những

điều rất cần thiết cho em trong quá trình học tập và công tác sau này.

Sau cùng em xin gửi lời cảm ơn chân thành tới gia đình, bạn bè

đã động viên, đóng góp ý kiến và giúp đỡ trong quá trình học tâp,

nghiên cứu và hoàn thành thực tập tốt nghiệp.

Đề tài này được hoàn thành không thể tránh khỏi những thiếu sót

nhất định. Em mong nhận được sự góp ý quý báu của các thầy cô giáo

và các bạn.

Em xin chân thành cảm ơn.

3

Hà Nội 03-2016

Mục lục

Bảng ký hiệu viết tắt

ả

Ký hi uệ

Vi

ế ầ ủ t đ y đ

Gi

i thích

ề

ể

VĐK

Vi Đi u Khi n

ả

PIC

Máy tính kh trình thông minh

Programmable Intelligent Computer

ộ ử

CPU

Central Processing Unit

B x lý trung tâm

ộ

ROM

Readonly Memory

ớ ỉ ọ B nh ch đ c

ẫ

ộ

ớ

RAM

Random Access Memory

ậ B nh truy c p ng u nhiên

ƯƠ Ớ Ệ Ề CH NG 1 : GI I THI U Đ TÀI

I.

ơ ở ế C s lý thuy t

ộ ố ườ ượ ữ ầ Khi cu c s ng con ng i càng đ ộ ố c nâng cao, nh ng nhu c u cu c s ng

ỏ ừ ữ ự ế ầ ngày càng đòi h i ph i đ ả ượ ỗ ợ ố ơ c h tr t t h n. Và t nh ng nhu c u th c t đó

ưở ề ộ ự ấ ủ ơ ý t ng v m t ngôi nhà thông minh mà n i đó ngoài s m áp c a tình yêu

ạ ộ ủ ọ ườ ề ượ ỗ ợ ạ h nh phúc, m i ho t đ ng c a con ng i đ u đ ỡ ộ c h tr và giúp đ m t

ữ ạ ượ ỡ ự ộ ả cách linh ho t, không nh ng đ c giúp đ mà ngôi nhà còn t đ ng qu n lý

ộ m t cách thông minh

ớ ự ẽ ượ ậ ủ ể ạ ọ ỹ Ngày nay v i s phát tri n m nh m v ậ t b c c a khoa h c k thu t,

ệ ự ủ ể ề ể ưở ề ộ ặ đ c bi t là s phát tri n c a vi đi u khi n thì ý t ng v m t ngôi nhà

ướ ệ ả ở thông minh không còn v ng b i rào c n công ngh . Khi đó con ng ườ ẽ i s

ẽ ượ ủ ả ơ có c m giác an toàn h n khi ngôi nhà c a chúng ta s đ ợ ủ c tích h p c a các

ư ệ ố ể ườ ệ ố ề ệ ố h th ng nh h th ng đi u khi n và giám sát môi tr ả ng: h th ng đ m

ệ ộ ệ ố ề ể ả ạ ả ắ ỏ b a nhi t đ , h th ng đ m b o ánh sáng…, m ch đóng ng t, đi u khi n ra

ộ ệ ố ả ạ ấ ố vào, giám sát c nh báo cháy…, thành m t h th ng m ng th ng nh t.

II.

5

ự ễ Ý nghĩa th c ti n

ậ ợ ủ ể ủ ứ ệ Chúng ta không th ph nh n l ể i ích c a vi c nghiên c u và phát tri n

ớ ờ ố ệ ạ ạ ệ ả nhà thông minh t i đ i s ng hi n t i, nó mang l i tính ti n nghi, tho i mái,

ấ ả ằ ề ọ ộ ố sang tr ng, an toàn cho cu c s ng nhi u âu lo, v t v h ng ngày. Không

ữ ậ ả ế ệ ồ ượ nh ng v y nhà thông minh còn là gi i pháp ti t ki m ngu n năng l ng, đang

ề ấ ọ ầ là v n đ làm đau đ u các nhà khoa h c.

ườ ẽ ộ ố ố ẹ ề ơ Con ng i s có cu c s ng t ả t đ p h n, không ph i dành quá nhi u tâm

ệ ả ườ ể ờ ờ trí trong vi c qu n lý ngôi nhà, mà con ng i có th dành th i gi ề cho nhi u

ư ươ ệ ầ ươ ậ ệ ữ ướ vi c khác. Chúng ta g n nh t ng tác đ c nh ng v t li u mà tr c đây

ư ể ầ g n nh là không th .

ủ ớ ộ Và ngôi nhà c a chúng ta cũng có m t cái nhìn hoàn toàn m i, th c s nh ự ự ư

ộ ậ ể ự ậ ụ ụ ể ườ ờ m t v t th t v n hành đ ph c v con ng i. Gi đây ta hoàn toàn hãnh

ể ệ ệ ệ ệ ẳ ạ ớ ấ ủ ự di n v i ngôi nhà th hi n d ng c p c a s chuyên nghi p, hi n đ i, phong

ấ ứ ặ ậ ầ ư ố ớ cách mà b t c đ c tr ng nào ta mu n có. V i tiêu chí đó khóa lu n l n này

ự ề ẽ ế ế ể ệ ộ em s trình vày v cách xây d ng và thi ề t k modul đi u khi n nhi t đ và

ánh sáng trong nhà thông minh.

ƯƠ Ọ Ụ Ề Ể CH NG 2 : CÁC H VI ĐI U KHI N THÔNG D NG

ề ượ ợ Vi đi u khi n ể là m tộ máy tính đ c tích h p trên m t ộ chíp, nó th ngườ

ượ ử ụ ể ự ề ấ đ ể ề c s d ng đ đi u khi n các thi ế ị ệ ử t b đi n t ể . Vi đi u khi n, th c ch t, là

ộ ệ ố ệ ồ m t h th ng bao g m m t ấ ộ vi x lýử có hi u su t đ dùng và giá thành th p ấ ủ

ế ợ ử ớ ộ ớ ố (khác v i các b vi x lý đa năng dùng trong máy tính) k t h p v i các kh i

ạ ộ ớ ổ ố ế ngo i vi nh ư b nh , các mô đun vào/ra, các mô đun bi n đ i s sang t ươ ng

ự ươ ự ố Ở ườ ượ t và t ng t sang s ,... máy tính thì các mô đun th ng đ ự c xây d ng

ạ ở b i các chíp và m ch ngoài.

ể ề ườ ượ ự ể ệ ố Vi đi u khi n th ng đ c dùng đ xây d ng các h th ng nhúng . Nó

ệ ề ấ ụ xu t hi n khá nhi u trong các d ng c đi n t ụ ệ ử, thi ế ị ệ máy gi t b đi n, tặ , lò vi

ầ ế ị ươ ệ sóng, đi n tho i ọ ạ , đ u đ c DVD ,thi t b đa ph ng ti n ệ , dây chuy n t ề ự ộ , đ ng

v.v.

(do tập đoàn "Applied Micro Circuits

ệ ề ể ọ Các h vi đi u khi n hi n nay:

ọ ề ể H vi đi u khi n AMCC

ể ề ọ Corporation" sản xuất). Từ tháng 5 năm 2004, h vi đi u khi n này đ ượ c

ị ườ ể phát tri n và tung ra th tr ng b i ở IBM.

+ 403 PowerPC CPU + PPC 403GCX

ể ọ ề

H vi đi u khi n Atmel + Dòng 8051 (8031, 8051, 8751, 8951, 8032, 8052, 8752, 8952) + Dòng Atmel AT91 (Kiến trúc ARM THUMB)

ọ ể ề H vi đi u khi n Cypress MicroSystems

+ CY8C2xxxx (PSoC)

ọ ề ể ừ ữ H vi đi u khi n Freescale Semiconductor . T năm 2004, nh ng vi

ề ượ ị ườ ể ể đi u khi n này đ c phát tri n và tung ra th tr ng b i ở Motorola.

+ Dòng 8bit

ể ề ọ

ề ể ọ

ọ ề ể

7

H vi đi u khi n Fujitsu + F²MC Family (8/16 bit) + FR Family (32 bit) + FRV Family (32 bit RISC) H vi đi u khi n Intel + Dòng 8bit + Dòng 16bit + Dòng 32bit H vi đi u khi n Microchip ử ữ ệ + PIC 8bit (x lý d li u 8bit, 8bit data bus) ữ ệ ử + PIC 16bit (x lý d li u 16bit)

ử

ữ ệ + PIC 32bit (x lý d li u 32bit): PIC32MX ọ ề ụ ề ể Trong bài báo cáo này em xin trình bày v 3 h vi đi u khi n thông d ng và

ượ ườ ử ụ ệ ấ ọ ồ đ ề c nhi u ng i s s ng nh t hi n nay là: H VĐK 8051 (bao g m vđk

ọ ọ 8051, 8052, 8031) , h VĐK PIC ( PIC16F877A) và h VĐK AVR.

I.

ọ ể ề H vi đi u khi n 8051

1. Vi đi u khi n 8051

ể ề

a. Tóm t

ắ ề ị ử ủ t v l ch s c a 8051

ớ ộ ố ộ ệ ể ề ượ Vào năm 1981 hãng Intel gi i thi u m t s b vi đi u khi n đ ọ c g i

ề ể ộ là 8051. B vi đi u khi n này có 128 byte RAM, 4K byte ROM trên chíp, hai

ề ộ ố ế ộ ổ ờ ổ ộ ị b đ nh th i, m t c ng n i ti p và 4 c ng (đ u r ng 8 bit) vào ra t ấ ả ượ c t c đ

ấ ộ ượ ệ ố ộ ‟ ặ đ t trên m t chíp. Lúc y nó đ c coi là m t „h th ng trên chíp . 8051 là

ộ ộ ử ẻ ệ ớ ỉ m t b x lý 8 bit có nghĩa là CPU ch có th làm vi c v i 8 bit d li u t ữ ệ ạ i

ữ ệ ớ ể ộ ờ ơ ƣợ ữ ệ m t th i đi m. D li u l n h n 8 bit đ c chia ra thành các d li u 8 bit đ ể

ử ấ ả ổ ộ cho x lý. 8051 có t ẽ ỗ ổ t c 4 c ng vào ra I/O m i c ng r ng 8 bit (hình v ).

ự ạ ư ặ ộ ả M c dù 8051 có m t ROM trên chíp c c đ i là 64Kbyte, nh ng các nhà s n

ấ ưở ấ ỉ ớ xu t lúc đó đã xu t x ng ch v i 4Kbyte Rom trên chíp.

ổ ế ả ấ ở 8051 đã tr nên ph bi n sau khi Intel cho phép các nhà s n xu t khác

ấ ỳ ạ ủ ể ấ ả ọ ớ ế nhau s n xu t và bán b t k d ng bi n th nào c a 8051 mà h thích v i

ả ể ạ ề ệ ươ ẫ ớ ọ đi u ki n h ph i đ l i mã t ế ự ề ng thích v i 8051. Đi u này d n đ n s ra

ả ủ ề ố ộ ượ ớ ờ đ i nhi u phiên b n c a 8051 v i các t c đ khác nhau và dung l ng Rom

ề ế ể ề ặ ọ trên chíp khác nhau. Đi u này quan tr ng là m c dù có nhi u bi n th khác

ủ ộ ượ ư ớ ề ố nhau c a 8051 v t c đ và dung l ng nh ROM trên chíp nh ng t ấ ả t c

ề ươ ề ệ ề ầ ớ chúng đ u t ng thích v i 8051 ban đ u v các l nh. Đi u này có nghĩa là

ế ươ ẽ ả ạ ộ ế n u ta vi t ch ớ ng trình cho m t phiên b n nào đó thì nó cũng s ch y v i

ấ ỳ ả ọ ệ ừ ả ấ m i phiên b n b t k khác mà không phân bi t nó t hãng s n xu t nào.

.

ặ

ố ượ

Đ c tính

S l

ng

ROM trên chip

RAM

ộ ị

ờ

B đ nh th i

4Kbyte 128 byte 2 32 1 6

Các chân vào ra

ố ế

ổ

C ng n i ti p

ồ ắ Ngu n c t

ả ầ ặ ủ . Các đ c tính c a 8051 đ u tiên B ng 2.1

ộ ề ủ ọ ệ ể

ầ B vi đi u khi n 8051 là thành viên đ u tiên c a h 8051, hãng Intel ký hi u nó là MSC51.

ơ ồ b. S đ chân

9

ơ ồ Hình 2.1 S đ chân 8051

ấ ổ T ừ hình 2.1. ta th y trong 40 chân có 32 chân dùng cho các c ng P0, P1,

ỗ ổ ớ ạ ồ P2, P3 v i m i c ng có 8 chân. Các chân còn l ấ i dành cho ngu n Vcc, đ t

ở ộ ộ ạ GND, các chân dao đ ng XTAL1 và XTAL2, kh i đ ng l i RST cho phép

ắ ấ ƣơ ố ị ỉ ch t đ a ch ngoài EA , cho ng t c t ch ng trình PSEN . Trong 8 chân này thì

ƣợ ọ 6 chân Vcc, GND, XTAL1, XTAL2, RST và EA đ c các h 8031 và 8051 s ử

ả ượ ố ể ệ ố ụ d ng. Hay nói cách khác là chúng ph i đ ệ c n i đ cho h th ng làm vi c

ầ ế ộ ộ ọ ể ề mà không c n bi t b vi đi u khi n thu c h 8051 hay 8031. Còn chân PSEN

ượ ử ụ ệ ố ự và chân ALE đ c s d ng trong các h th ng d a trên 8031.

ươ ứ ớ ố ố + Chân Vcc và chân GND t ng ng v i chân s 40 và chân s 20 cung

ồ ố ấ c p ngu n (+5V) và n i mass

ộ ộ + Chân XTAL1 (chân 19) và XTAL2 (chân 18): 8051 có b dao đ ng

ể ạ ư ầ ộ ồ ồ trên chíp nh ng nó yêu c u có m t xung đ ng h ngoài đ ch y nó. B ộ

ạ ộ ượ ố ớ dao đ ng th ch anh đ c n i v i XTAL1 và XTAL2 cùng hai t ụ ệ đi n

ị có giá tr 30pF

ầ ậ ố + Chân RST: Chân s 9 là chân tái l p RESET. Nó là chân đ u vào có

ứ ự ấ ớ ề m c tích c c cao. Khi c p xung cao t ể ộ i chân này thì b vi đi u khi n

ạ ộ ư ự ế ể ậ ọ ậ ẽ s tái l p và k t thúc m i ho t đ ng. Nó có th coi nh s tái b t

ngu n.ồ

ậ ố ỏ ớ ộ + Chân EA (là chân IN): Truy c p b nh ngoài, chân s 31 trên v chíp

ư ặ ượ ố ớ ồ nh 8751, 89C51 ho c DS5000 thì chân EA đ c n i v i ngu n Vcc.

ườ ư ợ Tr ng h p không có ROM trên chíp nh 8031 và 8051 thì mã ch ươ ng

ớ ượ trình đ ượ ư ấ ở ộ c l u c t b nh ngoài, khi đó chân EA đ ố ấ c n i đ t. Nh ư

ậ v y chân này không bao gi ờ ượ ể ở c đ h . đ

ứ ư ƣơ + Chân PSEN là chân có ch c năng cho phép l u ch ng trình. Ở ệ h

ố ươ ấ ở ộ ớ th ng 8031, khi ch ng trình c t b nh ROM ngoài thì chân này

ủ đ ượ ố ớ c n i t i chân OE c a ROM.

ố ị ứ ự ố ỉ + ALE cho phép ch t đ a ch là chân có m c tích c c cao. Khi n i 8031

ớ ộ ớ ổ ượ ấ ữ ệ ị ỉ t i b nh ngoài thì c ng 0 cũng đ c c p đ a ch và d li u. Hay nói

ữ ệ ể ế ồ ổ ị ệ ỉ cách khác, 8031 d n đ a ch và d li u qua c ng 0 đ ti ố t ki m s chân.

ượ ử ụ ữ ệ ể ằ ỉ Chân ALE đ ị c s d ng đ phân kênh đ a ch và d li u b ng cách

ủ ủ ố ớ n i t i chân G c a c a chíp 73LS373.

ề ổ ố ổ + Nhóm chân c ng vào ra I/O: b n c ng P0, P1, P2, P3 đ u có 8 chân

ề ượ ấ ạ ổ ổ ấ ả và t o thành c ng 8 bít. T t c các c ng khi RESET đ u đ c c u hình

ầ ượ ậ ể ầ ổ làm c ng ra. Đ làm đ u vào thì c n đ c l p trình.

ổ ổ ườ ể ừ

ổ ầ ừ ổ ừ

ở ệ ả ượ ừ ế chân 32 đ n 39 ph i đ ổ

ầ ế ặ

ệ ở

ổ ở ệ

ể ử ụ ổ ầ ặ

ầ ổ

ế ổ ổ

ở ể ử ụ ừ ặ ư ầ

ệ ở ầ ng là c ng ra. C ng P0 có th v a làm đ u Các c ng bình th ố ra, v a làm đ u vào c ng P0 t c n i ớ chân v i đi n tr kéo 10K bên ngoài. C ng P1 cũng có 8 chân, t ớ ể ử ụ 1 đ n chân 8, và có th s d ng làm đ u vào ho c ra. Khác v i ế ầ ổ c ng P0, c ng P1 không c n đ n đi n tr kéo bên ngoài vì nó đã ế ừ chân 21đ n có đi n tr kéo bên trong. C ng P2 cũng có 8 chân t ư ổ ố 28, và có th s d ng làm đ u vào ho c ra. Cũng gi ng nh c ng ệ ở ệ P1, c ng P2 không c n đi n tr kéo vì bên trong đã có các đi n chân 10 đ n chân 17. C ng này có tr kéo. C ng P3 có 8 chân t ổ th s d ng làm đ u vào ho c ra. Cũng nh chân P1và P2, c ng ầ P3 cũng không c n đi n tr kéo.

ứ

ổ Bít c ng P3

Ch c năng

Chân số

ậ ữ ệ ữ ệ

ậ ữ ệ ữ ệ

ắ ắ ộ ị ộ ị

ờ ờ

ắ ắ ộ ị ộ ị

ờ ờ

ọ

ọ

P3.0 P3.1 P3.2 P3.3 P3.4 P3.5 P3.6 P3.7

Nh n d li u (RXD) Phát d li u (TXD) Ng t 0(INT0) Ng t 1(INT1) B đ nh th i 0 (TO) B đ nh th i 1(T1) Ghi (WR) Đ c (RD)

Nh n d li u (RXD) Phát d li u (TXD) Ng t 0(INT0) Ng t 1(INT1) B đ nh th i 0 (TO) B đ nh th i 1(T1) Ghi (WR) Đ c (RD)

11

ả ứ ổ . Ch c năng các chân c ng P3. B ng 2.2

ủ ọ ề ể ộ Có hai b vi đi u khi n thành viên khác c a h 8051 là 8052 và 8031.

c. T ch c b nh

ổ ứ ộ ớ

ề ề ể ộ ọ ổ ứ Các vi đi u khi n thu c h 8051 đ u t ch c thành 2 không gian

ươ ẽ ả ề ế ch ng trình và d li u, đi u này. Ki n trúc vi ữ ệ hình 2.2 và hình 1.3 s mô t

ủ ử ậ ơ ố ớ x lý 8 bit c a 8051 này cho phép truy nh p và tính toán nhanh h n đ i v i

ờ ệ ữ ệ ớ ươ ộ không gian d li u nh vi c phân chia 2 không gian b nh ch ng trình và

ữ ệ ư ộ ớ ượ ở ệ ố ậ d li u nh trên. Tuy nhiên b nh ngoài đ c truy nh p b i h th ng 16 bit

ể ự ỉ ẫ ờ ỏ ệ ị đ a ch v n có th th c hi n nh thanh ghi con tr .

ớ ộ ươ ỉ ọ ộ ớ B nh ch ng trình (ROM, EPROM) là b nh ch đ c, có th m ể ở

ố ớ ọ ớ ươ ể ộ ộ r ng t ề i đa 64Kbyte. V i h vi đi u khi n 89xx, b nh ch ng trình đ ượ c

ẵ ợ ướ ấ ỏ ớ tích h p s n trong chip có kích th ề c nh nh t là 4kByte. V i các vi đi u

ợ ẵ ớ ươ ể ộ ả ộ khi n không tích h p s n b nh ch ng trình trên chip, bu c ph i thi ế ế t k

ớ ươ ụ ử ụ ộ b nh ch ng trình bên ngoài. Ví d s d ng EPROM: 2764 (64Kbyte), khi

ả ở ứ ự đó chân PSEN ph i m c tích c c (5V).

ấ ươ ể ề ng trình vi đi u khi n 89C51 Hình 2.2: C u trúc ch

ớ ữ ệ ồ ạ ộ ậ ớ ộ ớ ươ ộ B nh d li u (RAM) t n t i đ c l p so v i b nh ch ng trình. H ọ

ớ ữ ệ ể ề ấ ộ ợ ỏ vi đi u khi n 8051 có b nh d li u tích h p trên chip nh nh t là 128byte

ể ở ộ ớ ữ ệ ớ ộ ớ ữ và có th m r ng v i b nh d li u ngoài lên t ớ i 64kByte. V i nh ng vi

13

ề ể ẫ ợ đi u khi n không tích h p ROM trên chip thì v n có RAM trên chip là

ữ ệ ử ụ ệ ọ ờ 128byte. Khi s d ng RAM ngoài, CPU đ c và ghi d li u nh tín hi u trên

ử ụ ả ộ ớ ươ các chân RD và WR. Khi s d ng c b nh ch ớ ữ ệ ộ ng trình và b nh d li u

ả ế ợ ở ổ ộ bên ngoài thì bu c ph i k t h p chân RD và PSEN b i c ng logic AND đ ể

ệ ấ ữ ệ ệ phân bi t tín hi u truy xu t d li u trên ROM hay RAM ngoài.

ớ ươ ắ ộ ị ỉ ng trình Hình 2.3: Đ a ch các ng t trên b nh ch

ả ấ ớ ươ ộ ở ộ c u trúc b nh ch ng trình. Sau khi kh i đ ng, CPU Hình 2.2 mô t

ệ ươ ở ị ả ị ự ắ ầ b t đ u th c hi n ch ng trình v trí 0000H. ắ ỉ đ a ch ng t Hình 2.3 mô t

ặ ị ớ ươ ộ ỏ ủ ắ ả ố m c đ nh trên b nh ch ng trình. M i khi x y ra ng t, con tr c a CPU s ẽ

ắ ươ ế ả ỉ ị ự ứ ươ ạ nh y đ n đúng đ a ch ng t t ng ng và th c thi ch ng trình t i đó. Ví d ụ

ẽ ắ ắ ả ị ỉ ng t ngoài 0 s có đ a ch là 0003H, khi x y ra ng t ngoài 0 thì con tr ỏ

ươ ể ự ế ẽ ả ỉ ươ ch ị ng trình s nh y đ n đúng đ a ch 0003H đ th c thi ch ng trình t ạ i

ế ươ ụ ứ ế ắ đó. N u trong ch ị ử ụ ng trình ng d ng không x d ng đ n ng t ngoài 0 thì đ a

ử ụ ể ẫ ộ ỉ ụ ch 0003H v n có th dùng cho m c đích khác (s d ng cho b nh ch ớ ươ ng

trình).

ấ ộ ớ ữ ệ Hình 2.4: C u trúc b nh d li u

ả ấ ớ ữ ệ ớ ữ ệ ộ ộ c u trúc b nh d li u trong và b nh d li u ngoài Hình 2.4 mô t

ề ể ẽ ế ọ ủ c a h vi đi u khi n 8051. CPU s dùng đ n các chân RD và WR khi truy

ớ ữ ệ ế ộ ậ c p đ n b nh d li u ngoài.

ả ấ ộ ượ ớ ữ ệ c u trúc b nh d li u trong chip, đ c chia thành 3 Hình 2.5 mô t

ấ ặ ố ệ kh i là 128 byte th p, 128 byte cao và 128 byte đ c bi t.

ấ ớ ộ Hình 2.5: C u trúc b nh trong

ứ ị ượ ị ị bit đ ỉ c đ nh đ a ch trong đó 128 ứ bit ch a trong 8051 ch a 210 v trí

ở ị ỉ ừ ế ầ các byte đ a ch t 20H đ n 2FH (16 byte x 8 bit = 128 bit) và ph n còn l ạ i

15

ứ ặ ệ ậ ch a trong các thanh ghi đ c bi t. Ngoài ra 8051 còn có các ấ port xu t/nh p có

ể ị ế ệ ề ằ ả ơ ị th đ nh đ a ch t ng ầ ỉ ừ bit, đi u này làm đ n gi n vi c giao ti p b ng ph n

ề ế ị ậ ấ ớ m m v i các thi t b xu t/nh p đ n ơ bit.

ặ ở ị ỉ ừ ụ ế Vùng RAM đa m c đích có 80 byte đ t đ a ch t 30H đ n 7FH, bên

ướ ừ ị ế ớ ỉ d i vùng này t đ a ch 00H đ n 2FH là vùng nh có th đ ể ượ ử ụ c s d ng

ươ ự ấ ỳ ị ụ ề ớ t ng t . B t k v trí nh nào trong vùng RAM đa m c đích đ u có th ể

ượ ấ ự ử ụ ỉ ự ế ằ ị ị đ c truy xu t t ặ ể do b ng cách s d ng các ki u đ nh đ a ch tr c ti p ho c

gián ti p.ế

ấ ỳ ị ụ ề ớ B t k v trí nh nào trong vùng RAM đa m c đích đ u có th đ ể ượ c

ấ ự ử ụ ỉ ự ế ằ ị ị truy xu t t ặ ể do b ng cách s d ng các ki u đ nh đ a ch tr c ti p ho c

gián ti p.ế

ừ ứ ế ư Cũng nh các thanh ghi t R0 đ n R7, ta có 21 thanh ghi ch c năng

ệ ộ ừ ị ủ ế ầ ỉ ặ đ c bi t SFR chi m ph n trên c a Ram n i t ầ ư ế đ a ch 80H đ n FFH. C n l u

ả ấ ả ỉ ừ ị ề ế ượ ị ý là không ph i t t c 128 đ a ch t 80H đ n FFH đ u đ c đ nh nghĩa mà

ỉ ượ ị ỉ ị ch có 21 đ a ch đ c đ nh nghĩa.

d. Các thanh ghi đ c bi

ặ ệ t

ứ ặ ệ ế ầ 8051 có 21 thanh ghi ch c năng đ c bi ủ t SFR chi m ph n trên c a

ộ ừ ị ầ ư ả ấ ả ế ỉ ị Ram n i t đ a ch 80H đ n FFH. C n l u ý là không ph i t t c 128 đ a ch ỉ

nghĩa mà ch có 21 đ a ch đ

ừ ế ề ượ ỉ ượ ị ỉ t 80H đ n FFH đ u đ ị c đ nh ị c đ nh

ả ặ ệ ớ ữ ệ các thanh ghi đ c bi ế t trong vùng nh d li u 80H đ n nghĩa. Hình 2.6 mô t

ị ủ FFH và giá tr c a chúng sau khi Reset.

ặ ệ t Hình 2.6: Các thanh ghi đ c bi

Thanh ghi chính:

ủ ể ề Thanh ghi tính toán chính c a vi đi u khi n 8051 ACC (Accumulator).

ặ ệ ủ ể ự ủ Là thanh ghi đ c bi ệ t c a 8051 dùng đ th c hi n các phép toán c a CPU,

ườ th ệ ng kí hi u là A.

Thanh ghi ph :ụ

ụ ủ ề ể Thanh ghi tính toán ph c a vi đi u khi n 8051 là B. Thanh ghi B đ aở ị

ỉ ượ ứ ớ ch F0H đ c dùng chung v i thanh ch a A trong các phép toán nhân, chia.

17

ệ ứ ế ứ ấ ố L nh MUL AB nhân 2 s 8 bit không d u ch a trong A và B và ch a k t qu ả

ứ ặ ấ ấ ấ 16 bit vào c p thanh ghi B, A (thanh ch a A c t byte th p và thanh ghi B c t

byte cao).

ệ ở ươ ố ấ ứ L nh chia DIV AB chia A b i B, th ng s c t trong thanh ch a A và

ư ố ấ ượ ử d s c t trong thanh ghi B. Thanh ghi B còn đ ư ộ c x lý nh m t thanh ghi

ượ ị ỉ ủ ỉ ừ ị ị nháp. Các bit đ c đ nh đ a ch c a thanh ghi B có đ a ch t ế F0H đ n F7H.

ạ ươ Thanh ghi tr ng thái ch ng trình (PSW):

ươ ị ạ Thanh ghi tr ng thái ch ỉ ng trình PSW (đ a ch : D0H) là thanh ghi mô

ả ộ ạ ươ ủ ệ ố t toàn b tr ng thái ch ạ ộ ng trình đang ho t đ ng c a h th ng. B ngả 2.2 và

7

6

4

3

5

2

1

0

CY

AC

RS1

RS0

F0

0V

P

ả ả ẽ s mô t thanh ghi này. B ng 2.3

Bit

Mô t

bitả

ả ạ ươ Thanh ghi tr ng thái ch ng trình PSW B ng 2.2:

ị

ỉ

Ký Hi uệ

Đ a Ch

CY

D7H

PSW.7

C nhờ ế ượ ớ (Carry Flag): đ c Set n u có Bit ộ ớ ừ ặ nh t Bit 7 trong phép c ng ho c có Bit ừ ượ m n cho Bit 7 trong phép tr .

AY

D6H

PSW.6

ượ

ớ ừ

c Set trong phép c ng Bit 3 sang Bit 4 ho c k t ấ

ộ ặ ế ả

ằ

ờ ớ ụ: đ C nh ph ế n u có Bit nh t ả qu trong 4 Bit th p n m trong kho ng 0AH>0FH.

FO

D5H

PSW.5

ườ ử ụ

i s d ng.

C Oờ : dành cho ng

RS1

D4H

PSW.4

ọ

(Bit 1)

Ch n dãy thanh ghi

ọ

RS0

D3H

(Bit 0)

PSW.3

ỉ ỉ ỉ ỉ

Ch n dãy thanh ghi ị 00=Bank 0: Đ a ch 00H>07H ị 01=Bank 1: Đ a ch 08H>0FH ị 10=Bank 2: Đ a ch 10H>17H ị 11=Bank 3: Đ a ch 18H>1FH

0V

D2H

PSW.2

ờ

ượ

(Overflow Flag): đ ế ấ

ặ

c Set khi phép C tràn ả toán có d u có k t qu > +127 ho c < 128.

D1H

PSW.1

ư

Ch a dùng

P

D0H

PSW.0

ượ

C ki m tra ch n l ầ ứ ằ

ặ ẵ ẻ: đ ờ ể c Set ho c Clear ể ỳ ệ ở ỗ b i ph n c ng sau m i 1 chu k l nh, đ ặ ố ẻ ố ẵ ỉ Bit 1 ch ra r ng có 1 s ch n ho c s l trong thanh ch a.ứ

ả ế Chi ti t các bit trong thanh ghi PSW B ng 2.3:

ế Thanh ghi ngăn x p (Stack Pointer):

ỏ ở ị Con tr stack SP (stack pointer) là 1 thanh ghi 8 bit ỉ đ a ch 81H. SP

ứ ị ệ ở ỉ ủ ệ ỉ ủ ữ ệ ch a đ a ch c a d li u hi n đang ế đ nh c a stack. Các l nh liên quan đ n

ấ ữ ệ ữ ệ ệ ệ ấ ồ ỏ satck bao g m l nh c t d li u vào stack và l nh l y d li u ra kh i stack.

ệ ấ ướ ệ ấ ữ ệ ữ ệ Vi c c t vào stack làm tăng SP tr c khi ghi d li u và vi c l y d li u ra

ẽ ả ủ ỏ ượ ữ kh i stack s gi m SP. Vùng stack c a 8051 đ c gi trong RAM n i ộ và

ượ ớ ạ ấ ượ ế ỉ ể ở ị ỉ đ c gi ị i h n đ n các đ a ch truy xu t đ ế ị c b i ki u đ nh đ a ch gián ti p.

ữ ệ ừ ệ ấ ẽ ấ ữ ệ Các l nh PUSH và POP s c t d li u vào stack và l y d li u t stack, các

ọ ươ ệ ở ề ệ l nh g i ch ng trình con (ACALL, LCALL) và l nh tr v (RET, RETI)

ủ ụ ấ ồ ộ ươ cũng c t và ph c h i n i dung c a b ộ đ mế ch ng trình PC (Program

counter)

ỏ ữ ệ Con tr d li u DPTR:

ỏ ữ ệ ượ ấ ộ ể Con tr d li u DPTR (data pointer) đ c dùng đ truy xu t b nh ớ

ươ ớ ữ ệ ặ ộ ộ ch ng trình ngoài ho c b nh d li u ngoài. DPTR là m t thanh ghi 16 bit

ấ ị ỉ có đ a ch là 82H (DPL, byte th p) và 83H (DPH, byte cao).

ổ Thanh ghi các c ng P0P3:

ủ ấ ậ ạ ị ỉ Các port xu t/nh p c a 8051 bao g m ồ Port 0 t i đ a ch 80H, Port 1

19

ạ ị ỉ ạ ị ỉ ạ ị ấ ả ỉ t i đ a ch 90H, Port 2 t i đ a ch A0H và Port 3 t i đ a ch B0H. T t c các

ề ượ ỉ ừ ấ ả ằ ị ị port đ u đ ế c đ nh đ a ch t ng bit nh m cung c p các kh năng giao ti p

m nh.ạ

ố ế ộ ệ ề Thanh ghi b đ m truy n thông n i ti p (Serial Data Buffer):

B đ m truy n thông đ

ộ ệ ề ượ ộ ệ ộ ệ ề c chia thành hai b đ m, b đ m truy n d ữ

ữ ệ ữ ệ ộ ệ ệ ậ ượ ể li u và b đ m nh n d li u. Khi d li u đ c chuy n vào thanh ghi SBUF,

ữ ệ ẽ ượ ữ ệ ộ ệ ẽ ượ ư ể ề d li u s đ c chuy n vào b đ m truy n d li u và s đ c l u gi ữ ở đó

ố ế ữ ệ ế ề ế ề cho đ n khi quá trình truy n d li u qua truy n thông n i ti p k t thúc. Khi

ữ ệ ừ ự ệ ể ệ th c hi n vi c chuy n d li u t SBUF ra ngoài, d li u s đ ữ ệ ẽ ượ ấ ừ ộ c l y t b

ậ ữ ệ ủ ố ế ề ệ đ m nh n d li u c a truy n thông n i ti p.

ờ ộ ế ủ ộ ị Thanh ghi c a b đ nh th i/b đ m:

ộ ế ể ị ờ ị ả 8051 có 2 b đ m/đ nh th i (counter/timer) 16 bit đ đ nh các kho ng

ặ ặ ờ ể ế th i gian ho c đ đ m các s ki n. ự ệ Các c p thanh ghi (TH0, TL0) và (TH1,

ộ ế ủ ờ ộ ị ờ ị ỉ TL1) là các thanh ghi c a b đ m th i gian. B đ nh th i 0 có đ a ch 8AH

ộ ị ấ ờ ị ỉ (TL0, byte th p) và 8CH (TH0, byte cao). B đ nh th i 1 có đ a ch 8BH (TL1,

ấ byte th p) và 8DH (TH1, byte cao).

ủ ộ ị ạ ộ ờ ượ ế ậ ế ộ ị ở Ho t đ ng c a b đ nh th i đ c thi t l p b i thanh ghi ch đ đ nh

ờ ở ị ỉ ỉ ượ ị th i TMOD (Timer Mode Register) đ a ch 88H. Ch có TCON đ ị c đ nh đ a

ỉ ừ ch t ng bit.

ề ể Các thanh ghi đi u khi n:

ể ặ ệ ư ề Các thanh ghi đi u khi n đ c bi t nh IP, IE, TMOD, TCON, SCON và

ủ ệ ố ể ề ậ ạ ắ PCON là các thanh ghi đi u khi n và ghi nh n tr ng thái c a h th ng ng t,

bộ

ố ế ề ờ ị ế ủ ế đ m/đ nh th i, truy n thông n i ti p. Chi ti t c a các thanh ghi này s đ ẽ ượ c

ả mô t sau.

e. Các b đ nh th i c a 8051

ờ ủ ộ ị

ộ ị ờ ở ầ 8051 có hai b đ nh th i là ph n này chúng ta Timer 0 và Timer 1,

ủ ề ậ bàn v các thanh ghi c a chúng và sau đó trình bày cách l p trình chúng nh ư

ộ ễ ờ ể ạ ế th nào đ t o ra các đ tr th i gian.

ộ ị ả ề ộ C hai b đ nh th i cượ ờ Timer 0 và Timer 1 đ u có đ dài 16 bit đ

ư ậ ẽ truy c p nh hai thanh ghi tách bi t ệ byte th pấ và byte cao. Chúng ta s bàn

ề ừ riêng v t ng thanh ghi.

ủ ộ Các thanh ghi c a b Timer 0

ượ ư ậ ấ c truy c p nh byte th p và byte cao: Thanh ghi 16 bit c a bủ ộ Timer 0 đ

ấ ượ ọ Thanh ghi byte th p đ c g i là TL0 (Timer0 Low byte).

ượ ọ Thanh ghi byte cao đ c g i là TH0 (Timer0 High byte).

ể ượ ặ ượ ọ Các thanh ghi này có th đ ậ c truy c p, ho c đ ư ọ c đ c nh m i thanh ghi

ư ạ ẳ khác ch ng h n nh A, B, R0, R1, R2 v.v...

ủ ộ Các thanh ghi c a b Timer 1

ố ờ Gi ng nh ộ ị ư timer 0, b đ nh th i gian Timer 1 cũng dài 16 bit và thanh

ượ ủ ghi 16 bit c a nó cũng đ c chia ra thành hai byte là TL1 và TH1. Các thanh

ượ ủ ộ ư ậ ọ ố ở ghi này đ c truy c p và đ c gi ng nh các thanh ghi c a b Timer 0 trên.

Thanh ghi TMOD

ả ề ộ ộ ị C hai b đ nh th i ượ c ờ Timer 0 và Timer 1 đ u dùng chung m t thanh ghi đ

ể ế ậ ế ộ ộ ị ủ ệ g i làọ t l p các TMOD: đ thi ch đ làm vi c khác nhau c a b đ nh

th iờ .

Thanh ghi TMOD là thanh ghi 8 bit g mồ có:

21

ể ế ậ 4 bit th p đ thi ấ t l p cho b ộ Timer 0.

ể ế ậ 4 bit cao đ thi t l p cho Timer 1.

Trong đó:

ấ ủ ể ế ậ ờ 2 bit th p c a chúng dùng đ thi ế ộ ủ ộ ị t l p ch đ c a b đ nh th i.

ị 2 bit cao dùng đ xác đ nh phép toán. ể

2. Vi đi u khi n 8052

ể ề

ủ ọ ể ề ộ B vi đi u khi n 8052 là thành viên khác c a h 8051, 8052 có t ấ ả t c

ủ ẩ ặ các đ c tính chu n c a 8051 ngoài ra nó có thêm 128 byte RAM và m t b ộ ộ

ờ ữ ộ ị ờ ị đ nh th i n a. Hay nói cách khác là 8052 có 256 byte RAM và 3 b đ nh th i,

ư nó cũng có 8K byte ROM trên chíp thay vì 4K byte nh 8051.

ặ

Đ c tính

8051

8052

8031

ROM trên chip

RAM

ộ ị

ờ B đ nh th i

4K byte 128 byte 2 32 1 6

8K byte 256 byte 3 32 1 8

0K 128 byte 2 32 1 6

Chân vào – ra

ố ế

ổ

C ng n i ti p

ồ ắ Ngu n c t

ả ặ ọ ủ . So sánh các đ c tính c a các thành viên h 8051. B ng 2.4

ả ậ ươ ng

Qua b ng trên ta th y thì 8051 là t p con c a 8052, nên m i ch ế ấ ạ ượ ủ ư ề ề c trên 8052 nh ng đi u ng t cho 8051 đ u ch y đ ọ ượ ạ c l i là không

trình vi đúng.

3. Vi đi u khi n 8031

ề ể

ủ ộ M t thành viên khác c a 8051 là chíp 8031. Chíp này không có ROM

ể ử ụ ả ổ trên chíp nên đ s d ng chíp này ta ph i b sung ROM ngoài cho nó, ROM

ứ ươ ẽ ạ ự ệ ớ ả ngoài ph i ch a ch ng trình mà 8031 s n p và th c hi n. So v i 8051 mà

ươ ượ ị ớ ạ ứ ở ch ng trình đ c ch a trong ROM trên chíp b gi i h n b i 4K byte, còn

ứ ƣơ ượ ắ ể ớ ế ROM ngoài ch a ch ng trình đ c g n vào 8031 thì có th l n đ n 64K

ư ậ ổ ỉ ạ ể ả ể ổ ổ byte. Khi b xung c ng, nh v y ch còn l i hai c ng đ thao tác. Đ gi i

ế ấ ể ổ ề ằ ổ ố quy t v n đ này ta có th b xung c ng vào ra cho 8031 b ng cách ph i

ớ ộ ẳ ạ ổ ớ ớ ghép 8031 v i b nh và c ng vào ra ch ng h n v i chíp 8255. Ngoài ra còn

ề ố ộ ủ ả ừ ấ có các phiên b n khác nhau v t c đ c a 8031 t ả các hãng s n xu t khác

nhau.

II.

Ọ Ể Ề H VI ĐI U KHI N PIC

PIC là vi tế t tắ c aủ “Programable Intelligent Computer”, có thể t mạ

d chị là “máy tính thông minh khả trình” do hãng Genenral Instrument đ tặ tên

cho vi đi uề khi nể đ uầ tiên c aủ h : ọ PIC1650 đ cượ thi tế kế để dùng làm các

ề thi tế bị ngo iạ vi cho vi đi uề khi nể CP1600. Vi đi u khi n ể này sau đó đ cượ

ề ể nghiên c uứ phát tri nể thêm và từ đó hình thành nên dòng vi đi u khi n PIC ngày

nay.

Hi nệ nay trên thị tr ngườ có r tấ nhi uề họ vi đi uề khi nể như 8051,

Motorola 68HC, AVR, ARM,... Ngoài họ 8051 đ cượ h ngướ d nẫ m tộ cách căn

b nả ở môi tr ngườ đ iạ h c,ọ b nả thân ng iườ vi tế đã ch nọ họ vi đi uề khi nể PIC

ứ để mở r ngộ v nố ki nế th cứ và phát tri nể các ng d ng ụ trên công cụ này vì các

23

nguyên nhân sau:

+ Họ vi đi uề khi nể này có thể tìm mua dễ dàng t iạ thị

tr ngườ Vi tệ Nam. Giá thành không quá đ tắ

ầ ủ ạ ộ ộ ậ ủ ề ể ộ + Có đ y đ các tính năng c a m t vi đi u khi n khi ho t đ ng đ c l p.

Là m tộ sự bổ sung r tấ t tố về ki nế th cứ cũng như về ngứ d ngụ cho họ vi

ể đi uề khi n mang tính truy nề th ng:ố họ vi đi uề khi nể 8051.

Số l ngượ ng iườ sử d ngụ họ vi đi uề khi nể PIC. Hi nệ nay t iạ Vi tệ Nam

cũng như trên thế gi i,ớ họ vi đi uề khi nể này đ cượ sử d ngụ khá r ngộ rãi. Đi uề này

t oạ nhi uề thu nậ l iợ trong quá trình tìm hi uể và phát tri nể các ngứ d ngụ nh :ư số

l ngượ tài li u,ệ số l ngượ các ngứ d ng ụ mở đã đ cượ phát tri nể thành công, dễ dàng

ặ trao đ i,ổ h cọ t p,ậ dễ dàng tìm đ cượ sự chỉ d nẫ khi g p khó khăn,…

ị Sự hỗ trợ c aủ nhà s nả xu tấ về trình biên d ch, các công cụ l pậ trình, n pạ

ch ngươ trình từ đ nơ gi nả đ nế ph cứ t p,…ạ

Các tính năng đa d ngạ c aủ vi đi uề khi nể PIC, và các tính năng này không

ng ngừ đ c ượ phát tri n.ể

ế 1. Ki n trúc PIC

C uấ trúc ph nầ c ngứ c aủ m tộ vi đi uề khi nể đ cượ thi tế kế theo hai d ngạ

ế ki nế trúc: ki nế trúc Von Neuman và ki n trúc Havard.

ế ế Hình 2.7: Ki n trúc Havard và ki n trúc VonNeuman

Tổ ch cứ ph nầ c ngứ c aủ PIC đ cượ thi tế kế theo ki nế trúc Havard. Đi mể

khác bi tệ gi aữ ki n ế trúc Havard và kiến trúc VonNeuman là c uấ trúc bộ nhớ dữ

li uệ và bộ nhớ ch ngươ trình.

Đ iố v iớ ki nế trúc VonNeuman, bộ nhớ dữ li uệ và bộ nhớ ch ngươ trình

n mằ chung trong m t ộ bộ nh ,ớ do đó ta có thể tổ ch c,ứ cân đ iố m tộ cách linh ho tạ

bộ nhớ ch ngươ trình và bộ nhớ d li u. ữ ệ Tuy nhiên đi uề này chỉ có ý nghĩa khi t cố

độ xử lí c aủ CPU ph iả r tấ cao, vì v iớ c uấ trúc đó, trong cùng m tộ th iờ đi mể CPU

chỉ có thể t ngươ tác v iớ bộ nhớ dữ li uệ ho cặ bộ nh ch ớ ươ trình. Như v yậ có ng

thể nói ki nế trúc VonNeuman không thích h pợ v iớ c uấ trúc c a ủ m tộ vi đi uề

khi n.ể

Đ iố v iớ ki nế trúc Havard, bộ nhớ dữ li uệ và bộ nhớ ch ngươ trình tách ra

ớ thành hai bộ nh riêng bi t.ệ Do đó trong cùng m tộ th iờ đi mể CPU có thể t ngươ

tác v iớ cả hai bộ nh ,ớ như v y ậ t cố độ xử lí c aủ vi đi uề khi nể đ cượ c iả thi nệ

đáng k .ể

M tộ đi mể c nầ chú ý n aữ là t pậ l nhệ trong ki nế trúc Havard có thể đ cượ

t iố uư tùy theo yêu c uầ ki nế trúc c aủ vi đi uề khi nể mà không phụ thu cộ vào c uấ

trúc dữ li u.ệ Ví d ,ụ đ iố v iớ vi đi uề khi nể dòng 16F, độ dài l nhệ luôn là 14 bit

ừ (trong khi dữ li uệ đ cượ tổ ch cứ thành t ng byte), còn đ iố v iớ ki nế trúc Von

ệ Neuman, độ dài l nhệ luôn là b iộ số c aủ 1 byte (do dữ li u đ ượ tổ ch cứ thành c

t ngừ byte).

ự ọ ề ể Các dòng PIC và cách l a ch n vi đi u khi n PIC

PIC có bộ nhớ flash

25

Các kí hi uệ c aủ vi đi uề khi nể PIC: PIC12xxxx: độ dài l nhệ 12 bit PIC16xxxx: độ dài l nhệ 14 bit PIC18xxxx: độ dài l nhệ 16 bit C: PIC có bộ nhớ EPROM (chỉ có 16C84 là EEPROM) F: LF: PIC có bộ nhớ flash ho tạ đ ngộ ở đi nệ

ngươ tự như LF, đây là kí

ụ ở ố áp th p ấ LV: t hi uệ cũ Bên c nhạ đó m tộ số vi đi uệ khi nể có kí hi uệ xxFxxx là EEPROM, n uế có cu i là flash (ví d PIC16F877 là EEPROM, còn PIC16F877A là

thêm chữ A flash).

ộ ề ể ớ

tệ Nam phổ bi nế nh tấ là các họ vi điều khiển PIC do hãng Microchip

Ngoài ra còn có thêm m t dòng vi đi u khi n PIC m i là dsPIC. ở Vi s nả xu t.ấ ọ ự ộ ợ ể ề Cách l a ch n m t vi đi u khi n PIC phù h p:

Tr cướ h tế c nầ chú ý đ nế số chân c aủ vi đi uề khi nể c nầ thi tế cho ngứ d ng.ụ

Có nhi u ề vi đi uề khi nể PIC v iớ số l ngượ chân khác nhau, th mậ chí có vi đi uề

khi nể chỉ có 8 chân, ngoài ra còn có các vi đi uề khi nể 28, 40, 44, … chân.

C nầ ch nọ vi đi uề khi nể PIC có bộ nhớ flash để có thể n pạ xóa

ch ngươ trình đ c ượ nhi u l n ề ầ h n.ơ

Ti pế theo c nầ chú ý đ nế các kh iố ch cứ năng đ cượ tích h pợ s nẵ trong vi

ể đi uề khi n, các chu nẩ giao ti pế bên trong.

ớ ươ ế ầ ộ ể Sau cùng c n chú ý đ n b nh ch ề ng trình mà vi đi u khi n cho phép.

Ngoài ra m iọ thông tin về cách l aự ch nọ vi đi uề khi nể PIC có thể đ cượ

tìm th yấ trong cuốn sách “Select PIC guide” do nhà s nả xu tấ Microchip cung

c p.ấ

2. Ngôn ng l p trình cho PIC

ữ ậ

Ngôn ngữ l pậ trình cho PIC r tấ đa d ng.ạ Ngôn ngữ l pậ trình c pấ th pấ có

MPLAB (đ cượ cung c pấ mi nễ phí b iở nhà s nả xu tấ Microchip), các ngôn ngữ

l pậ trình c pấ cao h nơ bao g mồ C, Basic, Pascal, … Ngoài ra còn có m tộ số ngôn

ngữ l pậ trình đ cượ phát tri nể dành riêng cho PIC như PICBasic, MikroBasic,…

ề ể 3. Vi đi u khi n PIC16F877A

a. Hình d ng và b trí chân c a Pic16F877A

ủ ố ạ

b. Đ c tính n i b t c a b x lý.

ổ ậ ủ ộ ử ặ

ệ ử ụ ợ

ườ ử ụ ả i s d ng có th l p trình v i các câu l nh đ n gi n

ơ ạ ừ ộ ố ệ ệ ệ ẽ

ệ S d ng công ngh tích h p cao RICSC CPU ể ậ ệ ớ Ng ự T t c các câu l nh th c hi n trong 1 chu kì ngo i tr m t s l nh r nhánh th c hi n trong 2 chu kì.

ấ ả ự ố ộ ạ ộ

ồ ự ệ

ng trình Flash 8Kx14 Words

ồ T c đ ho t đ ng là : Xung đ ng h vào la DC20MHz ệ Chu kì l nh th c hi n trong 200ns ớ ươ ớ ớ ộ ộ ộ B nh ch B nh Ram 368x8 bytes B nh EFPROM 256x8 bytes.

27

ơ ồ ố c. S đ kh i

d. T ch c b nh

ổ ứ ộ ớ

ộ ớ ươ B nh ch ng trình:

ớ ủ ươ B nh ch

ề

ừ

ộ ng trình c a vi ể PIC16F877A là bộ nhớ đi u khi n ngượ b ộ nhớ 8K word flash, dung l cượ phân (1 word = 14 bit) và đ ế ề page0 đ n thành nhi u trang (t ngươ page 3) . Như v yậ bộ nhớ ch cượ có kh ả năng ch aứ đ trình 8*1024 = 8192 l nhệ (vì m tộ l nhệ sau khi mã hóa sẽ có dung l ngượ 1 word (14 bit).

cượ đ aị chỉ c aủ ngươ trình, bộ ngượ ngươ trình có dung l

Để mã hóa đ 8K word bộ nhớ ch đ mế ch 13 bit (PC<12:0>).

Khi vi đi uề khi nể đ

ị

cượ reset, bộ đ m ế ch ngươ trình sẽ chỉ đ nế đ aị chỉ 0000h (Reset vector). Khi có ng tắ x yả ra, bộ đ mế ỉ ỉ ế ẽ ngươ trình s ch đ n đ a ch ch 0004h (Interrupt vector). Bộ nhớ ch ngươ trình không

bao g m ồ bộ nhớ stack và không đ cượ

đ aị chỉ hóa b i ở bộ đ mế ch ngươ trình.

ộ ớ B nh stack s đ ẽ ượ ề ậ ụ ể c đ c p c th

ầ trong ph n sau.

ộ ớ ữ ệ B nh d li u:

ủ ệ ộ ớ ượ B nh ớ d ữ li u c a PIC là b ộ nh EEPROM đ ề c chia ra làm nhi u

ố ớ bank. Đ i v i PIC16F877A bộ nhớ dữ li uệ đ cượ chia ra làm 4 bank. M iỗ

bank có dung l ngượ 128 byte, bao g mồ các thanh ghi có ch cứ năng đ cặ bi tệ

SFG (Special Function Register) n mằ ở các vùng đ aị chỉ th pấ và các thanh ghi

29

m cụ đích chung GPR (General Purpose Register) n mằ ở vùng đ aị chỉ còn l iạ

trong bank. Các thanh ghi SFR th ngườ xuyên đ cượ sử d ngụ (ví dụ như thanh

ghi STATUS) sẽ đ cượ đ tặ ở t tấ cà các bank c aủ bộ nhớ dữ li uệ giúp thu nậ ti nệ

trong quá trình truy xu tấ và làm gi mả b tớ l nhệ c aủ ch ngươ trình. Sơ đồ cụ

ệ thể c aủ bộ nhớ dữ li u PIC16F877A nh ư sau:

31

ớ ữ ệ ơ ồ ộ Hình 2.8 S đ b nh d li u PIC16F877A

Ổ Ậ Ấ CÁC C NG XU T NH P C A Ủ PIC16F877A:

C ngổ xu tấ nh pậ (I/O port) chính là ph ngươ ti nệ mà vi đi uề khi nể dùng

để t ngươ tác v iớ thế gi iớ bên ngoài. Sự t ngươ tác này r tấ đa d ngạ và thông qua

quá trình t ngươ tác đó, ch cứ năng c aủ vi đi uề khi nể đ cượ thể hi nệ m tộ cách rõ

ràng.

M tộ c ngổ xu tấ nh pậ c aủ vi đi uề khi nể bao g mồ nhi uề chân (I/O pin), tùy

theo cách b tríố và ch cứ năng c aủ vi đi uề khi nể mà số l ngượ c ngổ xu tấ nh pậ và

số l ngượ chân trong m i c ng ỗ ổ có thể khác nhau. Bên c nhạ đó, do vi đi uề khi nể

ặ đ cượ tích h pợ s nẵ bên trong các đ c tính giao ti pế ngo iạ vi nên bên c nhạ ch cứ

ườ năng là c ngổ xu tấ nh pậ thông th ng, m tộ số chân xu tấ nh pậ còn có thêm các

ch cứ năng khác để thể hi nệ sự tác đ ngộ c aủ các đ cặ tính ngo iạ vi nêu trên đ iố v iớ

thế gi iớ bên ngoài. Ch cứ năng c aủ t ngừ chân xu tấ nh pậ trong m iỗ c ngổ hoàn toàn

có thể đ cượ xác l pậ và đi uề khi nể đ cượ thông qua các thanh ghi SFR liên quan

ấ đ nế chân xu t nh p ậ đó.

Vi đi uề khi nể PIC16F877A có 5 c ngổ xuất nh p,ậ bao g mồ PORTA,

PORTB, PORTC, PORTD và PORTE. C uấ trúc và ch cứ năng c aủ t ngừ c ngổ xu tấ

nh pậ sẽ đ cượ đề c pậ cụ th ể trong ph nầ sau.

Ọ Ể Ề III. H VI ĐI U KHI N AVR

ộ ọ ể ề ả ấ AVR là m t h vi đi u khi n do hãng Atmel s n xu t (Atmel cũng là

ể ạ ừ ề ể ấ ả ế nhà s n xu t dòng vi đi u khi n 89C51 mà có th b n đã t ng nghe đ n).

ớ ấ ệ ể ề ả ậ ơ AVR là chip vi đi u khi n 8 bits v i c u trúc t p l nh đ n gi n hóa

ể ấ ộ ể ệ RISC(Reduced Instruction Set Computer), m t ki u c u trúc đang th hi n

ư ộ ử ế u th trong các b x lí.

ơ ượ ề ế S l

c v ki n trúc VĐK ơ ấ ề ổ ớ ị 1. AVR n đ nh h n r t nhi u so v i dòng VĐK 8051

ớ ủ ọ Tính năng m i c a h AVR :

ế ệ ồ ộ Giao di n SPI đ ng b , giao ti p I2C, USART.

ế ạ ọ AVR do hãng Atmel ch t o ra, là h VĐK 8bit theo công ngh m i ệ ớ

ữ ạ ấ ượ ợ ớ v i nh ng tính năng r t m nh đ c tích h p trong trong chip.

ượ c.

ổ

ẵ

ạ

ộ ộ ị ộ ớ ậ ố i vào ra l p trình đ Các l ộ ế ợ Tích h p b bi n đ i ADC 10bit. Có s n các kênh băm xung PWM. ấ B Timer/Counter 8bit và 16bit r t m nh. ờ B đ nh th i Watchdog. B nh EEPROM.

ụ

ộ ố M t s chip AVR thông d ng: AT90S1200 AT90S2313 AT90C8534 ATtyni10, ATtyni11, ATtyni12 ATtyni15 ATtyni22 ATmega8/8515/8535 ATmega16 ATmega161 ATmega32 ATmega323 ATmega64/128/…

ộ ớ ấ 2. C u trúc b nh

ư ọ ứ ể ề ấ Cũng nh m i vi đi u khi n khác AVR có c u trúc Harvard t c là có

33

ườ ớ ươ ộ ớ ữ ệ ớ ộ b nh và đ ng bus riêng cho b nh ch ộ ng trình và b nh d li u.

ớ ủ ộ ớ ươ ấ ồ ộ Ta th y không gian b nh c a b nh ch ng trình g m 4Kx8 và có

ỉ ừ ị đ a ch t 0000H t ớ i FFFH.

ớ ữ ệ ầ ồ ộ ộ ộ ớ ớ B nh d li u g m hai ph n: b nh RAM và b nh EEPROM trong đó

ớ ạ ứ ầ ộ không gian b nh RAM l i chia làm 3 ph n: Các thanh ghi ch c năng

ớ ộ ố ộ chung, các thanh ghi vào ra và cu i cùng là 512 byte b nh SRAM. B nh ớ

ầ ủ ộ ớ ữ ệ ư ặ ộ ạ EEPROM m c dù cùng là m t ph n c a b nh d li u nh ng l i hoàn toàn

ư ộ ộ ớ ộ ậ ộ ậ ứ ượ ị ỉ đ ng đ c l p nh m t b nh đ c l p và cũng đ c đánh đ a ch riêng.

a. B nh d li u

ộ ớ ữ ệ

ượ ế ự ế c liên k t tr c ti p ứ AVR có 32 thanh ghi ch c năng chung và chúng đ

ể ệ ủ ộ ố ộ ử ự ạ ớ v i ALU đây là đi m khác bi t c a AVR và t o cho nó m t t c đ x lý c c

ượ ặ ừ ớ ặ ệ ặ cao. Các thanh ghi đ c đ t tên t R0 t i R31. Và đ c bi t c p 6 thanh ghi

ố ừ ớ ử ụ ừ ộ cu i (t R6 t i R31) t ng đôi m t tao thành các thanh ghi 16 bit s d ng làm

ỏ ỏ ớ ộ ớ ươ ầ ượ con tr tr t i b nh ch ữ ệ ng trình và d li u. Chúng l n l t có tên là X, Y,

Z.

b. B nh ch

ộ ớ ươ ng trình

ậ ộ ớ ượ Là b nh Flash l p trình đ c, trong các chip AVR cũ (nh ư

ớ ộ ươ ầ AT90S1200 hay AT90S2313…) b nh ch ỉ ồ ng trình ch g m 1 ph n là

ư ớ Application Flash Section nh ng trong các chip AVR m i chúng ta có thêm

ẽ ượ ầ ầ ả ph n Boot Flash setion. Boot section s đ c kh o sát trong các ph n sau,

ề ộ ớ ươ ự ể trong bài này khi nói v b nh ch ng trình, chúng ta t hi u là Application

ứ ự ấ ầ ầ ồ section. Th c ch t, application section bao g m 2 ph n: ph n ch a các

ạ ộ ứ ệ ầ ắ ủ instruction (mã l nh cho ho t đ ng c a chip) và ph n ch a các vector ng t

ắ ằ ở ủ ầ ầ (interrupt vectors). Các vector ng t n m ph n đ u c a application section

ừ ị ế ầ ạ ộ ỉ (t ứ đ a ch 0x0000) và dài đ n bao nhiêu tùy thu c vào lo i chip. Ph n ch a

ề ằ ươ ế ả ượ instruction n m li n sau đó, ch ng trình vi t cho chip ph i đ c load vào

ầ ph n này

ủ ộ ớ ươ ứ ứ Vì ch c năng chính c a b nh ch ng trình là ch a instruction, chúng

35

ơ ộ ề ậ ộ ộ ớ ta không có nhi u c h i tác đ ng lên b nh này khi l p trình cho chip, vì

ườ ậ ộ ớ ọ ế ố ớ th đ i v i ng i l p trình AVR, b nh này “không quá quan tr ng”. T t c ấ ả

ớ ữ ệ ủ ầ ằ ả ọ ộ các thanh ghi quan tr ng c n kh o sát n m trong b nh d li u c a chip.

ắ 3. Ng t Ngoài

ắ Ng t trên AVR a.

ườ ẩ ấ ệ ắ ộ ọ Interrupts, th ng đ ở ế ượ g i là ng t, là m t tín hi u kh n c p g i đ n c

ạ ộ ộ ử ứ ạ ầ ắ ừ ộ ử b x lí, yêu c u b x lí t m ng ng t c kh c các ho t đ ng hi n t ệ ạ ể i đ

ụ ẩ ấ ộ ơ ự ệ ệ ế ả ệ ộ “nh y” đ n m t n i khác th c hi n m t nhi m v kh n c p nào đó, nhi m

ụ ụ ắ ọ ế ụ v này g i là trình ph c v ng t – isr (interrupt service routine ). Sau khi k t

ộ ế ụ ệ ươ ẽ ượ ả ề thúc nhi m v trong isr, b đ m ch ng trình s đ c tr v giá tr tr ị ướ c

ể ộ ử ề ự ụ ệ ệ ế ở ư ậ đó đ b x lí quay v th c hi n ti p các nhi m v còn dang d . Nh v y,

ứ ộ ư ử ắ ấ ắ ườ ượ ể ử ng t có m c đ u tiên x lí cao nh t, ng t th ng đ c dùng đ x lí các

ờ ư ệ ề ấ ẫ ờ ố ế ự ệ s ki n b t ng nh ng không t n quá nhi u th i gian. Các tín hi u d n đ n

ấ ắ ừ ế ị ắ ể ng t có th xu t phát t các thi ộ ế t b bên trong chip (ng t báo b đ m

ở ữ ệ ế ắ ằ timer/counter tràn, ng t báo quá trình g i d li u b ng RS232 k t thúc…)

ắ ượ ắ ấ hay do các tác nhân bên ngoài (ng t báo có 1 button đ c nh n, ng t báo có

ượ ữ ệ 1 gói d li u đã đ ậ c nh n…).

ự ệ ắ ậ ắ ộ ỏ ỹ Ng t là m t trong 2 k thu t “b t” s ki n c b n ơ ả là h i vòng

ắ ưở ượ ế ế ộ ề ạ (Polling) và ng t. Hãy t ng t ạ ầ ng b n c n thi ể t k m t m ch đi u khi n

ệ ấ ụ ự ệ ề ậ ồ ỉ ừ hoàn ch nh th c hi n r t nhi u nhi m v bao g m nh n thông tin t ng ườ i

ặ ậ dùng qua các button hay keypad (ho c keyboard), nh n tín hi u t ệ ừ ả c m

ử ể ệ ể ế ấ ạ ị ề bi n, x lí thông tin, xu t tín hi u đi u khi n, hi n th thông tin tr ng thái

ể ạ ượ ớ lên các LCD…(b n hoàn toàn có th làm đ c v i AVR), rõ ràng trong các

ụ ệ ệ ậ ườ nhi m v này vi c nh n thông tin ng i dùng (start, stop, setup, change,…)

ư ụ ệ ế ả ớ ạ ấ ấ r t hi m x y ra (so v i các nhi m v khác) nh ng l ấ ẩ i r t “kh n c p”,

ượ ư ế ầ ạ ầ ế đ c u tiên hàng đ u. N u dùng Polling nghĩa là b n c n vi ạ t 1 đo n

ươ ủ ạ ạ ch ng trình chuyên thăm dò tr ng thái c a các button (tôi t m g i ọ đo nạ

ươ ạ ả ươ ch ng trình ạ đó là Input()) và b n ph i chèn đo n ch ng trình Input() này

ề ấ ị ươ ể ườ ợ ỏ vào r t nhi u v trí trong ch ng trình chính đ tránh tr ng h p b sót

ừ ườ ự ề ậ ờ ả ệ l nh t ng i dùng, đi u này th t lãng phí th i gian th c thi. Gi i pháp cho

ế ố ử ụ ớ ườ ề ắ ằ ấ v n đ này là s d ng ng t, b ng cách k t n i các button v i đ ắ ng ng t

ử ụ ươ ụ ụ ủ c a chip và s d ng ch ng trình Input() làm trình ph c v ng t ắ isr c aủ

ự ạ ầ ả ắ ng t đó, b n không c n ph i chèn Input() trong lúc đang th c thi và vì th ế

ỉ ượ ố ờ ọ ườ ấ không t n th i gian cho nó, Input() ch đ c g i khi ng i dùng nh n các

button. Đó là ý t ngưở s d ng ử ụ ng t.ắ

ọ ổ ứ ườ ắ ch c ng t thông th ng trong các chip Hình 2.9 minh h a cách t

ố ượ ứ ắ ỗ ớ ỗ AVR. S l ng ng t trên m i dòng chip là khác nhau, ng v i m i ng t s ắ ẽ

ỉ ố ị ắ ắ ị ượ có vector ng t, vector ng t là các thanh ghi có đ a ch c đ nh đ ị c đ nh

ướ ủ ằ ầ ầ ộ ớ ươ ụ nghĩa tr c n m trong ph n đ u c a b nh ch ng trình. Ví d vector

ủ ắ ị ỉ ng t ngoài 0 (external interrupt 0) c a chip atmega8 có đ a ch là 0x001 (theo

ừ ươ ự ế datasheet t Atmel). Trong lúc ch ộ ng trình chính đang th c thi, n u có m t

ổ ẫ ắ ả ế ở ộ ế ự s thay đ i d n đ n ng t x y ra chân INT0 (chân 4), b đ m ch ươ ng

ế ả ị ỉ ả ử ạ ị trình (Program Counter) nh y đ n đ a ch 0x001, gi s ngay t i đ a ch ỉ

ụ ụ ệ ế ặ ắ ộ 0x001 chúng ta có đ t 1 l nh RJMP đ n m t trình ph c v ng t (IRS1

ữ ộ ế ộ ầ ạ ẳ ươ ể ự ế ả ch ng h n), m t l n n a b đ m ch ng trình nh y đ n IRS1 đ th c thi

ộ ế ụ ụ ắ ươ ạ ề ị ế trình ph c v ng t, k t thúc ISR1, b đ m ch ng trình l i quay v v trí

ướ ươ ắ ế tr c đó trong ch ng trình chính, quá trình ng t k t thúc. Không mang tính

ư ạ ộ ổ ươ ắ b t bu c nh ng tôi khuyên b n nên t ứ ch c ch ắ ng trình ng t theo cách

37

ữ ể ỗ ỉ ươ ị này đ tránh nh ng l ế i liên quan đ n đ a ch ch ng trình.

ồ

ắ Hình 2.9 Ng t.ắ ( Ngu n: hocavr.com) ắ t các vector ng t có trên chip atmega8 B ngả 2.5 Tóm t

ắ b. Ng t ngoài ắ ả ể ự ữ ệ ệ ế ấ Ng t ngoài là cách r t hi u qu đ th c hi n giao ti p gi a ng ườ i

ắ dùng và chip. Trên chip atmega8 có 2 ng t ngoài có tên là INT0 và INT1 t ươ ng

ứ ề ậ ư ố ố ệ ng 2 chân s 4 (PD2) và s 5 (PD3). Nh đã đ c p trong bài, khi làm vi c

ế ị ủ ạ ầ ỉ ớ v i các thi ư t b ngo i vi c a AVR, h u nh chúng ta ch thao tác trên các

ặ ệ ứ thanh ghi ch c năng đ c bi t SFR (Special Function Registers) trên vùng nh ớ

ế ị ộ ậ ể ề ạ ồ ợ ỗ IO, m i thi t b bao g m m t t p h p các thanh ghi đi u khi n, tr ng thái,

ớ ấ ả ề ắ ả ồ ng t…khác nhau, đi u này đ ng nghĩa chúng ta ph i nh t t c các thanh ghi

ụ ả ạ ủ c a AVR. Lúc này datasheet phát huy tác d ng, b n ph i nhanh chóng

ử ụ ủ ề ấ download file datasheet c a chip mình đang s d ng, có r t nhi u n i đ ơ ể

39

download nh t iư ạ www.atmel.comhay trên các trang web chuyên cung c p ICấ

ễ ề ớ ụ datasheet mi n phí ắ (www.alldatasheet.com là 1 ví d ). Quay v v i ng t

ế ắ ngoài, có 3 thanh ghi liên quan đ n ng t ngoài đó là MCUCR, GICR và GIFR.

ụ ể ượ ướ C th các thanh ghi đ c trình bày bên d i.

ề ể Thanh ghi đi u khi n MCU – MCUCR (MCU Control Register) là thanh

ế ộ ắ ậ ắ ướ ghi xác l p ch đ ng t cho ng t ngoài, quan sát ể c khi tìm hi u hình 2.10 tr

thanh ghi này.

ế ố ồ ắ Hình 2.10 K t n i ng t ngoài cho atmega8. ( Ngu n: hocavr.com)

ắ ề ể

ặ ạ ắ ạ ả

ủ

ượ ử ụ ư ể ề ỉ

ướ Thanh ghi đi u khi n ng t chung – GICR (General Interrupt Control ư Register) (chú ý trên các chip AVR cũ, nh các chip AT90Sxxxx, thanh ghi này ườ có tên là thanh ghi m t n ng t thông th ng GIMSK, b n tham kh o thêm ế ế ầ ử ụ datasheet c a các chip này n u c n s d ng đ n). GICR cũng là 1 thanh ghi 8 ắ bit nh ng ch có 2 bit cao (bit 6 và bit 7) là đ c s d ng cho đi u khi n ng t, ư ấ c u trúc thanh ghi nh bên d i (trích datasheet).

ọ

ắ ạ ộ ươ ự ắ Bit 7 – INT1 g i là bit cho phép ng t 1(Interrupt Enable), set bit này ề , bit INT0 đi u ng t

ể ạ ằ b ng 1 nghĩa b n cho phép ng t INT1 ho t đ ng, t ắ khi n ng t INT0.

ờ ắ

ờ ạ ủ ắ

ế ự ệ ả

ợ ủ ằ cho tr

ắ ự ươ ng t ậ ề ầ

ậ đ ng, vì v y thanh ghi này th

ng không đ ượ ấ

Thanh ghi c ng t chung – GIFR (General Interrupt Flag Register) có 2 bit INTF1 và INTF0 là các bit tr ng thái (hay bit c Flag) c a 2 ng t INT1 và ượ ợ INT0. N u có 1 s ki n ng t phù h p x y ra trên chân INT1, bit INTF1 đ c ể ử ườ ự ộ đ ng set b ng 1 (t t ng h p c a INTF0), chúng ta có th s ế ắ ể ụ t d ng các bit này đ nh n ra các ng t, tuy nhiên đi u này là không c n thi ượ ườ ắ ự ộ ế c n u chúng ta cho phép ng t t ắ ậ quan tâm khi l p trình ng t ngoài. C u trúc thanh ghi GIFR đ c trình bày trong hình ngay bên d i.ướ

ậ ệ ắ ẵ Sau khi đã xác l p các bit s n sàng cho các ng t ngoài

ầ

ủ ạ ộ i bài AVR2).

ắ ả

, vi c sau cùng ụ , trong thanh ghi ắ ứ chúng ta c n làm là set bit I, t c bit cho phép ng t toàn c c ạ tr ng thái chung c a chip (thanh ghi SREG, xem l M t chú ý ạ khác là vì các chân PD2, PD3 là các chân ng t nên b n ph i set các chân này là Input (set thanh ghi DDRD).

ƯƠ Ế Ế Ề Ể CH NG 3 : THI T K MODUL ĐI U KHI N NHÀ THÔNG MINH

I.

1. Khái quát về Vi điều khiển ATMEGA 8

Cơ sở lý thuyết

a. M t s đ c tính k thu t.

41

ộ ố ặ ậ ỹ

ề ể ộ ộ

(cid:0) ATMega8 là m t con Vi Đi u Khi n thu c dòng Mega AVR c a ủ ổ ộ ư hãng ATMEL. Dòng Vi Đi u Khi n này có tính năng n i tr nh :

ể ề

(cid:0) 32 thanh ghi đa d ngụ

(cid:0) ố ộ ố ế ạ ớ T c đ t i đa lên đ n 16MIPS v i th ch anh 16MHz

(cid:0) Có 8KB b nh Flash l p trình ISP ớ

o 512 byte EFPROM.

o 1k SRAM.

ậ ộ

o Chu k ghi/ xóa 10000 l n cho b nh flash ROM và 100000

ộ ớ ỳ

ớ ộ ầ ầ l n cho b nh EFPROM.

oC và 100 năm khi ở

o L u d li u t oC ệ ộ

ữ ệ ố ở ệ ộ i đa 20 năm nhi t đ 85

t đ 25 ư nhi

(cid:0) Tính năng ngo i viạ

o 2 b timer/counter 8 bít v i b đ m đi n t

ớ ộ ế ệ ử ằ ầ ố b ng t n s ,1 b ộ

ộ so sánh.

ộ ớ ộ ế ệ ử ằ b ng t n s , b ầ ố ộ

o 1 b timer/counter 16 bit v i b đ m đi n t so sánh và m t ch đ ch p đ i chi u.

ế ộ ụ ố ế ộ

o Bô đ m th i gian th c v i dao đ ng riêng.

o 3 kênh PWM.

ự ớ ế ờ ộ

o 6 kênh ADC 10 bits cho ki u v PDIP, 8 kênh ADC 10 bits cho

ể ỏ

ể ỏ ki u v TQFP và QFN/MLF.

ế ố ế o Giao ti p n i ti p TWI(I2C).

o 2 chân ng t ngoài INT0 và INT1 ng v i 2 chân PD2 và PD3.

ứ ắ ớ

o L p trình n i ti p USART.

ố ế ậ

o Giao ti p n i ti p SPI master/slave.

ố ế ế

o L p trình Watchdog Timer v i b onchip Oscillator

ớ ộ ậ

o B so sánh analog onchip.

ộ

(cid:0) M t vài tính năng đ c bi

ặ ộ ệ ủ t c a Atmega8A

o Reset b ng ngu n và có kh năng phát hi n l

ệ ằ ả ồ ỗ ậ i l p trình

Brownout

ằ ộ ộ ộ o Xung n i dùng b dao đ ng b ng RC

ừ

ạ

ả ắ ắ ạ o Có c ng t ngo i vi và ng t trong

ễ

ộ ), ADC Noise ệ

ế ộ ế

ệ

t ki m đi n)

,

ế ộ ỉ

ủ

ồ

.

Idle(Ng ng ho t đ ng , Powersave (Ch đ ti

o Có 5 ch đ ngh : Reduction(Nhi u ADC) Powerdown (Ch đ ngu n th p), ế ộ

ấ Standby (Ng đông)

(cid:0) I/O

o 23 ngõ vào/ra kh trình.

ả

ể ỏ ể o Được đóng gói trong 28 chân ki u v PDIP, và 32 chân ki u

TQFP và QFN/MLF.

o Đi n áp ho t đ ng 2,7V5,5V(ATmega8A,Atmega8L)và 4,5

ệ

43

ạ ộ 5,4V(ATmega8).

ố ạ ộ ầ o T n s ho t đ ng 0 8MHz (ATmega8L) và 0

16MHz(ATmega8A) đ ng.ộ

(cid:0) M c tiêu th đi n áp khi

oC

ụ ệ ứ ở 4MHz,3V,25

o Ho t đ ng: 3.6mA

ạ ộ

o Ch đ Idle : 1.0mA

ế ộ

2. Giao thức 1-Wire

a. Tổng quan về 1-Wire

ế ộ ấ ồ o Ch đ ngu n th p : 0,5µA

ứ ượ Giao th c 1Wire đ c phát phát tri n b i

ườ ế ồ ở Dallas Semiconductor (Công ề ng truy n

ữ ệ ệ ủ ty con c a Maxim) ở d li u, 1 đi n tr pullup g n ủ ắ ở phía thi ể ứ ỉ . Ki n trúc c a giao th c này ch bao g m 1 đ ế ị ủ hình 2.1). t b ch (

Hình 3.1 Truyền thông giữa các vi mạch bằng giao thức 1-Wire

ề ẩ

ả ố ượ ấ ng thi

ể ạ ớ ỏ ơ ố ữ ộ T c đ truy n nh n tiêu chu n c a 1wire là 15,4kbps, kho ng cách gi a ế ị ớ ế ị ủ t b t t b ch và thi thi ế ố k t n i trên bus đ ậ ủ ế ị ớ xa nh t có th đ t t t b t ế ượ c khuy n cáo nên nh h n 20 thi i 200m. S l ế ị t b .

ử ụ ệ

ứ ả ừ ể ế ậ ằ ứ ạ ộ Giao th c 1Wire s d ng m c logic CMOS/TTL. Đi n áp ho t đ ng n m ớ ề ủ ế ị có th truy n/nh n v i t b ch và thi trong d i t 2.8 đ n 6V. Thi ế ị ớ t b t

ể ờ ộ ượ i m t th i đi m ch có m t trong hai thao tác đ ự c th c thi.

ấ ượ ướ ạ nhau, tuy nhiên t ố ấ ọ Bit có tr ng s th p nh t (LSB) đ ộ ỉ ề c truy n đi tr c.

ủ ụ ữ ề ậ ế ị ủ ướ Th t c truy n/nh n gi a thi t b ch và thi ế ị ớ t b t ồ bao g m 3 b c:

ế ị ượ ố ộ ữ t b đ ồ c n i trên bus, đ ng b gi a thi ế ị ủ t b ch

ừ

ế ị ủ

ư ừ ứ

ề

t b ch , bus ph i đ

thi ờ

c đ t chi u ra và đ a t ẽ ượ

ừ

ề

480 đ n 640µs. Ti p theo bus s đ

ả ượ ặ ế ả

ế

ấ

ờ

ứ ả ể ọ m c th p trong kho ng th i gian t ẽ ế ị ớ . Xung này s xu t hi n trong kho ng th i gian 60 đ n 240µs. N u có thi t b t ẽ

ả

ầ

ộ

ể ự ệ ữ ứ ấ ủ ậ ế ố ế

ề ứ

ự

ể

ệ

Đ th c hi n thao tác này, t ế gi ệ xác nh n c a thi ượ ạ ẽ ạ ượ c l c k t n i, bus s có tr ng thái logic “0”, ng đ ướ ụ ồ ừ 45 đ n 180 µs đ “ph c h i” v m c logic “1” tr t

ấ ố m c cao xu ng m c th p, ặ c đ t chi u vào đ đ c xung ế ị ớ ế t b t ờ ố i s là “1”. Cu i cùng, bus c n m t kho ng th i gian c khi th c hi n các thao tác khác.

(1) Reset, xác nh n có thi t b t và thi ậ ế ị ớ hình 3.2). (

ạ ế ị ủ ự ệ t b ch th c hi n reset Hình 3.2. D ng sóng khi thi

ế ả ệ ộ b. C m bi n nhi t đ DS18B20

ấ ở ộ ả ế c s n xu t b i Dalas Semiconductor t đ đ

ượ ủ ứ ợ ố DS18B20 là b c m bi n nhi đ ệ ộ ượ ả ộ ố c tích h p giao th c 1Wire. M t s thông s chính c a DS18B20:

ế ệ Đi n áp: 3.0V đ n 5.5V

ế ả ừ ế ộ 10°C đ n +85°C, đ chính xác là

ả D i đo:55°C đ n +125°C. Trong d i t ±0.5°C.

45

ỗ ị ị ố ớ ộ ế ổ ả M i giá tr nhi ệ ộ ượ t đ đ c bi n đ i sang gia tr s v i đ phân gi i 12bit.

ơ ồ ủ Hình 3.3. S đ chân c a DS18B20

Hình 3.4. Sơ đồ khối của DS18B20

Các thành phần chính trên DS18B20 bao gồm: - 64-bit lasered ROM, - Cảm biến nhiệt độ (temperature sensor) - Các thanh ghi cấu hình - Bộ cảnh báo quá nhiệt so với nhiệt độ đặt trước trong TH, TL. - Bộ phát mã vòng (CRC). - Bộ đệm, bộ biến đổi tương tự-số (SCRATCHPAD)

Khi hoạt động, DS18B20 sẽ tự động biến đổi nhiệt độ thu được từ cảm biến thành giá trị số, truyền về thiết bị chủ bằng giao thức 1-Wire. Bảng 3.1 mô tả quan hệ giữa nhiệt độ thực và giá trị số.

ả ị ố ươ ứ ượ ổ ươ ứ ế Giá tr s t ng ng đ c bi n đ i t ng ng nhi ệ ộ ự t đ th c B ng 3.1.

ổ ế ề ả 3. T ng quan v c m bi n quang

ậ ệ ệ ử ấ ặ ở ộ ạ Quang tr là m t lo i "v t li u" đi n t r t hay g p và đ ượ ử c s

ữ ế ả ể ể ộ ạ ụ d ng trong nh ng m ch c m bi n ánh sáng . Có th hi u m t cách d ễ

Ở Ệ ệ ằ ạ ở ộ ở dàng r ng, quang tr là m t lo i ĐI N TR có đi n tr ổ thay đ i theo

ườ ặ ở ế ộ ườ c ng đ ánh sáng. N u đ t môi tr ng có ít ánh sáng, có bóng râm

ặ ố ở ủ ở ẽ ặ ở ệ ế ắ ho c t i thì đi n tr c a quang tr s tăng cao còn n u đ t ngoài n ng,

ở ẽ ả ặ ơ ệ ho c n i có ánh sáng thì đi n tr s gi m.

ở ị ố ả ượ ế ạ ệ Là đi n tr có tr s càng gi m khi đ c chi u sáng càng m nh.

ở ố ệ ượ ế ở ố ườ Đi n tr t i (khi không đ c chi u sáng trong bóng t i) th ng trên

(cid:0) ị ố ể ướ ấ ả ỏ ượ , tr s này gi m r t nh có th d i 100 khi đ ế c chi u sáng 1M(cid:0)

47

m nhạ

ệ ủ ế ở ệ Nguyên lý làm vi c c a quang đi n tr là khi ánh sáng chi u vào

ể ẫ ấ ch t bán d n (có th là Cadmium sulfide – CdS, Cadmium selenide –

ệ ử ự ứ ự ẫ CdSe) làm phát sinh các đi n t t ệ do, t c s d n đi n tăng lên và làm

ạ ủ ở ủ ệ ệ ấ ả ẫ ặ ộ gi m đi n tr c a ch t bán d n. Các đ c tính đi n và đ nh y c a quang

ậ ệ ế ạ ệ ở ộ đi n tr dĩ nhiên tùy thu c vào v t li u dùng trong ch t o.

ề ươ ệ ượ ấ ộ V ph ng di n năng l ng, ta nói ánh sáng đã cung c p m t năng

ượ ệ ử ả ừ ệ ẫ ị l ể ng E=h.f đ các đi n t nh y t ư ậ dãi hóa tr lên dãi d n đi n. Nh v y

ượ ế ả ớ ơ ượ ̉ ấ ủ năng l ầ ng c n thi t h.f ph i l n h n năng l ng c a dai c m.

II.

ế ế Quy trình thi ộ t k và n i dung thi ế ế t k

́ ươ ́ ́ 1. H ng thiêt kê.

̀ ́ ̀ ́ ̃ ̀ ̀ ̃ ư ̉ ̉ ̉ ̣ Chung ta se dung vi điêu khiên AVR đê điêu khiên va lây d liêu nhi ệ t

́ ệ ộ ̉ ̣ ̉ ̀ ộ ư ̉ đ t cam biên nhi t đ DS18B20, cho hiên thi lên 2 led 7 thanh. Cho cam

́ ́ ̀ ́ ̀ ́ ̀ ́ ́ ́ ở ̣ ̉ ́ biên anh sang nhân biêt anh sang va điêu khiên bong đen tăt m

́ ̀ ́ư ́ 2. Thiêt kê phân c ng

́ ơ ̀ a. S đô nguyên ly

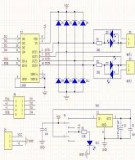

Hình 3.5. Sơ đồ nguyên lý

b. S đ mach in

49

ơ ồ ̣

ơ ồ ạ Hình 3.6. S đ m ch in

a.i. Viêt ch

́ ̀ ̀ ươ ̉ ̣ ng trinh điêu khiên cho mach

/*****************************************************

Project : Nghien Cuu Ly Thuyet Nha Thong Minh

Version : 1.0

Date : 26/02/2016

Author : NeVaDa

Company :

Comments:

Chip type : ATmega8

Program type : Application

AVR Core Clock frequency: 8,000000 MHz

Memory model : Small

External RAM size : 0

Data Stack size : 256

*****************************************************/

51

#include

#define ADC_VREF_TYPE 0x20

#include

#include <1wire.h>

#include

#define a PORTB.0

#define b PORTB.1

#define c PORTB.2

#define d PORTB.3

#define e PORTB.4

#define f PORTB.5

#define g PORTB.6

#define led1 PORTC.3

#define led2 PORTC.2

int t;

unsigned char *T=0;

int chuc,donvi;

interrupt [EXT_INT0] void ext_int0_isr(void)

{

}

interrupt [EXT_INT1] void ext_int1_isr(void)

{

}

unsigned char read_adc(unsigned char adc_input)

{

ADMUX=adc_input | (ADC_VREF_TYPE & 0xff);

delay_us(10);

ADCSRA|=0x40;

// Wait for the AD conversion to complete

while ((ADCSRA & 0x10)==0);

ADCSRA|=0x10;

return ADCH;

}

void ma7SEG(int so)

{

if(so==0){a=b=c=d=e=f=0; g=1;}

if(so==1){b=c=0; a=d=e=f=g=1;}

53

if(so==2){a=b=g=e=d=0; c=f=1;}

if(so==3){a=b=c=d=g=0; e=f=1;}

if(so==4){b=c=g=f=0; a=d=e=1;}

if(so==5){a=f=g=c=d=0; b=e=1;}

if(so==6){a=c=d=e=f=g=0;b=1; }

if(so==7){a=b=c=0;d=e=f=g=1; }

if(so==8){a=b=c=d=e=f=g=0; }

if(so==9){a=b=c=d=f=g=0; e=1;}

}

void hienthi(int k)

{

led1=1;

ma7SEG(k/10);delay_ms(10);

led1=0;PORTB=0XFF;

led2=1;

ma7SEG(k%10);delay_ms(10);

led2=0;PORTB=0XFF;

}

void nhietdo(void)

{

t=ds1820_temperature_10(T);

if(t>40){PORTC.4=1;}

else PORTC.4=0;

}

interrupt [TIM0_OVF] void timer0_ovf_isr(void)

{

TCNT0=50;

hienthi(t);

}

void anhsang(void)

{

if(read_adc(0)>=60){PORTC.5=0;}

else PORTC.5=1;

}

void setup(void)

{

PORTB=0x00;

DDRB=0xff;

55

PORTC=0x00;

DDRC=0xfe;

PORTD=0x00;

DDRD=0x00;

TCCR0=0x05;

TCNT0=0x00;

TCCR1A=0x00;

TCCR1B=0x00;

TCNT1H=0x00;

TCNT1L=0x00;

ICR1H=0x00;

ICR1L=0x00;

OCR1AH=0x00;

OCR1AL=0x00;

OCR1BH=0x00;

OCR1BL=0x00;

// Timer/Counter 2 initialization

// Clock source: System Clock

// Clock value: Timer2 Stopped

// Mode: Normal top=0xFF

// OC2 output: Disconnected

ASSR=0x00;

TCCR2=0x00;

TCNT2=0x00;

OCR2=0x00;

// External Interrupt(s) initialization

// INT0: On

// INT0 Mode: Low level

// INT1: On

// INT1 Mode: Low level

GICR|=0xC0;

MCUCR=0x00;

GIFR=0xC0;

// Timer(s)/Counter(s) Interrupt(s) initialization

TIMSK=0x01;

// USART initialization

57

// USART disabled

UCSRB=0x00;

// Analog Comparator initialization

// Analog Comparator: Off

// Analog Comparator Input Capture by Timer/Counter 1: Off

ACSR=0x80;

SFIOR=0x00;

// ADC initialization

// ADC Clock frequency: 1000,000 kHz

// ADC Voltage Reference: AREF pin

// Only the 8 most significant bits of

// the AD conversion result are used

ADMUX=ADC_VREF_TYPE & 0xff;

ADCSRA=0x83;

// SPI initialization

// SPI disabled

SPCR=0x00;

// TWI initialization

// TWI disabled

TWCR=0x00;

// 1 Wire Bus initialization

// 1 Wire Data port: PORTD

// 1 Wire Data bit: 0

// Note: 1 Wire port settings must be specified in the

w1_init();

ds1820_set_alarm(T,0,0);

#asm("sei")

}

void main(void)

{

unsigned char n=0;

setup();

while (1)

{

nhietdo();

anhsang();

59

}

}

ậ ế III. K t lu n

̉ ̀ư 1. Vê u điêm

́ ̀ ́ ̃ ư ̣ ệ ộ ̣ ̉ ̣ ̉ ̣ ́ Mach lây d liêu nhi ́ t đ va hiên thi ra rât chinh xac,ôn đinh

Ti lê sai sô nhó

̉ ̣ ̉

Đô chia nho (0.5 đô)

̣ ̉ ̣

Canh bao khi nhiêt đô qua cao

́ ́ ̉ ̣ ̣

Mach t

́ ự ̀ ơ ̣ ̣ ́ ̀ đông tăt đen khi tr i tôi

2. Vê nh

̀ ượ ̉ c điêm

Th i gian l y m u lâu

ẫ ấ ờ

́ ́ ̀ ̣ ̉ ̣ Mach điêu khiên it thiêt bi

Không ho t đ ng khi cúp đi n

ạ ộ ệ

3. H ng phát tri n

ướ ể

ệ ố ư ề ầ ợ ố Đ tài c n tích h p thêm các h th ng thông minh khác nh : ch ng

ở ử ự ộ ệ ố ớ ệ ố ế ợ ộ tr m, h th ng đóng m c a t ề đ ng… k t h p v i h th ng đi u

ể ằ khi n b ng modul sim, camera giám sát.

H th ng b o b o nhi

ệ ố ả ả ệ ộ ầ ớ ế ị ế ợ t đ c n k t h p v i các thi t b trong nhà

ỉ ệ ộ ư ợ ể ề đ đi u ch nh nhi t đ cho phù h p, cũng nh phòng cháy khi khong

ườ có ng i trong nhà.

M ch đi u khi n c n tích h p IC nh , ngu n tích tr khi nhà b cúp

ể ầ ữ ề ạ ớ ợ ồ ị

đi nệ

ữ ự ệ ề ỏ Trong quá trình th c hi n đ tài này không tránh kh i nh ng sai sót, em

ậ ượ ự ỉ ả ủ ẻ ạ ầ ấ r t mong nh n đ c s chia s , ch b o c a th y cô cùng b n bè. Em xin

ả ơ chân thành c m n.

Ả Ệ TÀI LI U THAM KH O:

ề ể https://vi.wikipedia.org/wiki/Vi_đi u_khi n

http://ketnoi.com/

………………..

61

http://www.hocavr.com/

![Giáo trình Xử lý sự cố Diesel tàu thủy (Nghề Khai thác máy tàu thủy, Trình độ Trung cấp) - Trường Cao đẳng Nông nghiệp Thanh Hóa [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260508/songngu_011/135x160/23801778744471.jpg)