Tuyển tập Hội nghị Khoa học thường niên năm 2015. ISBN : 978-604-82-1710-5

148

CẢI THIỆN CHẤT LƯỢNG BỘ ĐIỀU KHIỂN PI BẰNG

PHƯƠNG PHÁP TÁCH KÊNH CHO HỆ THỐNG MIMO

Phan Thanh Tùng

Đại học Thủy lợi, email: phanthanhtung86@gmail.com

1. GIỚI THIỆU CHUNG

Các mô hình toán học cho đối tượng công

nghiệp thông thường là hệ nhiều đầu vào

nhiều đầu ra MIMO. Các đầu vào và đầu ra

này có sự tương tác lẫn nhau và việc thiết kế

bộ điều khiển đáp ứng yêu cầu cho các hệ

thống này đòi hỏi nhu cầu cấp thiết. Có rất

nhiều bộ điều khiển hiện đại như bộ điều

khiển mờ, bộ điều khiển nơron… nhưng

thiết kế đơn giản mà tin cậy nhất là bộ điều

khiển PI.

Bộ điều khiển PI đã được phát triển và

ứng dụng rộng rãi trong công nghiệp, tuy

nhiên nó chỉ được thiết kế cho đối tượng một

vào một ra SISO. Nội dung của bài báo nhằm

sử dụng phương pháp tách kênh để biến một

hệ thống MIMO trở thành các hệ SISO riêng

rẽ và từ đó dễ dàng thiết kế được các bộ PI

cho từng phần.

2. PHƯƠNG PHÁP NGHIÊN CỨU

Qua nghiên cứu về tư tưởng thuật toán, tác

giả đề xuất phương pháp tách kênh để hỗ trợ

tính toán các bộ điều khiển PI nhằm cải thiện

chất lượng điều khiển: giảm thời gian xác lập

của hệ thống, và chống nhiễu tác động. Từ đó

chất lượng của hệ thống sử dụng phương

pháp tách kênh có chất lượng nâng cao so với

hệ thống cũ.

Mô hình trạng thái tuyến tính đối tượng

MIMO hai đầu vào, hai đầu ra:

dA B E

dt

xx u d

y = Cx

Trong đó:

10,334 4,050 0

A 9,834 5,332 3,050

0 1,282 3,550

,

1 0 0

C0 0 1

0,3737 0,4263

B 0,4263 0,3737

00

,

0,3737 0

E 0,0263 1

00

Với:

xT = [x1, x2, x3] là vector 3 biến trạng thái

uT = [u1, u2] là vector 2 đầu vào điều khiển

dT = [d1, d2] là vector 2 nhiễu loạn.

yT = [y1, y2] là vector 2 biến đầu ra.

Sử dụng phương pháp cặp đôi vào/ra dựa

trên RGA thì ta chọn cặp đôi u1-y2 và u2-y1. (1)

Hàm truyền cho mỗi cặp biến vào ra u1-y2;

u2-y1

2

21 1

Y ( s )

G ( s ) U ( s )

0,74223.(1 0,0527.s )

(1 0,06784.s ).(1 0,2345.s ).(1 4,5004.s )

1

12 2

Y ( s )

G ( s ) U ( s )

0,0737(1 0,207.s )(1 2,0008.s)

(1 0,0678.s ).(1 0,2347.s ).(1 4,5455.s )

Thiết kế bộ điều khiển phi tập trung PID

tức là ta chỉ thiết kế bộ điều khiển cho cặp

biến chính (u1-y2) còn ảnh hưởng của các

biến khác (từ u2 đến y2 coi là nhiễu).

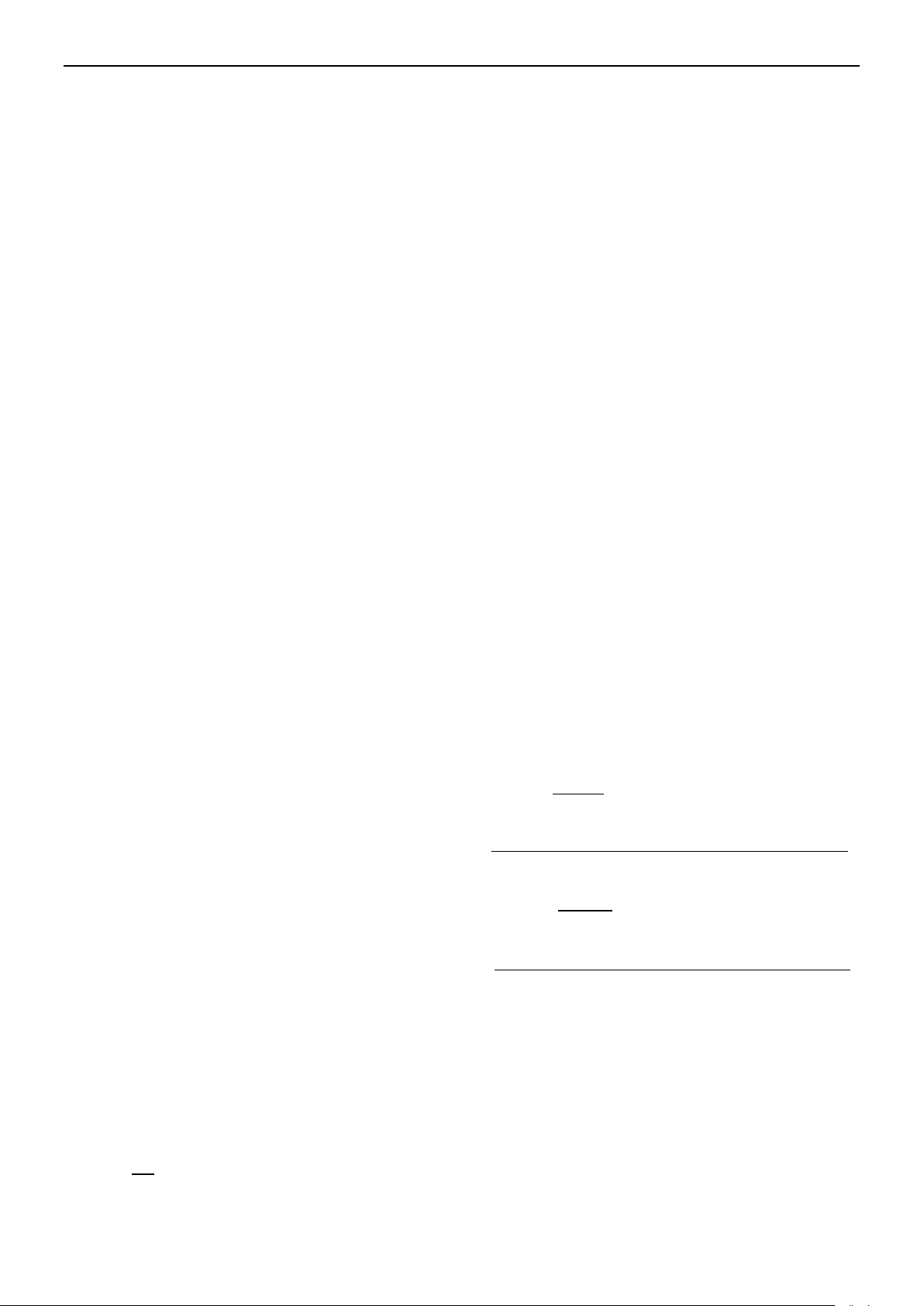

Ở đây: G = [G11 G12; G21 G22] là ma trận

hàm truyền từ đầu vào đến đầu ra;

Gd21 là hàm truyền nhiễu từ d1 đến y2;

R21 và R12 là hai bộ điều khiển cần tính;

Kd21 là hàm truyền bộ bù nhiễu.

Tuyển tập Hội nghị Khoa học thường niên năm 2015. ISBN : 978-604-82-1710-5

149

R21 G21

G11

G22

G12

R12

Kd21 Gd21

d1

u1

u2

y2

y1

-

-

-

+

+

+

W1

W2

Hình 1. Sơ đồ bộ điều khiển PI

chưa tách kênh.

Thiết kế bộ điều khiển PI chưa tách kênh:

Thiết kế bộ PID theo phương pháp tối ưu

độ lớn

21 p21 I21

1

R (s) k .(1 )

T .s

Tính được:

pI

21

1

k .( s)

T 12,146.(s 0,2222)

R (s ) ss

R12 (s) = -6,7843 . ( 1 +

1

1,3201.s

)

Nhận xét: Khi có bộ điều khiển PID thì

đầu ra bám giá trị đặt yêu cầu và sai lệch

tĩnh tiến tới 0. Tuy nhiên đặc tính động học

của hệ thống không tốt ở đầu ra y1 khi có

độ quá điều chỉnh lớn và thời gian xác lập

lâu. Nhược điểm chính của nó là không triệt

tiêu được ảnh hưởng của đầu vào thứ 2 lên

đầu ra thứ 2 (ở thời điểm 20s như kết quả

mô phỏng).

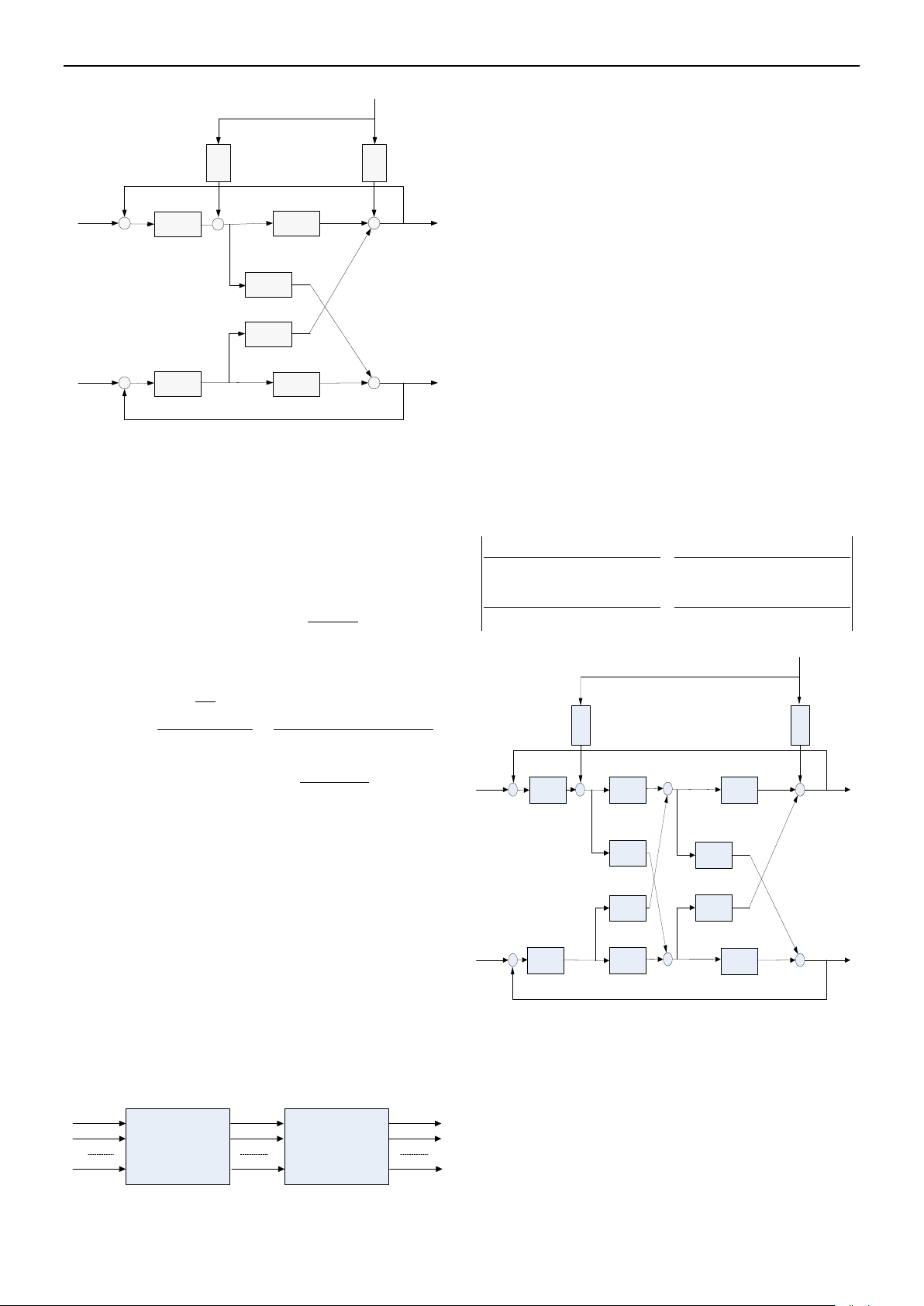

Thiết kế bộ điều khiển PI có tách kênh:

Bộ tách kênh Đối tượng

Hình 2. Sách lược tách kênh

Phương pháp tách kênh toàn phần:

1. Biến đổi G(s) = M(s).N(s)

M là ma trận đường chéo có các phần tử

là phân thức chứa mẫu số chung nhỏ nhất của

từng hàng của G. Nếu G có điểm không nằm

bên phải trục ảo thì điểm không đó phải xuất

hiện trên tử số trong từng phần tử trên đường

chéo chính của M.

N là một ma trận đa thứ, có thể nhân

thêm một phân thức có mẫu số chứa các điểm

không nằm bên phải trục ảo (xuất hiện trên tử

số của M.

2. Nghịch đảo N để nhận được khâu bù D.

Từ các tham số ma trận G(s) ta tính được

ma trận bù D:

D( s )

1.0347 (s+4.832) (s+0.4998) 1.1628 (s-0.8742)

(s+14.74) (s+4.263) (s+0.2222) (s+14.74) (s+4.263) (s+0.2222)

0.90701 (s+10.51) (s+2.988) -1.3265 (s+18.96)

(s+14.74) (s+4.263) (s+0.2222) (s+14.74) (s+4.2

63) (s+0.2222)

D11 G11

G21

G12

G22

D22

Kd11 Gd11

d1

u1

u2

y1

y2

-

-

-

+

+

+

W1

W2

D21

R1

R2

D12

+

+

Hình 3. Sơ đồ bộ điều khiển PI tách kênh.

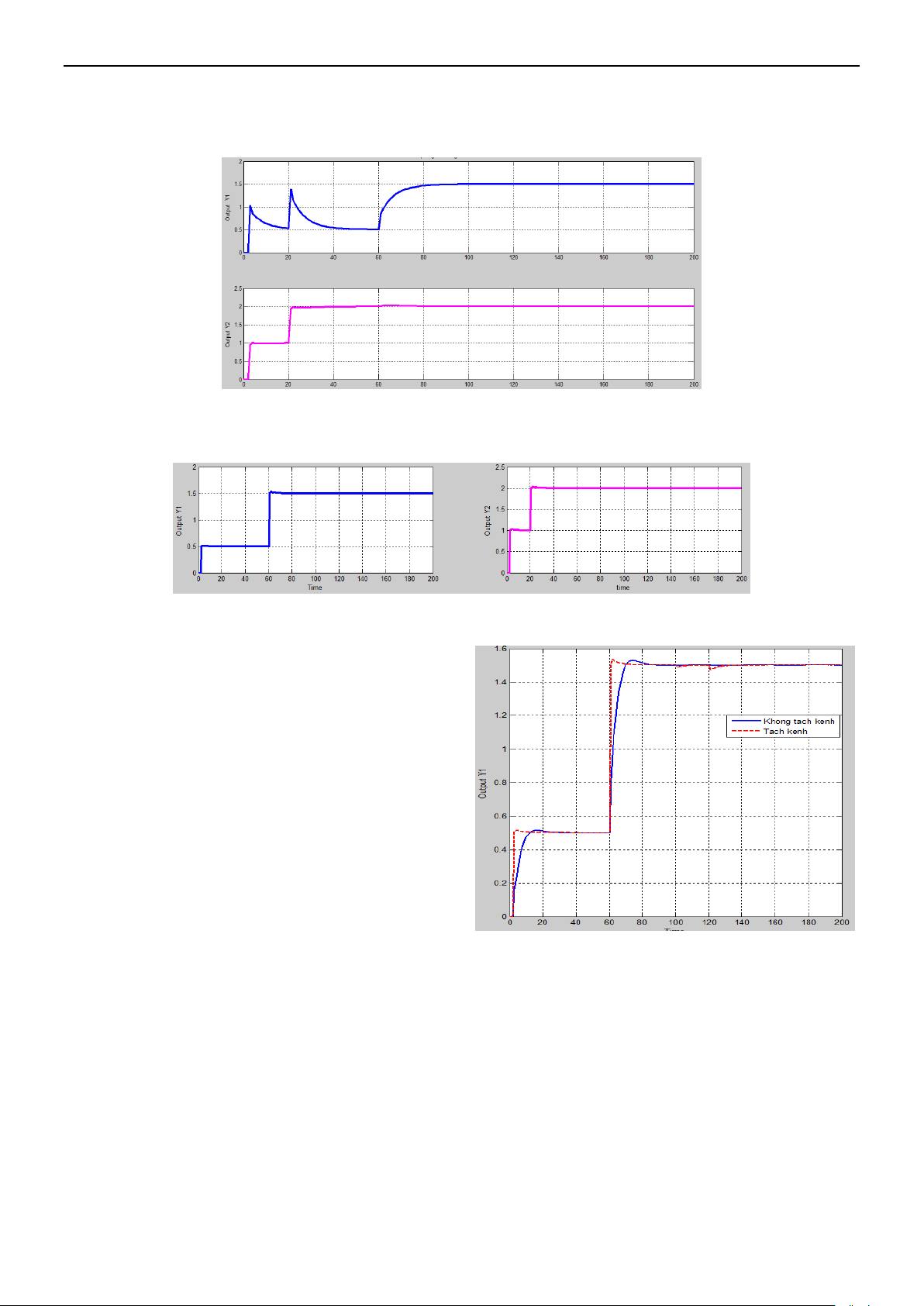

Kết quả mô phỏng:

Để đánh giá kết quả ta sẽ đưa vào tín hiệu

điều khiển u1 và u2 lần lượt các giá trị đặt ở

các thời điểm khác nhau như sau:

r1 = 1 khi t = 2s và r1 = 2 khi t = 20 s

r2 = 0.5 khi t = 2s và r2 = 1.5 khi t = 60 s.

Tuyển tập Hội nghị Khoa học thường niên năm 2015. ISBN : 978-604-82-1710-5

150

Kết quả mô phỏng trường hợp chưa có nhiễu tác động :

Hình 4 : Kết quả mô phỏng đầu ra hệ thống với bộ điều khiển PI

chưa tách kênh, chưa nhiễu

Hình 5: Kết quả mô phỏng đầu ra hệ thống với bộ điều khiển PI có tách kênh, chưa nhiễu

3. SO SÁNH VÀ ĐÁNH GIÁ KẾT QUẢ

Khi chưa xét ảnh hưởng của nhiễu thì với

bộ điều khiển chưa tách kênh có độ quá điều

chỉnh lớn (200% với đầu ra Y1 và thời gian

xác lập lâu đến 40s). Với bộ điều khiển tách

kênh thì độ quá điều chỉnh chỉ 5% và thời

gian xác lập 2s cho Y1.

Khi xét ảnh hưởng của nhiễu ta cũng quan

sát thấy thời gian phản ứng bám giá trị đặt

của bộ tách kênh chỉ là 1s so với 5s của bộ

không tách kênh.

Ưu điểm chính của phương pháp tách kênh

đó là sự thay đổi giá trị đặt của đầu vào này

không tác động đến đầu ra kia.

4. KẾT LUẬN VÀ KIẾN NGHỊ

Với phương pháp tách kênh thì giúp cho

việc tính toán thiết kế bộ điều khiển PI trở

nên đơn giản và dễ dàng hơn. Chất lượng đầu

ra được cải thiện rõ rệt khi giảm độ quá điều

chỉnh đi 40 lần đồng thời giảm thời gian xác

lập đi 5 lần. Bộ điều khiển PI khi có tách

kênh cũng chống nhiễu tốt và mang lại lợi thế

to lớn.

Hình 6: Khi xét ảnh hưởng của nhiễu

của hai bộ PI

5. TÀI LIỆU THAM KHẢO

[1] Hoàng Minh Sơn: Cơ sở hệ thống điều khiển

quá trình, NXB Khoa học và Kỹ thuật, 2006.

[2] Nguyễn Doãn Phước, Phan Xuân Minh: Lý

thuyết điều khiển tuyến tính, NXB Khoa học

và Kỹ thuật, 2003.

[3] Robert H. Bishop: Modern Control System,

Prentice Hall, 2012.

![Đề cương đề tài nghiên cứu khoa học [chuẩn nhất/mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251117/duong297/135x160/26111763433948.jpg)